一种基于FPGA的同态矩阵向量乘计算的加速器

- 国知局

- 2024-08-02 13:52:01

本发明涉及fpga的加速器,特别涉及一种基于fpga的同态矩阵向量乘计算的加速器。

背景技术:

1、在物联网、云服务、边缘计算、人工智能应用程序和其他由下一代网络支持的应用程序中,对数据隐私的担忧正在显著增加。全同态加密系统是指在无需知晓明文和密钥的情况下可以直接对密文进行计算,得到的结果进行解密后,与直接对明文进行计算得到的结果是一致的,因此同态加密被应用于隐私保护等领域。在同态加密系统中,矩阵向量乘是个应用场景很广泛的同态操作,比如逻辑回归等。而由于全同态加密系统具有计算密集型和存储密集型的实现特点,其在cpu或gpu上进行执行性能很差,使得其具有较大的应用限制。fpga具有可再编程性,灵活性和高并行计算的优势,可对其进行加速。

2、而当前针对全同态加密系统的加速器设计主要基于fpga实现加密系统中简单的计算函数,或者是基于定制化电路去实现较为复杂的计算函数,其实际部署难度大,实际应用意义较小。

技术实现思路

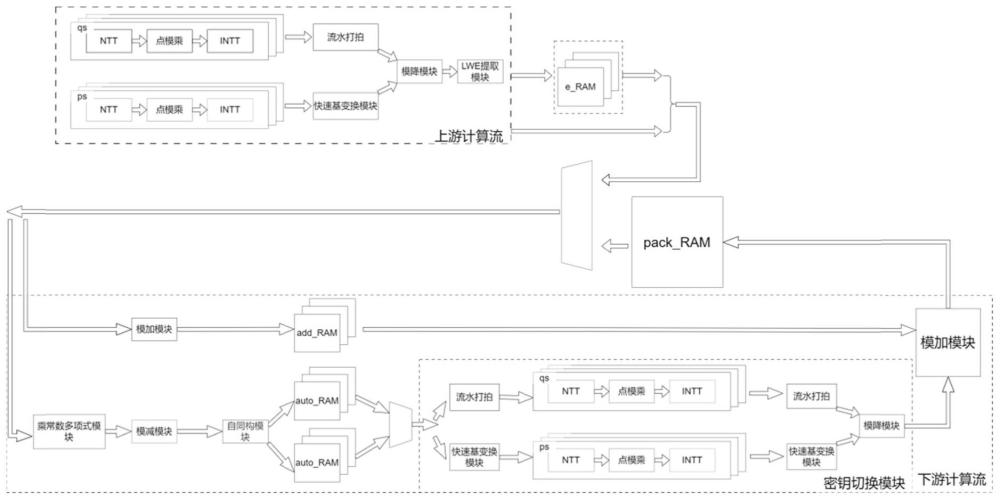

1、为了解决现有技术中存在的中间数据临时存储占用片上存储资源的问题,提出了一种基于fpga的同态矩阵向量乘计算的加速器,采用全流水式的设计架构,降低了中间数据占用的存储资源,有效地提高了系统的运行频率和吞吐量,加速器中各模块支持不同的并行度生成配置,可根据片上资源情况合理配置,最优化系统吞吐量。

2、本发明的技术方案如下:

3、一种基于fpga的同态矩阵向量乘计算的加速器,包括:

4、快速数论变换计算模块、点模乘模块、逆快速数论变换计算模块、快速基变换计算模块、模降模块、lwe提取模块、乘常数多项式模块、自同构计算模块、密钥切换函数模块;

5、各模块之间流式连接,一个模块的输出作为下一模块的输入,形成全流水的系统架构。

6、优选地,上述模块的输入输出均为一个长度为n的密文多项式,在n/ionum个周期内以每周期ionum个数据输入至电路中进行计算/从电路中输出,最终矩阵向量乘计算结果将以密文多项式的形式从模加模块输出。

7、进一步地,快速数论变换计算模块、点模乘模块、逆快速数论变换计算模块三个模块之间完成多项式乘法,快速数论变换计算模块将操作数据做ntt变换,其操作数据以自然序存储于快速数论变换计算模块的内部ram中,以逆序的索引地址从快速数论变换计算模块的内部ram中读出,对于n点的ntt、intt计算,一共有log2n个计算阶段,每个计算阶段都有n/2个蝶式计算。

8、更进一步地,每个计算阶段的蝶式计算上根据不同的并行度配置进行折叠,n/2个蝶式计算在ionum/2个蝶式计算单元上时分复用;

9、其中ionum表示并行度。

10、更进一步地,根据n个点的矩阵、ionum并行度,构建快速数论变换计算模块的网络结构;

11、快速数论变换计算模块的网络结构包括log2n个计算子结构,前log2n/2个计算子结构中蝶式计算单元将数据输入到重连接网络,后log2n/2个计算子结构中重排网络将数据输入至蝶式计算单元;

12、点模乘模块包括若干个模乘模块,快速数论变换计算模块的计算输出结果按逆序排布,输入至点模乘模块,点模乘模块的输出数据逆序输入至逆快速数论变换计算模块;

13、根据n个点的矩阵、ionum并行度,构建逆快速数论变换计算模块的网络结构;

14、逆快速数论变换计算模块的网络结构包括log2n个计算子结构,最初的log2n/4个计算子结构中蝶式计算单元将数据输入到重排网络,最后的log2n/4个计算子结构中重排网络将数据输入至蝶式计算单元;中间log2n/2个计算子结构中蝶式计算单元将数据输入到重连接网络。

15、优选地,快速基变换函数模块包括若干个模乘器、若干个模加器,p类通道全展开经过两级模乘,再进行一级模加,并且模加采取二叉加法树结构。

16、优选地,lwe提取模块包括若干个模减器;

17、lwe提取模块进行近似逐元素计算,即除身份标识为0的元素保持不变之外,其他元素均经过模减器进行计算;输入lwe提取模块的数据是以逆序的组织形式,经过lwe提取模块处理后身份标识的组织形式发生变化:

18、lwe提取模块输出偶行下的操作多项式、奇行下的操作多项式,将偶行下的操作多项式暂存入e_ram中,e_ram中读出的偶行下的操作多项式对调相邻io的输出,再进行输出;奇行下的操作多项式输出到乘常数多项式模块。

19、优选地,乘常数多项式模块中的每个输入数据的处理根据其输入的标识信息不同而不同;

20、对乘常数多项式模块的每个输入io配一个输入身份标识生成模块;并且每个io配一个常数模减器和一个2选1选择器,输入身份标识生成模块的最高位作为选择信号,最高位为1是选择模减器的输出作为输出,为0的是直接输出。

21、优选地,乘常数多项式模块中的每个输入数据的处理根据其输入的标识信息不同而不同;

22、对乘常数多项式模块的每个输入io配一个输入身份标识生成模块;并且每个io配一个常数模减器和一个2选1选择器,输入身份标识生成模块的最高位作为选择信号,最高位为1是选择模减器的输出作为输出,为0的是直接输出。

23、优选地,自同构模块乘常数多项式模块中的每个输入数据的处理根据其输出的标识信息不同而不同;

24、自同构模块的输出是快速数论变换计算模块的输入,而快速数论变换计算模块要求数据逆序输入,因此对自同构输出的数据进行重排;

25、在自同构模块和快速数论变换计算模块之间插入ping-pong-buffer;

26、ping-pong-buffer包括两个bram-bank组,一个bram-bank组由ionum个bram组成;

27、采用如下读写策略选择每个io输出的数据要流向的ram_bank的索引和地址:

28、write_ram_bank_idx=id/(n/ionum)

29、write_ram_addr=id%(n/ionum);

30、ping-pong-buffer输出数据至密钥切换函数模块中。

31、更进一步地,密钥切换函数模块由快速基变换函数模块、快速数论变换计算模块、点模乘模块、逆快速数论变换计算模块、模降模块组成,密钥切换函数模块构成流水式的结构;

32、密钥切换函数模块接收来自ping-pong-buffer的输出数据,快速基变换模块的输出结果输送至快速数论变换计算模块、点模乘模块、逆快速数论变换计算模块中进行计算,计算结果中一部分输出至快速基变换模块,另一部分计算结果进行打拍与快速基变换模块的输出对齐直连至模降模块,模降模块的输出与add_ram的读出数据对齐输入最后的模加模块,使两者相加;当模加后的结果为log2(m)时,以最终密文多项式的形式,作为最终结果输出;当模加后的结果小于log2(m)时,作为中间计算结果存储在pack_ram中;其中,m为矩阵行数。

33、本发明的有益效果:

34、1.通过全流水的系统架构,降低了中间数据占用的存储资源,有效地提高了系统的运行频率和吞吐量,避免输出应用额外的逆序重排网络,减少资源开销。

35、2.各模块支持不同的并行度生成配置,具有灵活性和可扩展性。

本文地址:https://www.jishuxx.com/zhuanli/20240801/240860.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表