一种使用FPGA内嵌DSP资源的包分类方法和装置与流程

- 国知局

- 2024-08-02 14:09:50

本发明涉及网络,特别涉及一种使用fpga内嵌数字信号处理(dsp)资源的包分类方法及装置。

背景技术:

1、包分类是指根据给定的规则库,将数据包分类为特定的流的过程,广泛应用在路由器、安全网关及流量控制系统等各类网络设备中。随着业务感知网络、数据中心网络以及软件定义网络等前沿网络技术的发展,对数据包分类算法性能提出了更高的要求。

2、三态内容寻址存储器(tcam)可以存储除0和1以外的第3种状,并且能在一个时钟周期内完成搜索,因此tcam在高速网络处理中被广泛用于数据包分类处理中。但可编程逻辑阵列(fpga)中通常未内置 tcam 硬核,在采用fpga实现包分类时需要使用fpga资源来实现tcam功能。在fpga上实现tcam功能时通常有三种方案:基于块存储器(bram)的方案、基于分布式存储器(dram)的方案和基于触发器(ff)的方案,但上述方案均需要消耗大量的逻辑资源及存储资源。另一方面,fpga通常内置有dsp模块,而网络包分类过程中很少使用到dsp功能,使用fpga的网络包分类装置又闲置了大量的dsp模块。因此,很有必要发明一种使用fpga内嵌dsp资源的包分类方法和装置。

技术实现思路

1、针对现有技术存在的不足,本发明提供一种使用fpga内嵌dsp资源的包分类方法和装置。

2、为了解决现有技术问题,本发明第一方面提供了使用fpga内嵌dsp资源的包分类方法,所述方法包括:

3、1、设置dsp模块的乘法运算、逻辑运算及模板匹配功能

4、dsp模块包含乘法器、逻辑运算及模板匹配三个功能模块,将乘法器两个输入端设置为拼接功能实现更宽数据的输入,同时绕过乘法器模块。将所述绕过乘法器后拼接的数据输入至逻辑运算单元,并将逻辑运算单元设置为位运算。将所述位运算的输出数据输入至模块匹配功能,并允许模块匹配功能。

5、2、设置模板及数据输入路径实现分类规则集的精确匹配查找

6、基于所述设置dsp模块的乘法运算、逻辑运算及模板匹配功能,设置逻辑运算单元为同或运算,设置逻辑运算的另一输入端为端口输入,并将匹配模板所有位设置为1。

7、3、将dsp模块级联以实现分类规则集的模糊匹配查找

8、 基于所述设置dsp模块的逻辑运算及模板匹配功能,将两个dsp模块级联,其中,第二dsp模块的输出引入到第一dsp的进位链输入端。设置第一dsp逻辑运算为同或运算,并将逻辑运算的另一输入端设置为进位链输入,将模板运算模块的模板输入设置为端口输入。设置第二dsp的逻辑输入为或运算,并将逻辑运算结果设置到进位输出端。

9、4、通过多模块并联实现不同宽度分类规则的匹配查找

10、基于所述将dsp模块级联以实现分类规则集的模糊匹配查找,将多个模块并联,所述并联模块具有相同的设置。将所述并联模块的输出结果输入到多模块匹配结果运算模块。将所述多路并联模块及多路匹配结果运算模块记为一个基于dsp模块的包分类单元。

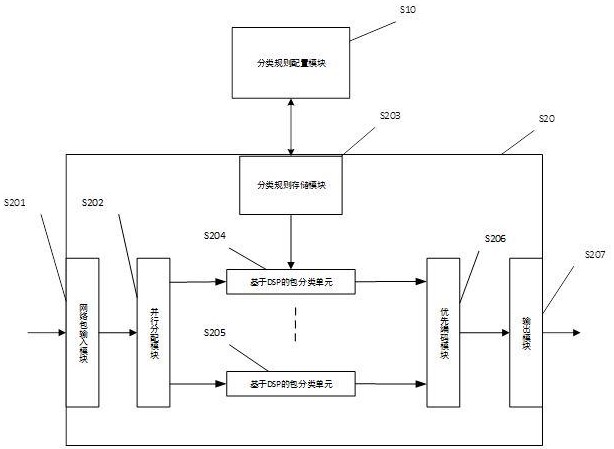

11、5、数据包多路并行匹配运算

12、基于所述dsp模块的包分类单元,将每一个分类规则对应一个包分类单元,则当有多个分类规则时,对输入数据包分类有多个包分类单元在并行运算。

13、6、将待分类数据包并行输入至基于dsp模块的包分类单元

14、基于所述数据包多路并行匹配运算方法,每一条分类规则对应一个包分类单元,并将分类规则输入至相应包分类单元的输入端,待分类数据包同时输入至所有包分类单元的相应输入端口。

15、7、对多路包分类单元的分类结果进行优先编码

16、基于所述数据包多路并行匹配运算,每一个包分类单元输出一个匹配结果,则共有多个包分类单元的匹配结果,将所有包分类单元的匹配结果输入至编码模块。将第1个包分类单元的地址记为0,第n个包分类单元的地址记为n-1,编码模块输出包分类单元匹配结果为命中的分类单元地址。所述编码模块支持低地址优先编码及高地址优先编码,当命中多条分类规则时,编码模块输出最高地址的分类规则地址或者最低地址的分类规则地址。

17、所述分类规则编码模块支持多级流水线结构,在分类规则数量较多时,将一定数量的包分类单元构成一个组,每个组由一个分类编码模块对该组分类结果进行编码,后级分类编码模块对上一级多组的分类结果进行编码。

18、本发明第二方面提供了一种使用所述dsp资源进行包分类方法的装置,所述装置主要包括分类规则配置模块及包分类执行模块。

19、分类规则配置模块,用于对分类规则排序及按照分类规则的顺序进行编码,并将编码后的所有分类规则配置到执行模块。

20、执行模块,用于执行所配置的分类规则匹配运算,输出命中或未命中分类规则集,当命中配置的分类规则时同时输出被命中分类规则的地址编码,执行模块主要包括:

21、网络数据包接收模块,用于接收待分类网络数据包;

22、并行分配模块,将接收到的网络数据包及所有分类规则输入到相应的基于dsp的包分类单元;

23、基于dsp的包分类单元,基于所述采用dsp模块的包分类方法完成一条分类规则的匹配运算,包分类单元的匹配运算结果为命中或者未命中;

24、优先编码模块,用于对多路包分类单元的匹配结果进行编码;

25、输出模块,输出包分类结果,命中及命中分类规则的地址编码或者未命中。

26、有益效果:本发明采用fpga内嵌dsp资源对数据包进行分类,充分利用了fpga资源,可有效节省fpga的逻辑资源及存储资源;本发明方法将多个dsp模块级联实现了多输入数据的匹配查找,可实现数据包分类过程中的精确匹配查找及模糊匹配查找;本发明方法支持级联模块的并行运算,通过将级联模块并联,可支持不同宽度、不同深度的分类规则;同时,本发明采用了流水线结构,每一个时钟周期可完成一个网络数据包的分类,进而本发明具有较高的分类速度,可满足100gbps网络的数据包分类要求。

技术特征:1.一种使用fpga内嵌dsp资源的包分类方法,其特征在于,所述方法包括:

2.根据权利要求1所述设置dsp模块的乘法运算、逻辑运算就及模板匹配功能,其特征在于,将乘法器的输入数据拼接为更宽的数据后输出至下一级,并绕过dsp模块的乘法器,将逻辑运算单元设置为按位同或运算,启用模板匹配功能并将模板的全部位数设置为1。

3.根据权利要求1所述将dsp模块级联以实现分类规则集的模糊匹配查找,其特征在于,根据权利要求2设置第一dsp模块,并将第二dsp输出结果输入至第一dsp进位链输入端。

4.根据权利要求3所述第二dsp模块,其特征在于,将乘法器的输入数据拼接为更宽的数据后输出至下一级,并绕过dsp模块的乘法器,将逻辑运算单元设置为位或运算,不启用模板匹配功能。

5.根据权利要求1所述通过多模块并联实现不同宽度分类规则的匹配查找,其特征在于,所并联模块是根据权利要求3及权利要求4所述设置的,需要并联模块的个数结合分类规则宽度及单个dsp模块宽度选取的。

6.根据权利要求1所述对多路包分类单元的分类结果进行优先编码,其特征在于,编码模块采用高地址优先编码或者低地址优先编码。

7.一种使用fpga内嵌dsp资源的包分类方法的装置,其特征在于,所述装置包括分类规则配置模块和分类规则执行模块。

8.根据权利要求7所述的分类规则配置模块,其特征在于,所述配置模块用于对分类规则排序及按照分类规则的顺序进行编码,并将编码后的所有分类规则配置到执行模块。

9.根据权利要求7所述分类规则执行模块,其特征在于,执行模块用于执行所配置的分类规则匹配运算,输出命中或未命中分类规则集,当命中配置的分类规则时同时输出被命中分类规则的地址编码,执行模块主要包括:

技术总结本发明涉及网络技术领域,特别涉及网络包分类方法,本发明提供了一种使用FPGA内嵌DSP资源的包分类方法和装置。本发明使用FPGA内嵌DSP资源对数据包进行分类,充分利用了FPGA资源,可有效节省FPGA的逻辑资源及存储资源;本发明方法将多个DSP模块级联实现了多输入数据的匹配查找,可实现数据包分类过程中的精确匹配查找及模糊匹配查找;本发明方法支持级联模块的并行运算,通过将级联模块并联,可支持不同宽度、不同深度的分类规则集;同时,本发明采用了流水线结构,每一个时钟周期可完成一个网络数据包的分类,进而本发明具有较高的分类速度,可满足100Gbps网络的数据包分类要求。技术研发人员:吴磊,郑重,马文东受保护的技术使用者:北京天御云安科技有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/241814.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。