一种新型静态隐匿的DFF-PUF复合电路

- 国知局

- 2024-08-02 14:22:42

本发明涉及电路设计和硬件安全,具体为一种新型静态隐匿的dff-puf复合电路。

背景技术:

1、随着现代技术的不断进步,以往针对信息安全所提出的各种数据保密措施也面临着巨大的漏洞,会对目前的芯片造成巨大的威胁。各人的敏感信息通常存储在芯片中,然而目前市面上流行的数据加密方案往往是以软件或者算法为基础,存储芯片为载体。如今,半导体微观探测工具的出现将改变目前的防护体系。攻击者可以绕过这些保护手段,通过攻击硬件本身,利用物理探测工具找到存储芯片中的根密钥。因此,硬件防护的需求在不断增加。物理不可克隆函数puf是一种基于物理特性的硬件构造,用于生成一个独特的标识或密钥。puf利用芯片器件中存在的微小差异,例如晶体管阈值电压、电流漏失等,来产生具有随机性和不可预测性的输出。这些差异是器件制造过程的自然变化所导致的,因此每个芯片都会有其特有的puf。

2、实际上,即便puf电路具有类似“指纹”的优势,它也会相应具备一些缺点。puf电路一般会具备明显的布局以及物理特征,某些puf会具有高度对称性。物理攻击对puf电路具有极强危害性的根源在于,芯片制造完成后puf电路相当于静态的“活靶子”,攻击者通过puf电路的结构或者布局特征,可以轻易地对其进行定位并采取针对性的物理攻击,进而直接获取关键数据或间接控制芯片。

3、经过检索,中国发明公开号cn117454448b提出了一种静态隐匿的dff-puf复合电路,将puf电路隐匿在混乱无序的数字后端版图中,使攻击者从图像上难以定位到具体的密钥信息单元,实现静态隐匿。然而,该puf存在可靠性不足的缺点。可靠性是puf电路的一个重要特性,一个puf电路在不同的环境下,例如在温度变化、电源电压波动、噪声毛刺的作用下,相同的激励下能否产生同样的响应,故提出一种新型静态隐匿的dff-puf复合电路以解决上述问题。

技术实现思路

1、针对现有技术的不足,本发明提供了一种新型静态隐匿的dff-puf复合电路,具备可靠性好等优点,解决了静态隐匿的dff-puf复合电路可靠性不佳的问题。

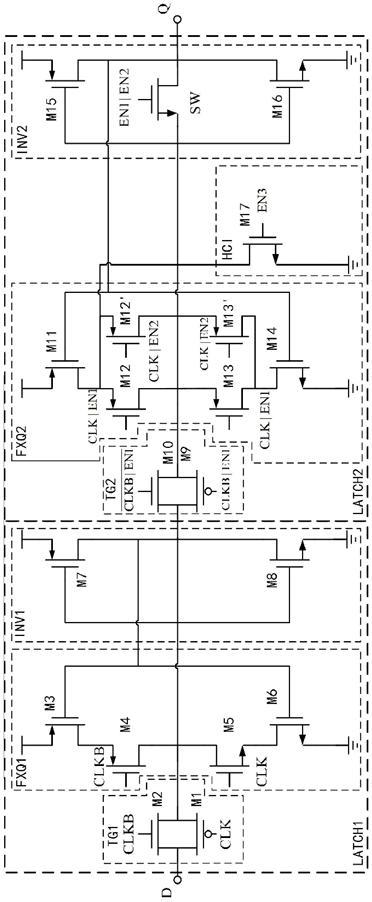

2、为实现上述目的,本发明提供如下技术方案:一种新型静态隐匿的dff-puf复合电路,包括输入端口d、第一锁存器latch1、第二锁存器latch2、使能开关sw和输出端口q,所述第一锁存器latch1包括第一传送门tg1、第一反相器fxq1和第一非门inv1,所述输入端口d与第一传送门tg1的输入端电性连接,所述第一传送门tg1的输出端分别与第一反相器fxq1的输出端和第一非门inv1的输入端电性连接,所述第二锁存器latch2包括第二传送门tg2、第二反相器fxq2、热载流子注入hci和第二非门inv2,所述第一反相器fxq1的输入端和第一非门inv1的输出端均与第二传送门tg2的输入端电性连接,所述第二传送门tg2的输出端分别与第二反相器fxq2的输出端和第二非门inv2的输入端电性连接,所述第二反相器fxq2的输出端与热载流子注入hci的输入端电性连接,所述第二反相器fxq2的输入端和第二非门inv2的输出端及使能开关sw的漏极均与输出端口q电性连接;

3、所述输入端口d用于输入信号,所述用于第一锁存器latch1用于对输入的信号进行传输或存储,所述第二锁存器latch2用于对第一锁存器latch1输出的信号进行传输或存储,所述第一传送门tg1用于对输入的信号进行传输,所述第二传送门tg2用于对第一锁存器latch1输出的信号进行传输,所述第一反相器fxq1和第二反相器fxq2均用于对输入的信号进行输出翻转或存储,所述第一非门inv1和第二非门inv2均用于对输入的信号进行翻转,所述使能开关sw用于控制第二传送门tg2、第二反相器fxq2的通断以及第二非门inv2是否短接,所述hci用于控制第二反相器fxq2进行阈值电压调整。

4、进一步,第一控制时钟信号clk分别连接在第一传送门tg1的第一输入控制信号端、第一反相器fxq1的第一输入控制信号端、第二反相器fxq2的第一输入控制信号端、第二反相器fxq2的第二输入控制信号端、第二反相器fxq2的第三输入控制信号端和第二反相器fxq2的第四输入控制信号端,第二控制时钟信号clkb分别连接在第一传送门tg1的第二输入控制信号端、第一反相器fxq1的第二输入控制信号端、第二传送门tg2的第一输入控制信号端和第二传送门tg2的第二输入控制信号端,第一控制时钟信号clk和第二控制时钟信号clkb为反向信号,使能开关sw产生的使能开关信号en1分别连接在第二传送门tg2的第一输入控制信号端、第二传送门tg2的第二输入控制信号端、第二反相器fxq2的第一输入控制信号端和第二反相器fxq2的第二输入控制信号端,使能开关sw产生的使能开关信号en2分别连接在第二反相器fxq2的第三输入控制信号端和第二反相器fxq2的第四输入控制信号端,使能开关信号en3连接在热载流子注入hci的输入控制信号端;

5、具体包括以下四种运行状态:

6、dff状态:当使能开关信号en1和使能开关信号en2均为低电平0时,此时复合电路工作处于触发器状态,当第一控制时钟信号clk为低电平0时,第一传送门tg1导通,此时输入信号通过输入端口d和第一传送门tg1传输进第一反相器fxq1中,并通过第一非门inv1进行翻转,当第二控制时钟信号clkb为高电平1时,第二传送门tg2截止,使得第一非门inv1的输出信号存储在第一反相器fxq1中而不会进入第二传送门tg2中,当第一控制时钟信号clk为高电平1时,第一传送门tg1截止,此时输入信号不再进入第一传送门tg1中,使得第一非门inv1的输出信号保持之前状态不变,当第二控制时钟信号clkb为低电平0时,第二传送门tg2导通,将之前锁存在第一非门inv1的输出信号传输进第二传送门tg2中,然后进入第二非门inv2并通过输出端向外输出,实现输出信号等于输入信号;

7、puf密钥生成状态:当使能开关信号en1为高电平1时,此时复合电路处于密钥生成的准备状态,第一传送门tg1、第一反相器fxq1和第一非门inv1仍然根据第一控制时钟信号clk对输入信号进行传输或存储,而第二非门inv2的输入端和输出端短接,且第二反相器fxq2截止,此时令第二非门inv2的输入电压为vm,第二非门inv2的输出电压为vout,则第二反相器fxq2的输出端与第二非门inv2的输入端连接处的电压与第二非门inv2输出的电压均维持在vm,当使能开关信号en1和第一控制时钟信号clk均为低电平0时,由于第二非门inv2的输出翻转阈值vdecision等于vm,第二传送门tg2、第二反相器fxq2和第二非门inv2将整体维持在亚稳态,根据第二反相器fxq2驱动强度不匹配引起电流失衡,使得电压vm与vdecision产生偏离电压δv,偏离电压δv进一步被第二非门inv2构成的灵敏放大器放大并锁存,实现数字密钥0或1的转换;

8、puf密钥可靠性增强状态:当使能开关信号en1和使能开关信号en2均为高电平1时,此时复合电路处于密钥生成的准备状态,第一传送门tg1、第一反相器fxq1和第一非门inv1仍然根据第一控制时钟信号clk对输入信号进行传输或存储,而第二非门inv2的输入端和输出端短接,且第二反相器fxq2截止,此时令第二非门inv2的输入电压为vm,第二非门inv2的输出电压为vout,则第二反相器fxq2的输出端与第二非门inv2的输入端连接处的电压与第二非门inv2输出的电压均维持在vm,当使能开关信号en1、使能开关信号en2和第一控制时钟信号clk均为低电平0时,由于第二非门inv2的输出翻转阈值vdecision等于vm,第二传送门tg2、第二反相器fxq2和第二非门inv2将整体维持在亚稳态,根据第二反相器fxq2驱动强度不匹配引起电流失衡,使得电压vm与vdecision产生偏离电压δv,偏离电压δv进一步被第二非门inv2构成的灵敏放大器放大并锁存,实现数字密钥0或1的转换;

9、hci状态:当使能开关信号en1、使能开关信号en2、使能开关信号en3和第一锁存器latch1输出均为高电平1时,热载流子注入hci将第二反相器fxq2的漏极电压置为低电平0,此时将电源电压变为2vdd,可以改变第二反相器fxq2的阈值电压,实现人为调节失配源的目的。

10、进一步,所述第一传送门tg1包括第一前端开关m1和第二前端开关m2,所述输入端口d与第一前端开关m1的源极、第二前端开关m2的源极电性连接,所述第一前端开关m1的漏极、第二前端开关m2的漏极与第一反相器fxq1的输出端和第一非门inv1的输入端电性连接。

11、进一步,所述第一反相器fxq1包括第一中端开关m3、第二中端开关m4、第三中端开关m5和第四中端开关m6,所述第二中端开关m4的漏极和第三中端开关m5的漏极均与第一前端开关m1的漏极和第二前端开关m2的漏极电性连接,所述第二中端开关m4的源极与第一中端开关m3的漏极电性连接,所述第三中端开关m5的源极与第四中端开关m6的漏极电性连接,所述第一中端开关m3的栅极、第四中端开关m6的栅极和第一非门inv1的输出端均与第二传送门tg2的输入端电性连接。

12、进一步,所述第一非门inv1包括第一后端开关m7和第二后端开关m8,所述第一后端开关m7的栅极和第二后端开关m8的栅极均与第二中端开关m4的漏极和第三中端开关m5的漏极电性连接,所述第一后端开关m7的漏极和第二后端开关m8的漏极、第一中端开关m3的栅极、第四中端开关m6的栅极均与第二传送门tg2的输入端电性连接。

13、进一步,所述第二传送门tg2包括第三前端开关m9和第四前端开关m10,所述第三前端开关m9的源极、第四前端开关m10的源极与第一后端开关m7的漏极、第二后端开关m8的漏极电性连接,所述第三前端开关m9的漏极、第四前端开关m10的漏极与第二反相器fxq2的输出端和第二非门inv2的输入端电性连接。

14、进一步,所述第二反相器fxq2包括第五中端开关m11、第六中端开关m12、第六中端开关m12’、第七中端开关m13、第七中端开关m13’和第八中端开关m14,所述第六中端开关m12的漏极和第六中端开关m12’的漏极以及第七中端开关m13的源极和第七中端开关m13’的源极与第三前端开关m9的漏极和第四前端开关m10的漏极电性连接,所述第六中端开关m12的源极和第六中端开关m12’的源极与第五中端开关m11的漏极电性连接,所述第七中端开关m13的漏极和第七中端开关m13’的漏极与第八中端开关m14的漏极电性连接,所述第五中端开关m11的栅极和第八中端开关m14的栅极均与第二非门inv2的输出端和输出端口q电性连接。

15、进一步,所述第二非门inv2包括第三后端开关m15和第四后端开关m16,所述第三后端开关m15的栅极、第四后端开关m16的栅极和使能开关sw的源极均与第六中端开关m12、第六中端开关m12’的漏极和第七中端开关m13、第七中端开关m13’的源极电性连接,所述第五中端开关m11的栅极、第八中端开关m14的栅极、第三后端开关m15的漏极、第四后端开关m16的漏极、使能开关sw的漏极均与输出端口q电性连接。

16、进一步,所述热载流子注入hci包括第九中端开关m17,所述第九中端开关m17漏极与第五中端开关m11的漏极电性连接。

17、进一步,所述第一前端开关m1、第一中端开关m3、第二中端开关m4、第一后端开关m7、第三前端开关m9、第五中端开关m11、第六中端开关m12、第六中端开关m12’、第七中端开关m13、第七中端开关m13’和第三后端开关m15均为pmos管,所述第二前端开关m2、第三中端开关m5、第四中端开关m6、第二后端开关m8、第四前端开关m10、第八中端开关m14和第四后端开关m16、第九中端开关m17和使能开关sw均为nmos管,第一控制时钟信号clk分别连接在第一前端开关m1的栅极、第三中端开关m5的栅极、第六中端开关m12的栅极和第七中端开关m13的栅极,第二控制时钟信号clkb分别连接在第二前端开关m2的栅极、第二中端开关m4的栅极、第三前端开关m9的栅极和第四前端开关m10的栅极,使能开关sw产生的使能开关信号en1分别连接在第三前端开关m9的栅极、第四前端开关m10的栅极、第六中端开关m12的栅极、第六中端开关m12’的栅极、第七中端开关m13的栅极和第七中端开关m13’的栅极,使能开关sw产生的使能开关信号en2分别连接第六中端开关m12’的栅极和第七中端开关m13’的栅极,使能开关信号en3连接在第九中端开关m17的栅极,第一中端开关m3的源极、第一后端开关m7的源极、第五中端开关m11的源极和第三后端开关m15的源极均与电源电性连接,第四中端开关m6的源极、第二后端开关m8的源极、第八中端开关m14的源极和第四后端开关m16的源极和第九中端开关m17的源极均接地。

18、与现有技术相比,本技术的技术方案具备以下有益效果:

19、1、该新型静态隐匿的dff-puf复合电路,无需辅助数据和不具有明显物理修调特征的失配源自检测电路,筛选高稳定性响应的dff-puf作为密钥单元;

20、2、该新型静态隐匿的dff-puf复合电路,针对芯片生产后,其密钥可靠性可能不具备理论分析那么完备,因此在确定具有高稳定性响应的密钥单元后,可采用热载流子注入修调方法人为增加失配源之间的差异,进一步提高密钥单元对环境干扰的鲁棒性或者消除不稳定密钥;

21、3、该新型静态隐匿的dff-puf复合电路,在原有主体puf电路的基础上仅增加了两个mos管,相较于传统的经过系统算法去增强电路可靠性,极大的降低了硬件开销。

本文地址:https://www.jishuxx.com/zhuanli/20240801/242614.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表