一种基于软硬件协同的时间同步的实现方法

- 国知局

- 2024-08-02 14:54:06

本发明涉及软硬件协同的,具体而言,涉及一种基于软硬件协同的时间同步的实现方法。

背景技术:

1、随着集成电路工业设计技术和半导体制造技术的进步,系统验证难度和成本投入逐渐增加。纯软件模拟器可配置性高,能够以较低的成本进行修改和维护,但其缺点在于仿真过程耗时较长。基于fpga的硬件仿真器虽然可以快速模拟实际硬件的运行情况,然而每次对设计进行修改后,都需要耗费大量时间进行综合、布局布线等工作,并重新加载到fpga仿真器上进行验证。为了克服传统仿真器(硬件仿真器或软件模拟器)的缺点,基于软件控制、硬件协同加速的思想设计一种软硬件协同仿真器。

2、针对如何协同软硬件协同仿真器软件模块(上位机)与硬件模块(下位机)的工作,使上下位机能在时间上保持同步成为该研究的核心问题。软件和硬件之间需要建立可靠的通信机制,确保数据的统一性和协同性。时间标记是一种常用的软硬件协同时间同步的实现方法,软件和硬件模块之间通过时间标记的方式可以准确地标记事件发生的时间点或者数据产生的时间,从而在硬件模块和软件模块之间建立起统一的时间参考,在仿真器中,任务的计算由下位机实现,上位机主要负责任务的通信。然而,如果上位机不考虑或估算任务的计算时间,仅按照任务的到达顺序来确定任务间的通讯时间,可能会带来一些问题,任务的执行时间具有先后次序的要求,任务在上位机通信子系统的注入时间如果不准确,会对仿真器的性能产生影响。

技术实现思路

1、本发明的目的在于:提供一种采用时间标记的方式在上位机(软件)和下位机(硬件)之间建立起统一的时间参考的方法,以提升软硬件之间协同的可靠性和正确性。

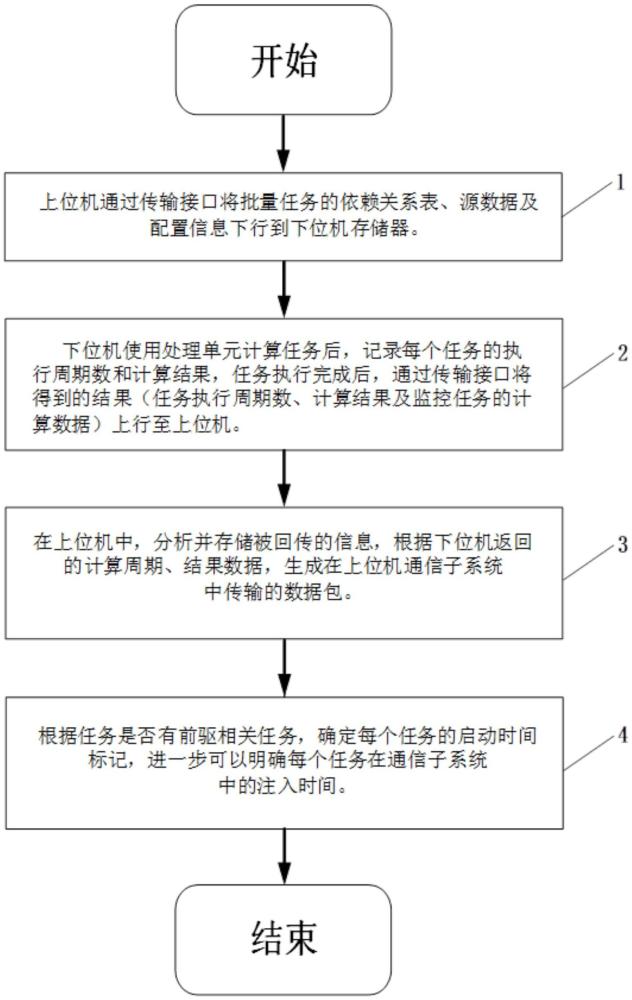

2、本发明的技术方案是:提供了一种基于软硬件协同的时间同步的实现方法,该方法包括:

3、s1、上位机通过传输接口将批量任务的依赖关系表、源数据及配置信息下行到下位机的存储器,依赖关系表包括任务核心信息段以及任务通信段;

4、s2、下位机使用pe计算任务后,记录每个任务的执行周期数和计算结果,任务执行完成后,通过传输接口将得到的结果上行至上位机,得到的结果包括任务执行周期数、计算结果及监控任务的计算数据;

5、下位机由ddr存储器、主控制器、任务读取单元、发射单元、pe、pe状态检测单元和数据结果处理单元组成;

6、上位机下行的批量任务的依赖关系表、源数据及配置信息存储在ddr存储器中,主控制器命令任务读取单元从ddr存储器中读取批量任务的数据,将配置信息以及依赖关系表中的任务标签整理为队列,主控制器读取一个任务标签后,命令任务读取单元将该任务的配置信息发送至发射单元;

7、发射单元将任务发射至处于空闲状态的pe进行计算,pe状态检测单元实时检测pe是否处于空闲状态,若不处于空闲状态则记录pe当前执行任务的编号,pe状态检测单元将收集整理的信息同步至主控制器;

8、同时,在pe加载任务配置后,与pe连接的周期计数模块启动并开始对任务计算过程的周期进行计数,任务计算完成后周期计数模块停止计数,得到该任务执行的总周期数;

9、数据结果处理单元接收pe计算完成任务的任务编号和该任务的总周期数,数据结果处理单元接收pe计算完成任务的计算结果,两者均封装写入ddr存储器;

10、ddr存储器中设有寄存器,每当ddr存储器被写入一个任务的计算结果,寄存器值加1,直到寄存器值与上位机分配的任务数量相等后,ddr存储器将储存的所有内容上行至上位机;

11、s3、上位机存储ddr存储器上行的内容并进行分析,读取所有任务的计算周期和计算结果,将计算周期转化为计算耗时,生成在上位机通信子系统中传输的数据包,以便在上位机通信子系统中能够方便、有序地发送,数据包包含所有任务的依赖关系表、计算耗时、计算结果;

12、s4、对任务进行时间同步,根据任务是否有前驱相关任务,确定每个任务的启动时间标记,根据启动时间进一步明确每个任务在上位机的通信子系统中的注入时间;若当前任务的注入时间与上位机全局时间相等时,就进行注入到通信子系统的操作;如果不相等,则需要等待下一个时间周期再次检查是否注入。

13、上述任一项技术方案中,进一步地,上位机在执行任务前,首先检查所有任务是否都已经执行完成;

14、若所有任务都已经执行完成,整个系统就会停止运行;若还有未完成的任务,上位机将批量任务的依赖关系表、源数据及配置信息下行到下位机;等待下位机发出任务计算完成信号后,上位机接收下位机返回的任务结果进行处理,任务结果包括任务执行周期数、计算结果及监控任务的计算数据;上位机对返回的任务结果处理完毕后更新任务列表,检查所有任务是否都已执行完成,重复上述循环。

15、上述任一项技术方案中,进一步地,步骤s4的具体计算过程如下:

16、首先根据任务依赖关系表的入度判断该任务是否有前驱任务,如果一个任务的入度为0,表示没有前驱任务,该任务启动时间标记为0;

17、如果一个任务的入度不为0,意味着该任务具有前驱任务,该任务的启动时间将是其所有前驱任务计算时间与传输时间之和的最大值;任务启动时间标记具体的计算过程如下:

18、设定当前任务x的计算耗时为cx、传输耗时为dx、启动时间为sx;其中计算耗时cx为任务的计算周期乘每周期的单位耗时,在下位机中每个计算周期消耗时间一致,传输耗时dx根据任务计算过程中的路径得出,不同路径具有各自固定的传输耗时;

19、任务可能会有多个前驱任务,当前任务x的前驱任务集合为{pn},pn表示当前任务的第n个前驱任务,n的范围是1到该任务的入度值;前驱任务的计算耗时为cn、传输耗时为dn,启动时间为sn;任务x的启动时间为sx=max{cn+dn+sn};

20、获得当前任务的启动时间后,可以计算出该任务的注入时间,注入时间为启动时间与计算耗时之和,当前任务x的注入时间为sx+cx。

21、上述任一项技术方案中,进一步地,主控制器除了负责控制的主控单元外还包括:任务写回单元、任务唤醒单元和任务缓存单元;

22、任务写回单元负责将计算结束的任务的计算结果进行管理,管理流程包括:每个pe连接在不同的节点上,对只有一个后继任务的单输出任务,若存在空闲节点则将该任务的结果数据写入空闲节点,否则将任务结果写回ddr存储器;对具有多个后继任务的多输出任务,任务写回单元遍历任务队列寻找该任务的后继任务,若后继任务以通过发射单元发射至pe,将该任务的结果数据写入后继任务所在pe的节点,若后继任务均未发射,则将结果数据写回ddr存储器;

23、任务缓存单元存储常用的任务数据的访存结构,采用寄存器作为存储单元,优化下位机的性能;通过这一机制,主控制器能在单周期内快速访问这些信息,增强下位机的发射效率;当有任务被发射,为发射的任务及其后继任务分配寄存器组来保存相应的任务信息;

24、当任务所需pe进入空闲,也就是前一任务完成写回后,任务唤醒单元从任务缓存单元中读取该任务并发送至发射单元,对于具有多个前驱任务的多输入任务,需要确保所有前驱任务均已完成写回再发射。

25、本发明的有益效果是:

26、本发明中的技术方案通过上位机将批量任务的依赖关系表、源数据及配置信息下行至下位机,下位机通过pe计算任务时记录任务执行周期数和传输周期数并随任务结果一同上行回上位机,上位机以此来确定任务的启动时间,从而实现软硬件时间同步,确保软硬件系统在相同的时间基准下工作,提高仿真器的可靠性,保证了仿真的精确性;下位机通过pe状态检测单元实时监控各pe的空闲状态以及正在处理任务的依赖关系,对批量任务的计算路径进行管理,提高下位机的计算效率。

本文地址:https://www.jishuxx.com/zhuanli/20240801/244257.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表