一种基于复数混频器可调超低相位噪声取样锁相电路的制作方法

- 国知局

- 2024-08-02 15:04:03

本发明涉及频率合成领域,尤其涉及一种基于复数混频器可调超低相位噪声取样锁相电路。

背景技术:

1、频率合成器是电子技术、空间技术和通信技术中的一个重要组成部分。作为时基信号以及本地振荡器在通信、雷达、电子对抗、仪器仪表等领域有着广泛的应用。在目前的电子技术应用中都会对本振源相位噪声有较高的要求,越低的相位噪声代表能提供给整机系统更好的性能。取样介质锁相振荡器因为其超低的相位噪声性能,在低相位噪声频率合成器方案中占据了重要的地位,传统的取样锁相属于纯模拟锁相结构,没有数字电路仅仅能产生固定点频输出,无法实现细步进可调,应用有一定的局限性,传统结构如图1所示。

2、如图1所示传统的取样锁相环是基于阶跃二极管构成的模拟鉴相器2实现锁相,介质振荡器4通常带宽很窄,没有分频器,仅仅能实现一个已知确定的输出频率f1=n*fref,其中n是根据需求确定的具体的一个值,一旦设计便无法可变,不能实现细步进。

3、其次传统的混频器方案,混频后必须有滤波器以滤除镜频以及其他杂散信号及如图2所示,传统混频器的输出为rf=m*lo±n*if(m,n=0、1、2、……),存在一系列的杂信号,其中最严重的是本振泄露lo、以及镜频信号,必须增加滤波器以滤除相关杂散,该方法中由于中频dds输出频率很低,本振泄露和镜频信号距离需要的有用信号都很近,因此对滤波器抑制要求非常高,使得滤波器实现将非常困难,甚至无法实现。

4、因此,本发明提出一种基于复数混频器可调超低相位噪声取样锁相电路。

技术实现思路

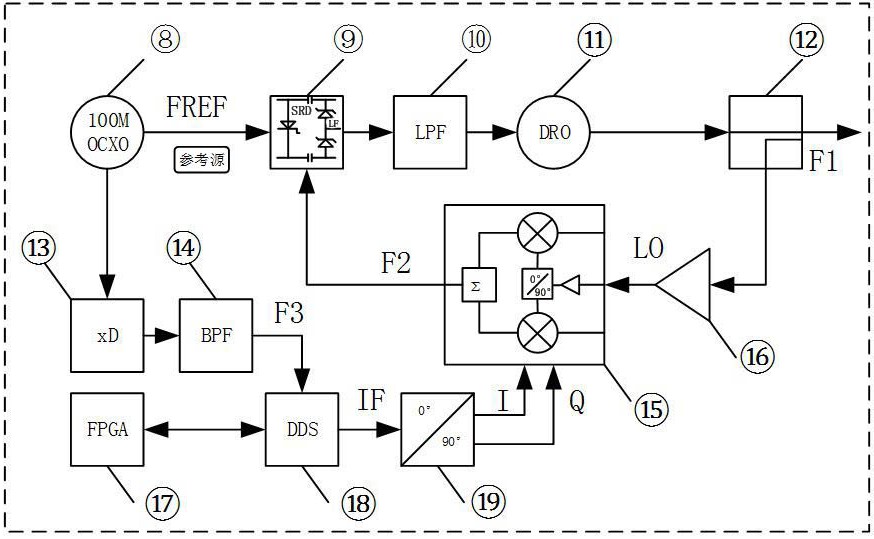

1、为了克服现有技术存在的缺点与不足,本发明提出了一种基于复数混频器可调超低相位噪声取样锁相电路,该电路包括:100m恒温晶振(ocxo)、取样鉴相器、低通滤波器、介质振荡器、耦合器、倍频器、带通滤波器、复数调制器、放大器、控制器fpga、dds以及正交功分器19;

2、100mhz的恒温晶振分两路、其中一路作为取样鉴相器的参考信号,另一路经过倍频器和带通滤波器倍频滤波后输出频率f3作为dds18的参考信号,dds在控制器fpga的控制下产生相应的中频if信号,介质振荡器经过耦合器后一路直接作为输出信号f1、另一路耦合信号经过放大器后作为复数调制器的本振信号,dds产生的中频信号if经过正交功分器转换为正交的iq信号,并与本振信号f2经过复数调制器调制以后得到射频信号f2,射频信号f2与100mhz的恒温晶振经过取样间相器模拟鉴相后产生控制信号,该信号经过低通滤波器滤除杂散信号后控制介质振荡器形成闭环控制。

3、进一步地,所述dds输出if=f3(ftw/2b),介质振荡器11输出频率f1与正交的if信号经过复数调制器15调制后得到射频信号f2=f1+if,射频信号f2与100mhz的参考信号fref整数倍相等即f2=n*fref,输出信号f1=if+n*fref即f1=n*fref-f3(ftw/2b),通过改变dds的频率控制字ftw进行介质振荡器的可调输出。

4、进一步地,所述ftw为dds的频率控制字,m为dds频率控制字位宽。

5、进一步地,所述f2=n*fref,其中n是根据需求确定的具体的一个值,不可变;

6、所述f1=n*fref-f3(ftw/2b),其中n是根据需求确定的具体的一个值,不可变。

7、进一步地,所述模拟鉴相器和介质振荡器采用srd结构作为振荡器,进行相位噪声的降低。

8、进一步地,所述dds输出信号经过正交功分器转换为正交的两路iq信号。

9、进一步地,采用复数调制器与正交的两路iq信号进行正交调制。

10、进一步地,所述dds用于细步进输出。

11、本发明具有如下有益效果:

12、本发明提出一种基于复数混频器可调超低相位噪声取样锁相电路,该电路采用srd结构的模拟鉴相器和介质振荡器作为振荡器,实现超低的相位噪声,将dds输出信号经过正交功分器转换为正交的两路iq信号,采用复数调制器与正交的两路iq信号进行正交调制,巧妙的剔除镜频信号f1-if、以及本振泄露既缩小了电路体积又提升了频谱纯度,内嵌dds作为细步进输出,实现了模拟取样振荡器的细步进可调输出。克服了传统模拟锁相环的局限性。

技术特征:1.一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,该电路包括:100m恒温晶振(8)、取样鉴相器(9)、低通滤波器(10)、介质振荡器(11)、耦合器(12)、倍频器(13)、带通滤波器(14)、复数调制器(15)、放大器(16)、控制器fpga(17)、dds(18)以及正交功分器(19);

2.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述dds(18)输出if=f3(ftw/2b),介质振荡器(11)输出频率f1与正交的if信号经过复数调制器(15)调制后得到射频信号f2=f1+if,射频信号f2与100mhz的参考信号fref整数倍相等即f2=n*fref,输出信号f1=if+n*fref即f1=n*fref-f3(ftw/2b),通过改变dds(18)的频率控制字ftw进行介质振荡器的可调输出。

3.如权利要求2所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述ftw为dds的频率控制字,m为dds频率控制字位宽。

4.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述f2=n*fref,其中n是根据需求确定的具体的一个值,不可变;

5.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述模拟鉴相器(9)和介质振荡器(11)采用srd结构作为振荡器,进行相位噪声的降低。

6.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述dds(18)输出信号经过正交功分器(19)转换为正交的两路iq信号。

7.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,采用复数调制器(15)与正交的两路iq信号进行正交调制。

8.如权利要求1所述的一种基于复数混频器可调超低相位噪声取样锁相电路,其特征在于,所述dds(18)用于细步进输出。

技术总结本发明公开了一种基于复数混频器可调超低相位噪声取样锁相电路,该电路包括:100M恒温晶振(OCXO)、取样鉴相器、低通滤波器、介质振荡器、耦合器、倍频器、带通滤波器、复数调制器、放大器、控制器FPGA、DDS以及正交功分器。该电路采用SRD结构的模拟鉴相器和介质振荡器作为振荡器,实现超低的相位噪声,将DDS输出信号经过正交功分器转换为正交的两路IQ信号,采用复数调制器与正交的两路IQ信号进行正交调制,巧妙的剔除镜频信号F1‑IF、以及本振泄露既缩小了电路体积又提升了频谱纯度,内嵌DDS作为细步进输出,实现了模拟取样振荡器的细步进可调输出。克服了传统锁相环的局限性。技术研发人员:梁国林,高栋,张少春受保护的技术使用者:成都玖锦科技有限公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/244809.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表