一种基于CMOS工艺的收发一体开关结构

- 国知局

- 2024-08-02 15:28:59

本发明属于集成电路设计,具体涉及一种基于cmos工艺的收发一体开关结构。

背景技术:

1、快速的互联网流量增长使光纤接入网络(如光纤到户)的新一波安装和升级成为可能,其中10gb/s级pon(无源光网络,passive optical network)部署正在稳步升级,以取代传统的gpon(千兆字节pon)。此外,新形式的高速网络(如光纤到房间)将进一步扩大从家庭门户到每个房间的高速光纤接入范围,从而要求在家庭内部署大量光纤链路。对于大规模的消费市场,系统的是否能够低成本实现特点将是影响其发展的关键。同时,作为高速光通信中成本最敏感的场景,经过二十年的优化,在使用pon收发器的光纤接入网络中,没有太多空间进一步大幅降低成本。在这方面,不仅对于光纤到房间,而且对于即将到来的光纤到万物的范式转变,都迫切需要具有更少成本的新结构。

2、大多数pon收发器中的现有的结构与方法对发射器(tx)和接收器(rx)路径采用两种不同的波长,以形成全双工光收发器。他们不仅需要单独的tx和rx光学器件,还不可避免地将光学对准、粘接和封装成本提高一倍,这与系统未来的大规模应用里对于低成本的要求是相违背的。因此,如图1(a)和图1(b)所示新的单波长半双工工作方式将非常有吸引力。通过重复使用tx和rx光学器件,有可能将光收发器的成本大致降低两倍,重要的是,半双工光收发器结构能够提供高数据速率以及提供了快速可配置性,以满足未来低成本光纤接入应用的需求。那么作为基本的系统骨架,集成收发一体(t/r)的开关结构是很重要的相关部分,并且由于其针对的应用场景的相关特点,此开关并非简单的双刀双掷开关结构,而是要有诸如高带宽,高线性度,大电流驱动能力等重要特点。

3、本工作的t/r开关的设计存在许多挑战,如:

4、(1)由于开关需要配合其他光器件以及电路其他部分一起传输高频数据,开关不可以给其他模块电路提供过大的寄生电容负担,从而减少其他电路模块的带宽,进而影响高频信号的传输,尤其对于需要接收传输放大较小电流信号的接收模式更是如此。因此设计开关所使用的电路器件要尽量选用栅极相对薄的器件。

5、(2)为了减少对于电路其他部分的负担从而选用薄栅管要面临的问题是电路器件的安全工作问题,由于信号的变化会引起电路器件周围电压的变化,器件节点之间如果压差过大,尤其薄栅管子耐压值相对厚栅管更低,会对电路的安全工作产生威胁。

6、(3)对于大信号的传输来说,优化信号的线性度是很重要的,尤其对于发射端来说,驱动某些光器件的电流信号甚至达到了直流一百二十毫安,交流八十毫安。

7、(4)由于此开关架构是集成了信号接收模式与信号发射模式两种模式的,在工作的时候,不可避免要涉及到模式的切换,因此努力保障信号接收模式与信号发射模式在进行模式切换时互相影响较小是很重要的,尤其是信号发射模式的信号较大,可能对信号接收模式带来干扰,因此需要采取一定措施来进行处理。

8、因此由于具体应用场景而带来的对于开关的附加约束条件使得大电流高速cmos高线性度t/r开关的设计面临更多困难。

技术实现思路

1、本发明的目的在于克服具体应用场景对大电流高速cmos高线性度t/r开关的附加约束条件的问题,提出了一种基于cmos工艺的收发一体开关结构。

2、为达到上述目的,本发明采用如下技术方案:

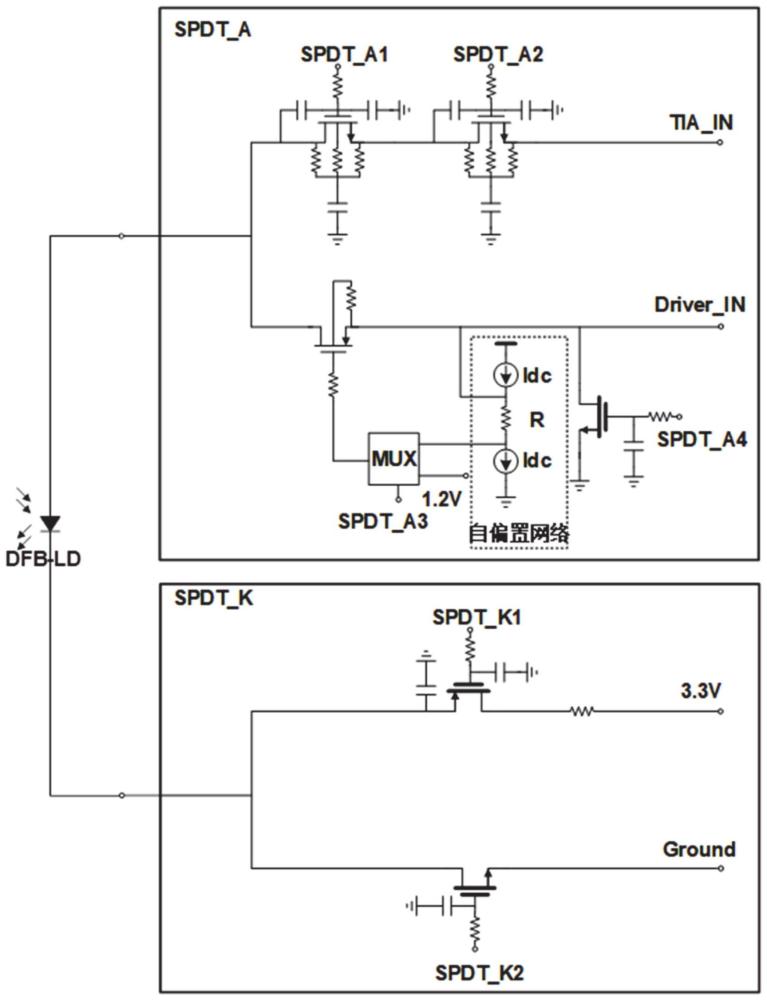

3、一种基于cmos工艺的收发一体开关结构,包括信号端开关电路spdt_a和电源/地端开关电路spdt_k,信号端开关电路spdt_a和电源/地端开关电路spdt_k之间连接激光器/光电探测器两用光器件,信号端开关电路spdt_a和电源/地端开关电路spdt_k均采用mos晶体管,mos晶体管的漏极与源极为信号通路,mos晶体管的栅极为控制端口,收发一体开关结构连接外部时序控制电路。

4、进一步地,信号端开关电路spdt_a设置第一端口tia_in、第二端口driver_in和第三端口;

5、第一端口tia_in的一端连接后级跨阻放大器,第二端口driver_in的一端连接前级激光驱动器,第三端口的一端与激光器/光电探测器两用光器件的阳极相连;

6、电源/地端开关电路spdt_k设置第四端口、第五端口ground和第六端口;第四端口连接电源电压,用于开关接收模式,第五端口ground连接地,用于开关发射模式,第六端口与激光器/光电探测器两用光器件的阴极相连。

7、进一步地,当开关工作在信号接收模式,信号端开关电路spdt_a的第一端口tia_in连接导通,第二端口driver_in连接断开,电源/地端开关电路spdt_k的第四端口连接导通,第五端口ground连接断开,激光器/光电探测器两用光器件为光电探测器工作。

8、进一步地,当开关工作在信号发射模式,信号端开关电路spdt_a的第一端口tia_in连接断开,第二端口driver_in连接导通,电源/地端开关电路spdt_k的第四端口连接断开,第五端口ground连接导通,激光器/光电探测器两用光器件为激光器工作。

9、进一步地,信号端开关电路spdt_a包括接收模式开关,接收模式开关的一端与第一端口tia_in的另一端连接,接收模式开关的另一端与第三端口的另一端连接,接收模式开关包括接收晶体管,接收晶体管包括第一nmos晶体管spdt_a1和第二nmos晶体管spdt_a2,接收晶体管设置电容前馈结构,接收晶体管的栅极连接栅极电阻,接收晶体管的栅极与外部时序控制电路连接;电容前馈结构为在接收晶体管的漏极与栅极之间以及接收晶体管的栅极与地之间均设置电容,第一nmos晶体管spdt_a1和第二nmos晶体管spdt_a2采用薄栅高速nmos晶体管。

10、进一步地,信号端开关电路spdt_a包括发射模式开关,发射模式开关的一端与第二端口driver_in的另一端连接,发射模式开关的另一端与第三端口的另一端连接;

11、发射模式开关包括第三pmos晶体管spdt_a3,第三pmos晶体管spdt_a3的源极连接片上多路选择器mux,片上多路选择器mux连接自偏置网络的一端,多路选择器mux控制第三pmos晶体管spdt_a3的开状态与关状态,开状态时多路选择器mux接至自偏置网络,关状态时多路选择器mux接至电压1.2v;多路选择器mux的控制行为通过外部时序控制电路控制;

12、自偏置网络的另一端与driver_in的另一端连接;

13、第三pmos晶体管spdt_a3为薄栅pmos晶体管;

14、发射模式开关的一端与第二端口driver_in的另一端之间连接导流nmos晶体管spdt_a4的漏极,导流nmos晶体管spdt_a4的栅极与外部时序控制电路连接。

15、进一步地,自偏置网络包括电流源和电阻r,电流源包括pmos电流源和nmos电流源,pmos电流源的大小和nmos电流源的大小相同,pmos电流源的一端与连接总供电电源,pmos电流源的另一端与电阻r的一端连接,电阻r的另一端与nmos电流源的一端连接,nmos电流源的另一端接地。

16、进一步地,电源/地端开关电路spdt_k包括电源pmos管spdt_k1和地端nmos管spdt_k2,电源pmos管spdt_k1的一端与第四端口连接,地端nmos管spdt_k2的一端与第五端口ground连接,电源pmos管spdt_k1的另一端、地端nmos管spdt_k2的另一端均与第六端口连接;

17、电源pmos管spdt_k1的栅极和地端nmos管spdt_k2的栅极均连接有低通滤波器,低通滤波器与外部时序控制电路连接,低通滤波器包括滤波电容和滤波电阻。

18、一种收发一体开关,利用所述的一种基于cmos工艺的收发一体开关结构。

19、一种半双工收发一体的光通信收发机系统,利用一种收发一体开关,一种收发一体开关采用所述的一种基于cmos工艺的收发一体开关结构。

20、与现有技术相比,本发明具有以下有益的技术效果:

21、本发明提出的一种基于cmos工艺的收发一体开关结构,采用cmos工艺,有利于进行系统集成,在系统层面将信号接收模式与信号发射模式集成在一起,帮助组成以半双工为工作方式的光通信收发前端。

22、进一步地,采用了电容前馈技术,缓和了器件面对的因信号变化而产生的电压波动,减小器件各节点电压差变化,使得接收电路的设计可以采用薄栅高速管,从而实现对于高速数据的传输。

23、进一步地,采用自偏置网络技术,优化了发射模式大信号输出的线性度,避免开关管栅源极电压差随着信号变化发生太大变化,从而稳定此开关管等效阻抗,进而减少谐波失真,实现开关的高线性度;自偏置网络的原理在于此电路结构中的采样电阻r只采样静态输入信号的电压值,开关管的栅源极电压差恒为电阻r上的电压差,大小为网络中电流值与电阻阻值的乘积,此电压差不随着driver_in进来的输入信号的工作点波动,因此保证了开关管的输出电阻的大小相对稳定,减少了谐波失真,提高了电路的线性度。

本文地址:https://www.jishuxx.com/zhuanli/20240801/246294.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种防水变频器的制作方法

下一篇

返回列表