一种提高外层阻抗模拟精度的PCB板结构模型的制作方法

- 国知局

- 2024-08-02 15:44:16

本技术涉及pcb板领域,具体涉及一种提高外层阻抗模拟精度的pcb板结构模型。

背景技术:

1、随着科技的不断发展,pcb板不断朝着高精度、高密度、高可靠性的方向发展,并不断缩小体积、降低成本、提高效能,使pcb板在未来电子产品的发展中保持了强大的生命力。

2、但高速pcb产品通常有信号完整性要求,阻抗管控是信号完整性要求中不可或缺的一环。业内常用的阻抗管控方法为,先用阻抗模拟软件中按阻抗关联的影响因素(影响因素有线宽、线距、铜厚、介质层厚度、阻焊油墨厚度、介质层dk等)对应的参考值去模拟外层阻抗模拟精度值,并在生产中通过控制这些影响因素的值去得到最终的阻抗,如此一来,外层阻抗模拟精度值就愈发重要。

3、在pcb板制作过程中,常通过电镀、磨板等制程制得外层线路图形,而经蚀刻而来的外层线路图形的横截面线型出现非单一形状的情况,而现有的外层图形线路结构形状仅采用单一梯形形状,用于外层阻抗模拟,与实际的外层线路形状贴合度不高,容易出现外层阻抗模拟精度较差的问题。

技术实现思路

1、为了克服现有技术的不足,本实用新型的目的在于提供一种提高外层阻抗模拟精度的pcb板结构模型,用于外层阻抗模拟过程,其可提高外层阻抗模拟精度,从而可得到准确度更高的产品阻抗。

2、本实用新型的目的采用以下技术方案实现:

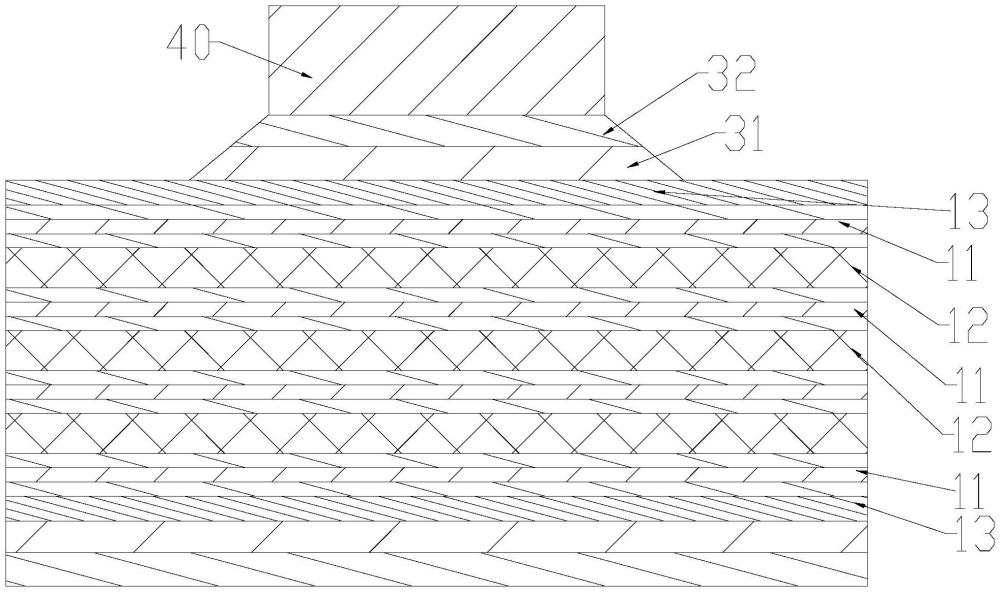

3、一种提高外层阻抗模拟精度的pcb板结构模型,包括主板体,所述主板体的外侧上设置有外层线路图形,所述外层线路图形包括内置线路体和外置线路体;所述内置线路体设置在外置线路体与主板体之间;所述外置线路体为通过图形电镀的方式而制作形成的图形铜层;从外置线路体靠近内置线路体的一端至远离内置线路体的一端,所述外置线路体的宽度均相同;从内置线路体靠近主板体的一端至靠近外置线路体的一端,所述内置线路体的宽度逐渐减小;所述外置线路体靠近内置线路体的一端的宽度与内置线路体靠近外置线路体的一端的宽度相同。

4、所述外层线路图形的厚度为30-60um。

5、所述外层线路图形的厚度与外置线路体的厚度的比值为:2-2.4。

6、所述内置线路体的横截面呈梯形状。

7、所述外置线路体的横截面呈矩形状。

8、所述内置线路体包括底铜层和电镀铜层;所述底铜层设置在主板体与电镀铜层之间。

9、所述主板体包括若干层芯板层;所述若干层芯板层从上至下依次排列,且顶层的芯板层、底层的芯板层均形成为端置板层;任意相邻的两芯板层之间均设置有中置粘结层。

10、所述底铜层通过外置粘结层设置在端置板层上。

11、所述中置粘结层、外置粘结层均为半固化片层。

12、相比现有技术,本实用新型的有益效果在于:

13、本实用新型提供的一种提高外层阻抗模拟精度的pcb板结构模型,其通过将外层线路图形采用内置线路体和外置线路体的结合,将外置线路体设置为通过图形电镀的方式而制作形成的图形铜层;并将所述外置线路体的宽度从外置线路体靠近内置线路体的一端至远离内置线路体的一端设置为相同,将所述内置线路体的宽度从内置线路体靠近主板体的一端至靠近外置线路体的一端设置为逐渐减小,同时将所述外置线路体靠近内置线路体的一端的宽度与内置线路体靠近外置线路体的一端的宽度设置为相同,此种外层线路图形的结构更贴合实际线路形状,用于外层阻抗模拟过程,可提高外层阻抗模拟精度,从而可得到准确度更高的产品阻抗。

技术特征:1.一种提高外层阻抗模拟精度的pcb板结构模型,其特征在于:包括主板体,所述主板体的外侧上设置有外层线路图形,所述外层线路图形包括内置线路体和外置线路体;所述内置线路体设置在外置线路体与主板体之间;所述外置线路体为通过图形电镀的方式而制作形成的图形铜层;从外置线路体靠近内置线路体的一端至远离内置线路体的一端,所述外置线路体的宽度均相同;从内置线路体靠近主板体的一端至靠近外置线路体的一端,所述内置线路体的宽度逐渐减小;所述外置线路体靠近内置线路体的一端的宽度与内置线路体靠近外置线路体的一端的宽度相同。

2.如权利要求1所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述外层线路图形的厚度为30-60um。

3.如权利要求2所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述外层线路图形的厚度与外置线路体的厚度的比值为:2-2.4。

4.如权利要求1所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述内置线路体的横截面呈梯形状。

5.如权利要求4所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述外置线路体的横截面呈矩形状。

6.如权利要求1所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述内置线路体包括底铜层和电镀铜层;所述底铜层设置在主板体与电镀铜层之间。

7.如权利要求6所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述主板体包括若干层芯板层;所述若干层芯板层从上至下依次排列,且顶层的芯板层、底层的芯板层均形成为端置板层;任意相邻的两芯板层之间均设置有中置粘结层。

8.如权利要求7所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述底铜层通过外置粘结层设置在端置板层上。

9.如权利要求8所述的提高外层阻抗模拟精度的pcb板结构模型,其特征在于:所述中置粘结层、外置粘结层均为半固化片层。

技术总结本技术公开了一种提高外层阻抗模拟精度的PCB板结构模型,包括主板体,所述主板体的外侧上设置有外层线路图形,所述外层线路图形包括内置线路体和外置线路体;所述内置线路体设置在外置线路体与主板体之间;所述外置线路体为通过图形电镀的方式而制作形成的图形铜层;从外置线路体靠近内置线路体的一端至远离内置线路体的一端,所述外置线路体的宽度均相同;从内置线路体靠近主板体的一端至靠近外置线路体的一端,所述内置线路体的宽度逐渐减小;所述外置线路体靠近内置线路体的一端的宽度与内置线路体靠近外置线路体的一端的宽度相同。本技术可提高外层阻抗模拟精度,从而可得到准确度更高的产品阻抗。技术研发人员:陈丽琴,陈蓓,李星受保护的技术使用者:深圳明阳电路科技股份有限公司技术研发日:20231215技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240801/247581.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。