一种用于残磁补偿电源的高分辨率数字脉宽调制器

- 国知局

- 2024-08-02 15:54:50

本发明属于电力电子,公开了一种用于残磁补偿电源的高分辨率数字脉宽调制器。

背景技术:

1、在数字开关电源领域,dpwm(数字脉宽调制器)的工作原理是用dpwm输出波形的占空比控制开关电源主电路中开关驱动管的通断进而达到调节输出电压的目的。dpwm的分辨率与输出电压精度有关,dpwm的分辨率如果低于adc的分辨率,系统就将会发生极限环振荡,从而导致系统不稳定,所以dpwm的分辨率必须高于adc的分辨率,从而保证输出电压的稳态精度,并且数字电源系统对dpwm的线性度、电路面积和功耗提出要求。所以进行高分辨率、高线性度且结构简单的高分辨率数字脉宽调制器的设计是必要的。

2、目前,高分辨率数字脉宽调制器主要有计数比较型,延迟链型和混合方式型三种方式。计数法在时钟源频率稳定的情况下能够精准的输出数字信号,然而当系统分辨率需求较高时,时钟源的频率以指数形式增加,导致系统结构复杂,且系统功耗增大。延迟链型和混合方式型都需要精度高的延迟单元和锁相环等复杂的延迟电路,同样使得系统结构复杂,系统功耗增加。

技术实现思路

1、发明目的:提供一种用于残磁补偿电源的高分辨率数字脉宽调制器,以解决现有技术存在的上述问题。

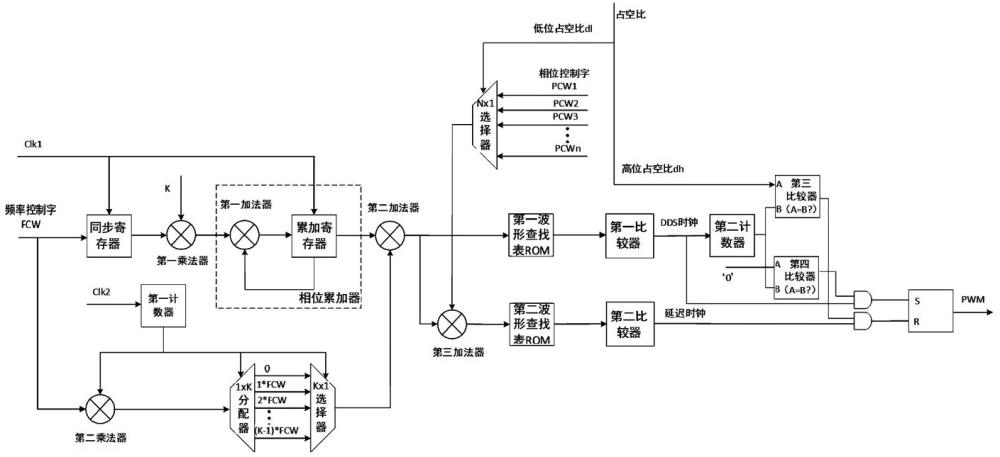

2、技术方案:一种用于残磁补偿电源的高分辨率数字脉宽调制器,包括:

3、dds时钟模块,包括:

4、dds主结构单元,用于生成dds时钟信号;

5、频率扩展单元,与dds主结构单元连接,用于扩展dds时钟信号的频率范围;

6、相位延迟单元,与dds主结构单元和相位延迟单元连接,用于生成延迟时钟信号;

7、输出模块,与dds时钟模块连接,基于扩展频率范围后的dds时钟信号和延迟时钟信号,生成pwm信号。

8、根据本申请的一个方面,所述dds主结构单元包括同步寄存器、相位累加器、第二加法器、第一乘法器、第一波形查找表rom和第一比较器,其中同步寄存器的数据输入端与频率控制字fcw相连,同步寄存器的时钟信号输入端与系统时钟clk1相连,同步寄存器的输出端与第一乘法器的输入端相连,第一乘法器的输出端和相位累加器的数据输入端相连,相位累加器的时钟信号输入端与系统时钟clk1相连,相位累加器的输出端与第二加法器的第一输入端相连,第二加法器的输出端与第一波形查找表rom的输入端相连,第一波形查找表rom的输出端与第一比较器的输入端相连。

9、根据本申请的一个方面,所述相位累加器包括第一加法器和累加寄存器。

10、根据本申请的一个方面,所述频率扩展单元包括第一计数器、第二乘法器、k×1选择器和1×k分配器,其中第二乘法器的第一输入端与频率控制字fcw相连,第二乘法器的输出端与1×k分配器的数据输入端相连,1×k分配器的k个输出端与k×1选择器的k个数据输入端相连,k×1选择器的输出端与所述dds主结构单元的第二加法器的第二输入端相连,第一计数器的时钟信号输入端与内部时钟clk2相连,第一计数器的输出端同时与第二乘法器的第二输入端、k×1选择器的选择端和1×k分配器的选择端相连。

11、根据本申请的一个方面,所述内部时钟clk2由系统时钟clk1驱动的振荡器产生,内部时钟clk2和系统时钟clk1的时钟同步,且内部时钟clk2和系统时钟clk1的频率比为k;

12、所述dds主结构单元的第一乘法器的频率倍增因子为k。

13、根据本申请的一个方面,所述相位延迟单元包括n×1选择器、第三加法器、第二波形查找表rom和第二比较器,其中n×1选择器的控制端与低位占空比信号dl相连,n×1选择器的数据输入端与相位控制字相连,n×1选择器的输出端与第三加法器的第一输入端相连,第三加法器的第二输入端与所述dds主结构单元的第二加法器的输出端相连,第三加法器的输出端与第二波形查找表rom的输入端相连,第二波形查找表rom的输出端与第二比较器的输入端相连。

14、根据本申请的一个方面,所述输出模块包括第二计数器、第三比较器、第四比较器、第一与门、第二与门和rs触发器,其中第二计数器的时钟信号输入端与所述dds主结构单元的第一比较器的输出端相连,第二计数器的输出端分别与第三比较器和第四比较器的b输入端相连,第三比较器的a输入端与高位占空比信号dh相连,第四比较器的a输入端与整数“0”相连,第三比较器的输出端与第一与门的第一输入端相连,第一与门的第二输入端与所述相位延迟单元的第二比较器的输出端相连,第一与门的输出端与rs触发器的r输入端相连,第四比较器的输出端与第二与门的第一输入端相连,第二与门的第二输入端与所述dds主结构单元的第一比较器的输出端相连,第二与门的输出端与rs触发器的s输入端相连。

15、有益效果:本发明通过dds时钟模块中的相位延迟模块,根据占空比信号控制时钟相位进行延迟,并且通过频率扩展模块输出了频率和相位可以灵活调节的高频率时钟信号,实现了高分辨率、高线性度且结构简单的设计要求,在简化电路结构的同时,还减少了系统功耗。

技术特征:1.一种用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,包括:

2.根据权利要求1所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述dds主结构单元包括同步寄存器、相位累加器、第二加法器、第一乘法器、第一波形查找表rom和第一比较器,其中同步寄存器的数据输入端与频率控制字fcw相连,同步寄存器的时钟信号输入端与系统时钟clk1相连,同步寄存器的输出端与第一乘法器的输入端相连,第一乘法器的输出端和相位累加器的数据输入端相连,相位累加器的时钟信号输入端与系统时钟clk1相连,相位累加器的输出端与第二加法器的第一输入端相连,第二加法器的输出端与第一波形查找表rom的输入端相连,第一波形查找表rom的输出端与第一比较器的输入端相连。

3.根据权利要求2所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述相位累加器包括第一加法器和累加寄存器。

4.根据权利要求3所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述频率扩展单元包括第一计数器、第二乘法器、k×1选择器和1×k分配器,其中第二乘法器的第一输入端与频率控制字fcw相连,第二乘法器的输出端与1×k分配器的数据输入端相连,1×k分配器的k个输出端与k×1选择器的k个数据输入端相连,k×1选择器的输出端与所述dds主结构单元的第二加法器的第二输入端相连,第一计数器的时钟信号输入端与内部时钟clk2相连,第一计数器的输出端同时与第二乘法器的第二输入端、k×1选择器的选择端和1×k分配器的选择端相连。

5.根据权利要求4所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述内部时钟clk2由系统时钟clk1驱动的振荡器产生,内部时钟clk2和系统时钟clk1的时钟同步,且内部时钟clk2和系统时钟clk1的频率比为k;

6.根据权利要求4所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述相位延迟单元包括n×1选择器、第三加法器、第二波形查找表rom和第二比较器,其中n×1选择器的控制端与低位占空比信号dl相连,n×1选择器的数据输入端与相位控制字相连,n×1选择器的输出端与第三加法器的第一输入端相连,第三加法器的第二输入端与所述dds主结构单元的第二加法器的输出端相连,第三加法器的输出端与第二波形查找表rom的输入端相连,第二波形查找表rom的输出端与第二比较器的输入端相连。

7.根据权利要求6所述的用于残磁补偿电源的高分辨率数字脉宽调制器,其特征在于,所述输出模块包括第二计数器、第三比较器、第四比较器、第一与门、第二与门和rs触发器,其中第二计数器的时钟信号输入端与所述dds主结构单元的第一比较器的输出端相连,第二计数器的输出端分别与第三比较器和第四比较器的b输入端相连,第三比较器的a输入端与高位占空比信号dh相连,第四比较器的a输入端与整数“0”相连,第三比较器的输出端与第一与门的第一输入端相连,第一与门的第二输入端与所述相位延迟单元的第二比较器的输出端相连,第一与门的输出端与rs触发器的r输入端相连,第四比较器的输出端与第二与门的第一输入端相连,第二与门的第二输入端与所述dds主结构单元的第一比较器的输出端相连,第二与门的输出端与rs触发器的s输入端相连。

技术总结本发明公开了一种用于残磁补偿电源的高分辨率数字脉宽调制器,包括DDS时钟模块和输出模块,其中所述DDS时钟模块包括DDS主结构单元,用于生成DDS时钟信号;频率扩展单元,与DDS主结构单元连接,用于扩展DDS时钟信号的频率范围;相位延迟单元,与DDS主结构单元和相位延迟单元连接,用于生成延迟时钟信号;所述输出模块,与DDS时钟模块连接,基于扩展频率范围后的DDS时钟信号和延迟时钟信号,生成PWM信号。本发明通过DDS时钟模块中的相位延迟模块,根据占空比信号控制时钟相位进行延迟,并且通过频率扩展模块输出了频率和相位可以灵活调节的高频率时钟信号,实现了高分辨率、高线性度且结构简单的设计要求,在简化电路结构的同时,还减少了系统功耗。技术研发人员:邹升,刘俊言,张红受保护的技术使用者:北京航空航天大学技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240801/248485.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表