一种多核结构处理器中锁步核调试及容错性能验证系统

- 国知局

- 2024-08-08 17:04:47

本发明涉及多核结构处理器的调试,具体涉及一种多核结构处理器中锁步核调试及容错性能验证系统。

背景技术:

1、随着微处理器芯片逐步采用纳米级制造工艺,在微处理器性能得到大幅提高的同时,由于集成电路特征尺寸的减小、频率的升高,使得处理器对于串扰、电压扰动、电磁干扰以及辐射等各种噪声干扰变得极为敏感,并可能引发错误的操作,导致微处理器的故障发生率不断攀升,微处理器的可靠性不断降低。改善的工艺往往采用更低的供电电压,这导致切换电流的噪声影响更加恶化。上述因素影响了系统部件的可靠性,进一步影响了系统的可靠性。

2、为了提高可靠性,目前主要的方案之一是使用多核锁步结构,其主要思想是在单个主核结构的基础上,增加多核与主核架构和结构完全相同的处理器核作为备份核,并与主核执行完全相同的程序,组成多核冗余锁步结构,通过执行结果的周期性比较,内部表决器会将相同结果多的一方作为正确输出,从而确保处理器的正常运行。但目前多核结构处理器的调试主要是针对主核,也存在一些针对双核锁步处理器的调试研究,但都是通过增加额外的调试硬件电路(目标核选择器以及每个核配套的调试控制电路)实现调试目标核的选择,并且也缺少对容错结构的功能正确性的验证,只能在处理器遇到故障时才能知道容错结构的功能是否正确,故容错结构的可靠性以及锁步核的可调试性都存在一定的不足。

技术实现思路

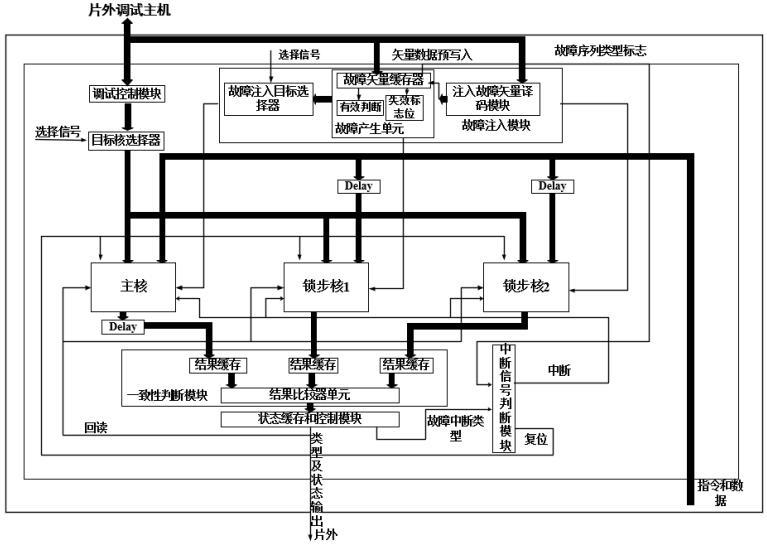

1、为了解决现有技术中存在的问题,本发明提供一种多核结构处理器中锁步核调试及容错性能验证系统,通过寄存器映射,用户配置对应寄存器可以实现对目标处理器核的选择,并且通过故障注入模块实现故障的主动产生,在系统的最后一级可以输出多核执行结果的对比状态,如果发生错误,中断信号判断模块可以迅速判断错误类型,并将信号返回给处理器核,以达到对冗余结构的容错性验证。

2、本发明具体通过以下技术方案实现:

3、提供一种多核结构处理器中锁步核调试及容错性能验证系统,包括:

4、多核锁步处理器组,其包含主核和至少两个锁步备份核,所述多核锁步处理器组用于执行相同的用户程序,并输出执行结果;

5、故障注入模块,其用于根据故障注入请求中的故障矢量序列号查找出相应的故障序列,然后选择目标核,并将所述故障序列输出至所述目标核内;其中,由代码编写故障信息并进行序列号,然后进行序列标准化后得到故障序列查找表,将所述故障序列查找表载入到所述故障注入模块的内存指定地址,用于故障序列的查找;

6、一致性判断模块,其用于对所述多核锁步处理器组的执行结果进行缓存,并在下一个时钟周期将所述多核锁步处理器组的上一周期的执行结果比较后输出比较结果;

7、状态缓存与控制模块,其用于接收所述一致性判断模块输出的比较结果并进行保存,然后对所述比较结果引起的状态以及后续操作进行控制。

8、作为本发明的进一步说明,所述故障序列的类型分为可恢复类型的故障序列以及不可恢复类型的故障序列。

9、作为本发明的进一步说明,所述验证系统还包括:

10、中断信号判断模块,其用于根据所述状态缓存与控制模块接收到的比较结果和对应故障序列的类型标志进行进一步比较,若为不可恢复故障,则选择进行全局复位;若为可恢复故障,则发送中断请求信号给对应的目标核,请求系统中断。

11、作为本发明的进一步说明,所述故障注入模块包括:

12、注入故障矢量译码模块,其用于将所述故障注入请求中的故障矢量序列号转译为故障产生单元能够识别的序列号信息,并将所述序列号信息传送给所述故障产生单元;

13、故障产生单元,其用于根据接收到的所述序列号信息,对其内部保存的故障序列查找表进行查表操作,若命中,则会直接取出内存对应地址的故障序列,并将所述故障序列输出至故障注入目标选择器选择的目标核中;

14、故障注入目标选择器,其用于对需要注入故障的目标核进行选择。

15、作为本发明的进一步说明,所述故障序列查找表中写入有默认故障序列信息。

16、作为本发明的进一步说明,在故障产生单元进行查表操作时,若未命中,则进一步判断是否启用默认故障序列进行输出,如果选择启用默认故障序列,则将所述默认故障序列输出至故障注入目标选择器选择的目标核中;如果不启用默认故障序列,则此次故障选择失败,故障注入不使能。

17、作为本发明的进一步说明,通过寄存器-内存地址映射,将所述故障注入目标选择器映射到内存中的外设地址区域,用户能够通过指针对所述地址区域进行访问并进行配置修改。

18、作为本发明的进一步说明,所述由代码编写故障信息并进行序列号,然后进行序列标准化后得到故障序列查找表,将所述故障序列查找表载入到所述故障注入模块的内存指定地址,具体包括:

19、由代码编写故障信息并进行序列号分配,得到故障序列;

20、在链接文件中指定一块内存区域作为故障信息存放的专用区域,设置该块内存区域的属性为只读属性,并在该区域的开头几个地址处的区域存放默认故障序列,然后在接下来的连续地址处存放经过序列标准化的故障序列,所述默认故障序列与所述标准化的故障序列构成故障序列查找表,最终得到带有故障序列查找表的链接文件;

21、所述带有故障序列查找表的链接文件通过调试接口载入到所述故障产生单元中的故障矢量缓存器组映射到的内存区域内。

22、作为本发明的进一步说明,所述一致性判断模块包括:

23、缓存器组单元,其用于对所述多核锁步处理器组的执行结果进行缓存,并将所述执行结果输出至结果比较器单元;

24、结果比较器单元,其用于在下一个时钟周期将所述多核锁步处理器组的上一周期的执行结果进行比较,并将比较结果输出至所述状态缓存与控制模块。

25、作为本发明的进一步说明,所述状态缓存与控制模块包括:

26、比较结果缓存单元,其用于接收所述一致性判断模块输出的比较结果并对所述比较结果进行保存;

27、控制单元,其用于对所述比较结果引起的状态以及后续操作进行控制。

28、与现有技术相比,本发明具有以下有益的技术效果:

29、1、在不增加硬件设计资源的前提下实现了对多核锁步结构调试链路的自由切换,并且调试目标核的选择可以让用户通过寄存器配置进行灵活选择。

30、2、实现了故障注入的主动调控,通过对传统的故障注入系统进行优化调整,可以实现软硬件协同对故障注入进行灵活配置,软件层面负责故障注入序列的实现和修改,硬件层面对故障序列的查找以及快速注入。此外,通过添加查找表的方式,使得故障序列类型定位更为迅速和准确,避免了锁步结构处理器遇到故障空等时间,提高了多核锁步处理器的验证效率。

31、本技术方案的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术方案而了解。本技术方案的目的和其他优点可通过在所写的说明书以及附图中所特别指出的结构来实现和获得。

32、下面通过附图和实施例,对本技术方案的技术方案做进一步的详细描述。

本文地址:https://www.jishuxx.com/zhuanli/20240808/272230.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。