基于双端口RAM的寄存器输出的FIFO电路、方法、芯片及设备与流程

- 国知局

- 2024-09-11 14:32:41

本发明涉及数据存储,具体是涉及一种基于双端口ram的寄存器输出的fifo电路、方法、芯片及设备。

背景技术:

1、在芯片设计或者fpga(field programmable gate array,现场可编程门阵列)开发领域,fifo(first input first output ,先入先出)的接口信号,通常是基于双端口ram(random access memory,随机存取存储器)的控制逻辑电路,转换为fifo的读写接口时序。fifo的数据位宽,即为ram的数据位宽;fifo的深度,即ram的深度。fifo的读写操作是彼此独立的,它们可以根据读写接口各自的状态,同时进行,所以fifo一般采用双端口ram。

2、参见图1,现有fifo电路的结构通常分为四个部分:写控制逻辑电路101、双端口ram102、读控制逻辑电路103、读写同步电路104。写控制逻辑电路101产生写数据指针或写计数,控制双端口ram102的写使能、写地址、写数据等,并产生fifo的满标志信号。读控制逻辑电103路产生读数据指针或读计数,控制双端口ram102的读使能、读地址、读数据等,并产生fifo的空标志信号。读写同步电路104用于同步写数据指针或写计数到读控制时钟域,以便与读数据指针或读计数比较产生空标志信号,以及用于同步读数据指针或读计数到写控制时钟域,与写数据指针或写计数比较产生满标志信号。

3、芯片设计和fpga开发时,ip(intellectual property,知识产权)提供商提供的ram标准单元ip都是ram block。大深度的fifo,需要多个标准单元的ram block拼接组成。fifo中对ram数据进行读写时,存在走线的延时,随着fifo的深度增加,将会越来越大,将严重制约整个芯片或者fpga的所能达到的最高时钟频率。特别是fpga,它的ram在芯片中的位置都是固定的,从而导致在读出数据时产生更大的读出走线延迟。参见图2,随着ram block的数量n越大,输出数据q的走线routing长度到输出选择电路mux_sel的距离越长,造成走线电路延迟越大。

4、为了解决ram读出数据走线延迟过大的问题,通常有两种办法,一种是自己在ramip核外额外增加一级读数据寄存器逻辑输出,另一种是利用ram ip核提供商提供现成的寄存器模式,由ram ip核自带的寄存器直接输出读数据。两种寄存器输出的区别在于寄存器离ram读出数据的走线距离,ip自带寄存器模式的寄存器紧邻每个ram block模块,走线距离要短,理论上可以得到更高的最高时钟频率。

5、使用ram的寄存器输出模式时,包括自己在ram外增加寄存器输出或者使用ram ip核自带的寄存器模式输出。但是,现有的ram的寄存器输出模式仍存在一些缺点,例如ram最后的读数据固定在读地址后的一个时钟周期内有效而不能保持一直有效,以及由于寄存器输出后需要设置一定的数据控制逻辑以适应后面使用读数据的时序逻辑或组合逻辑,会带来一定的路径延时。

技术实现思路

1、本发明的第一目的是提供一种可维持ram读数据持续有效且提高fifo电路逻辑布线效果的基于双端口ram的寄存器输出的fifo电路。

2、本发明的第二目的是提供一种可维持ram读数据持续有效且提高fifo电路逻辑布线效果的基于双端口ram的寄存器输出的fifo控制方法。

3、本发明的第三目的是提供一种包括上述基于双端口ram的寄存器输出的fifo电路的芯片。

4、本发明的第四目的是提供一种包括上述基于双端口ram的寄存器输出的fifo电路或芯片的电子设备。

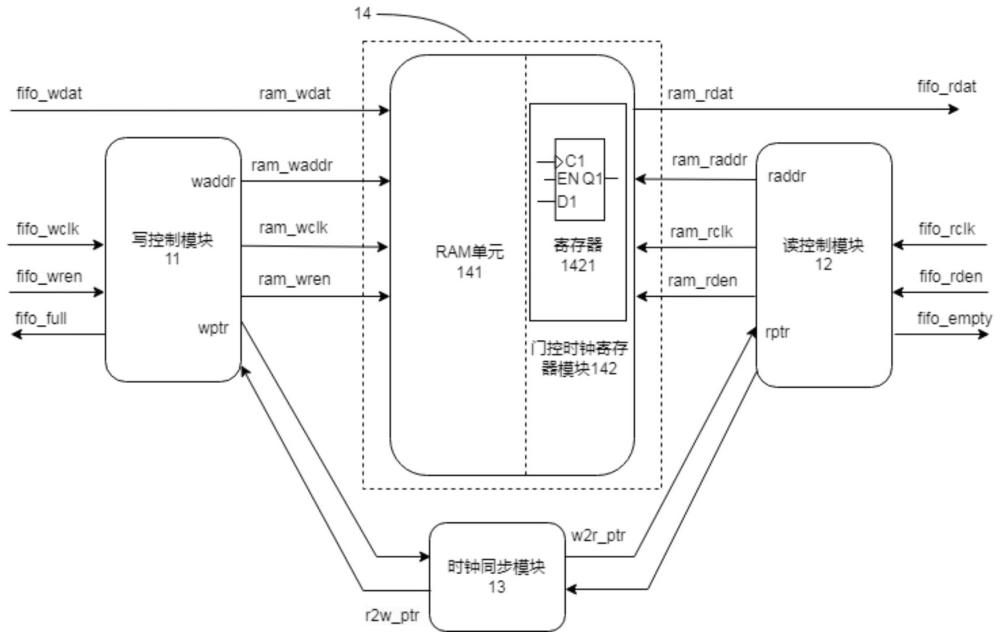

5、为了实现上述的第一目的,本发明提供的一种基于双端口ram的寄存器输出的fifo电路,包括写控制模块、读控制模块、双端口ram模块、时钟同步模块,双端口ram模块分别连接写控制模块和读控制模块,时钟同步模块分别连接写控制模块和读控制模块,双端口ram模块包括ram单元,其中,还包括:门控时钟寄存器模块,门控时钟寄存器模块包括门控时钟单元和寄存器,门控时钟单元分别连接读控制模块和寄存器的时钟端,寄存器的数据输入端连接ram单元,门控时钟单元用于从读控制模块获取ram读使能信号和ram读时钟信号,并基于ram读使能信号和ram读时钟信号输出门控信号至寄存器的时钟端。

6、由上述方案可见,本发明通过门控读出的ram数据后的输出寄存器的时钟的方式,实现寄存器输出ram读数据的效果。本发明实现的有益效果包括:(1)控制ram最后的读数据保持输出在寄存器输出端一直有效,而不是固定一个时钟周期有效;(2)基于受控寄存器输出端的数据维持特性,构建的fifo电路,可以过滤ram输出的无效数据,减少fifo电路输出数据的动态翻转,降低动态功耗;(3)门控时钟寄存器模块的插入,使ram输出数据和后面使用读数据的时序逻辑或组合逻辑之间增加了一级流水线,减少了ram输出数据布局布线的难度;(4)门控寄存器时钟模块的控制相比常规的数据控制使能信号来控制,虽然逻辑复杂度一样,但是减少了寄存器输出后的数据控制逻辑,从而使ram读数据与后面使用读数据的时序逻辑或组合逻辑之间的路径延时更短,后面逻辑的布局布线更容易。

7、进一步的方案是,双端口ram 模块包括门控时钟寄存器模块。

8、进一步的方案是,门控时钟单元包括锁存器和与门,锁存器的数据输入端和锁存器的控制端均与读控制模块连接,锁存器的数据输入端用于从读控制模块获取ram读使能信号,锁存器的控制端用于从读控制模块获取ram读时钟信号,锁存器的数据输出端连接与门的第一输入端,与门的第二输入端连接读控制模块,与门的第二输入端用于从读控制模块获取ram读时钟信号,与门的输出端连接寄存器的时钟端。

9、由此可见,门控时钟单元由低电平敏感的锁存器和与门实现,可以消除ram时钟使能信号和时钟沿之间偏差导致的门控信号产生的毛刺。

10、为了实现上述的第二目的,本发明提供的一种基于双端口ram的寄存器输出的fifo控制方法,应用于上述的基于双端口ram的寄存器输出的fifo电路,其中,包括以下步骤:门控时钟单元从读控制模块获取ram读时钟信号和ram读使能信号,门控时钟单元输出门控信号至寄存器的时钟端,门控信号根据ram读时钟信号与ram读使能信号相与操作得到,寄存器的数据输入端从ram单元获取ram输出数据并保存得到ram读数据,寄存器的输出端基于门控信号寄存输出ram读数据。

11、由上述方案可见,本发明通过ram读时钟信号与ram读使能信号相与操作得到门控信号输入到寄存器,通过门控信号控制进寄存器中ram读数据的输出,使得最后读出的ram读数据能够维持在寄存器的输出端一直维持有效。

12、为了实现上述的第二目的,本发明还提供一种基于双端口ram的寄存器输出的fifo控制方法,应用于上述的基于双端口ram的寄存器输出的fifo电路,其中,包括以下步骤:锁存器的数据输入端从读控制模块获取ram读使能信号,锁存器的控制端从读控制模块获取ram读时钟信号,锁存器的数据输出端基于ram读使能信号和ram读时钟信号输出锁存信号至与门的第一输入端,与门的第二输入端用于从读控制模块获取ram读时钟信号,与门的输出端输出门控信号至寄存器的时钟端,门控信号根据ram读时钟信号和锁存信号相与操作得到,寄存器的数据输入端从ram单元获取ram输出数据并保存得到ram读数据,寄存器的输出端基于门控信号寄存输出ram读数据。

13、由上述方案可见,本发明针对ram读时钟信号和ram使能信号在直接做逻辑与操作输出门控信号时,会因为ram读时钟信号的边沿与ram读使能信号跳变沿之间的延时使得时控信号产生毛刺的问题,通过锁存信号与ram读时钟信号相与操作可以得到消除毛刺后的门控信号。

14、为了实现上述的第三目的,本发明提供的一种芯片,其中,包括上述的基于双端口ram的寄存器输出的fifo电路。

15、为了实现上述的第四目的,本发明提供的一种电子设备,包括壳体,其中:壳体内包括上述的基于双端口ram的寄存器输出模式的fifo电路或上述的芯片。

本文地址:https://www.jishuxx.com/zhuanli/20240911/291333.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。