数据归一化RISC-V指令集扩展方法及硬件加速装置与流程

- 国知局

- 2024-10-21 14:51:53

本发明涉及机器学习、图像处理、信号处理的,尤其涉及一种数据归一化risc-v指令集扩展方法,以及一种数据归一化risc-v指令集扩展的硬件加速装置。

背景技术:

1、在机器学习、图像处理、信号处理等数据密集型领域,数据归一化是一种非常常见和重要的预处理步骤。数据归一化的目的是将数据映射到某个较小的区间内,如[0,1]或[-1,1],从而消除不同量纲数据之间的影响,提高模型训练的精度和收敛速度。

2、risc-v是一种基于“精简指令集(risc)”原则的开源指令集架构。指令集是cpu可以执行的操作规范,定义了如何进行运算,并通过优化设计帮助cpu更高效地运行,它是介于软件和底层硬件的一套程序指令集合集。与大多数指令集相比,risc-v指令集可以自由地用于任何目的,允许任何人设计、制造和销售risc-v芯片和软件。在现有的risc-v指令集中,缺乏专门用于进行数据归一化的指令。这种预处理操作通常需要通过一系列基础指令来完成,包括数据加载、算术计算(如减法和乘法)、条件分支等。

3、这种基于基础指令集的实现方式存在以下几个主要问题;执行效率低下,需要多条基本指令序列才能完成归一化,导致处理器执行周期过多,特别是在处理大规模数据集时,效率低下问题更加突出。代码复杂度高,编程人员需要手动组合多个基础指令来实现归一化,增加了编码和维护的复杂度。多次数据加载、存储和中间结果计算会导致额外的功耗,同时也需要预先分配额外存储空间,增加了内存开销。因此,急需开发一种新的方法,在硬件层面上高效地支持数据归一化处理,以提升risc-v架构在这些数据密集型应用中的性能和能效,满足日益增长的计算需求。

技术实现思路

1、为克服现有技术的缺陷,本发明要解决的技术问题是提供了一种数据归一化risc-v指令集扩展方法,其能够大幅提升数据归一化的计算效率,同时降低代码复杂度、功耗和内存开销,增强risc-v指令集的通用性。

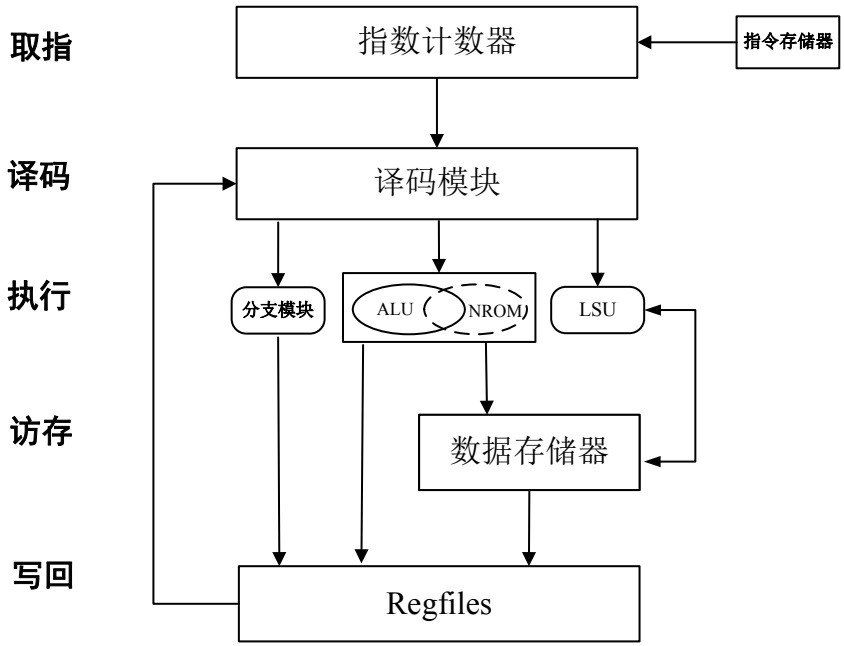

2、本发明的技术方案是:这种数据归一化risc-v指令集扩展方法,risc-v处理器采用五级流水线结构,其主要包括:

3、(1)在取指阶段,risc-v处理器根据指令计数器pc生成的地址预先取出存储在指令寄存器中对应的数据归一化的指令;

4、(2)在译码阶段,指令信号在译码模块通过分析func7和func3的编码来解析出对应的指令功能,并产生对应的控制信号;

5、(3)在执行阶段,先通过加载存储单元lsu模块将数据从数据存储器中取出,然后根据nrom指令在译码阶段产生的控制信号,将数据传入数据归一化扩展指令计算模块,最后根据公式

6、,

7、执行归一化过程,将归一化结果写回到对应的目的寄存器。

8、本发明的risc-v处理器采用五级流水线结构,在取指阶段处理器根据指令计数器生成的地址预先取出存储在指令寄存器中对应的数据归一化的指令,在译码阶段,指令信号在译码模块通过分析opcode、func7和func3的编码来解析出对应的指令功能,并产生对应的控制信号,进入到执行阶段,在执行归一化指令nrom之前,先通过加载存储单元lsu模块将数据从数据存储器中取出,然后根据nrom指令产生的控制信号,将数据传入数据归一化扩展指令计算装置,执行归一化过程,最后将归一化结果写回到对应的寄存器,该专用指令能够大幅提升数据归一化的计算效率,同时降低代码复杂度、功耗和内存开销,增强risc-v指令集的通用性。

9、本发明还提供了一种数据归一化risc-v指令集扩展的硬件加速装置,其集成在risc-v处理器核心中,包括:比较器、迭代模块、max模块、min模块、运算单元、数据归一化扩展指令计算模块;

10、比较器用于比较输入数据,将较大值送往max模块,较小值送往min模块;max模块和min模块分别计算输入数据的最大值和最小值;迭代模块包含rmax和rmin两个极值寄存器,用于简化最大/小值的迭代更新过程;运算单元包括减法运算单元和除法运算单元,复用risc-v处理器alu中的运算单元,执行归一化公式的减法和除法运算;在norm指令执行时,risc-v处理器首先通过加载存储单元lsu从数据存储器取出待归一化数据,并送入数据归一化扩展指令计算模块;数据归一化扩展指令计算模块进行归一化公式的高效计算,将结果写回目标寄存器。

技术特征:1.数据归一化risc-v指令集扩展方法,其特征在于:risc-v处理器采用五级流水线结构,其包括:

2.根据权利要求1所述的数据归一化risc-v指令集扩展方法,其特征在于:所述数据归一化扩展指令计算模块包括:比较器、迭代模块、max模块、min模块、减法运算单元和除法运算单元;当处理器检测到norm指令时,寄存器将待归一化的数据发送至数据归一化扩展指令计算模块进行数据归一化计算。

3.根据权利要求2所述的数据归一化risc-v指令集扩展方法,其特征在于:在数据归一化扩展指令计算模块中,输入的数据先通过比较器进行数据比较,根据比较结果分别将数据传递到max模块、min模块,这两个模块分别计算输入数据的最大值和最小值,并将这些值临时存储在迭代模块的最值寄存器里,通过迭代模块来更新这些最值数据。

4.根据权利要求3所述的数据归一化risc-v指令集扩展方法,其特征在于:所述迭代模块包括:rmax寄存器、rmin寄存器、比较器;rmax寄存器用于存储当前的最大值,rmin寄存器用于存储当前的最小值,当max和min模块计算出当前的极值后,这些值将送入迭代模块,并在比较器中与寄存器内的值进行比较,若当前最大值超过rmax寄存器中的值,则更新该寄存器;若当前最小值低于rmin寄存器中的值,则更新rmin寄存器;在迭代过程完毕后,迭代模块输出存储在rmax寄存器中的最大值和rmin寄存器中的最小值。

5.根据权利要求4所述的数据归一化risc-v指令集扩展方法,其特征在于:数据归一化扩展指令计算模块进行减法和除法运算,这些基础运算包含在risc-v处理器的算术逻辑单元alu中。

6.根据权利要求1所述的数据归一化risc-v指令集扩展方法,其特征在于:该方法采用risc-v的r型指令作为自定义指令格式,扩展指令包括:rs1、rs2、rd、funct7、funct3和opcode;rs1、rs2和rd寄存器地址位宽为5位,funct7的位宽为7位,funct3的位宽为3位,opcode的位宽为7位;rs1记录源操作数1的寄存器地址,rs2记录源操作数2的寄存器地址,opcode字段用于决定指令类型,funct3字段和funct7字段一起使用,判别数据归一化指令。

7.根据权利要求6所述的数据归一化risc-v指令集扩展方法,其特征在于:归一化指令的opcode编码与r-type指令的opcode编码保持一致,定义为0110011;funct3字段为000和r-type中的add和sub指令相同,funct7字段为000110;该方法指令形式为nrom rd,rs1,rs1代表要归一化的数据,rd代表归一化后的数据。

8.数据归一化risc-v指令集扩展的硬件加速装置,其特征在于:其集成在risc-v处理器核心中,包括:比较器、迭代模块、max模块、min模块、运算单元、数据归一化扩展指令计算模块;

9.根据权利要求8所述的数据归一化risc-v指令集扩展的硬件加速装置,其特征在于:该装置采用risc-v的r型指令作为自定义指令格式,扩展指令包括:rs1、rs2、rd、funct7、funct3和opcode;rs1、rs2和rd寄存器地址位宽为5位,funct7的位宽为7位,funct3的位宽为3位,opcode的位宽为7位;rs1记录源操作数1的寄存器地址,rs2记录源操作数2的寄存器地址,funct3字段和funct7字段一起使用,判别数据归一化指令。

10.根据权利要求9所述的数据归一化risc-v指令集扩展的硬件加速装置,其特征在于:归一化指令的opcode编码与r-type指令的opcode编码保持一致,定义为0110011;funct3字段为000和r-type中的add和sub指令相同,funct7字段为000110;该方法指令形式为nrom rd,rs1;rs1代表要归一化的数据,rd代表归一化后的数据。

技术总结本发明公开了数据归一化RISC‑V指令集扩展方法及硬件加速装置。NORM指令通过硬件层面直接高效地实现数据归一化,避免了基础指令序列的低效。扩展指令计算装置包含比较器、迭代模块、MAX/MIN模块及运算单元,利用硬件加速完成归一化公式的计算。迭代模块通过极值寄存器简化计算过程。该发明显著提升了数据计算效率,降低了代码复杂度、功耗和内存开销,并增强了指令集的通用性。最终,该扩展指令计算装置被集成到RISC‑V处理器核心中,实现了高效的数据归一化加速。技术研发人员:谢启祥,黄志洪,蔡刚,魏育成受保护的技术使用者:中科亿海微电子科技(苏州)有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/319592.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表