基于时序处理电路的PG信号上电响应方法与流程

- 国知局

- 2024-11-21 11:35:53

本申请涉及电源管理相关领域,尤其涉及基于时序处理电路的pg信号上电响应方法。

背景技术:

1、在当前的服务器主板设计中,电源管理是一个至关重要的环节,直接关系到服务器的稳定性和可靠性。服务器主板上通常集成了多个dc/dc电源芯片,这些电源芯片负责为服务器上的各个部件提供稳定的电压。为了确保电源系统的正常工作,每个电源芯片都会输出一个pg信号,用以指示其对应的输出电压是否已经达到稳定且可接受的状态,因此pg信号的有效与否直接关系到系统是否能够启动和稳定运行。在传统的服务器主板设计中,pg信号通常直接由电源芯片产生,并通过简单的上拉电阻连接到cpld(复杂可编程逻辑器件)或其他控制芯片的输入端。这种方法简单直接,然而由于电源芯片和cpld的电源域可能不同步,直接连接pg信号可能导致在电源未完全稳定时,cpld就接收到了错误的pg信号,从而引发误判。

2、现阶段相关技术中,pg信号上电响应存在无法准确判断电源状态,导致系统不稳定的技术问题。

技术实现思路

1、本申请通过提供基于时序处理电路的pg信号上电响应方法,采用明确pg信号上电响应应遵守的电源域范围,引入时序处理电路,根据电源域的范围和电源上电的时序,智能管理pg信号的上电响应,根据电源上电的不同阶段,生成并传递相应的pg信号等技术手段,达到了通过准确判断电源状态信息,提高系统稳定性的技术效果。

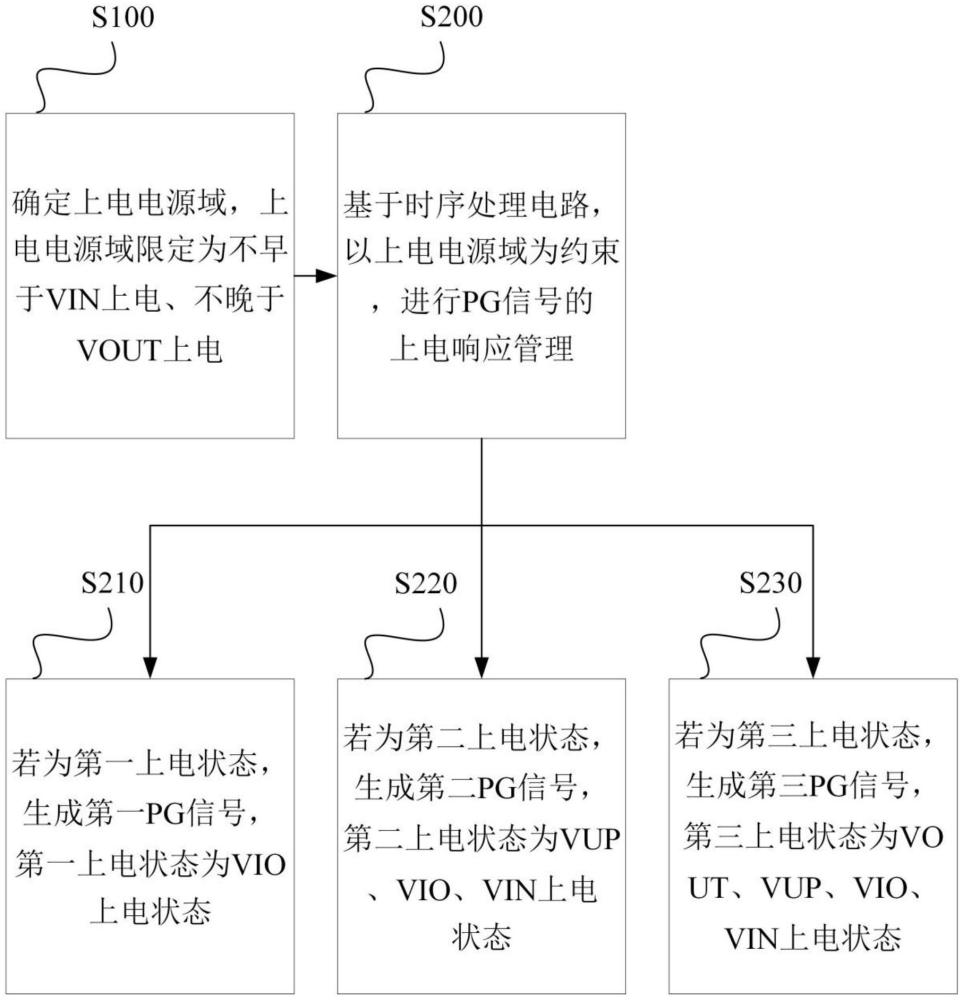

2、本申请提供基于时序处理电路的pg信号上电响应方法,包括:

3、确定上电电源域,所述上电电源域限定为不早于vin上电、不晚于vout上电;基于时序处理电路,以所述上电电源域为约束,进行pg信号的上电响应管理;其中,pg信号的上电响应管理包括:若为第一上电状态,生成第一pg信号,所述第一上电状态为vio上电状态;若为第二上电状态,生成第二pg信号,所述第二上电状态为vup、vio、vin上电状态;若为第三上电状态,生成第三pg信号,所述第三上电状态为vout、vup、vio、vin上电状态。

4、在可能的实现方式中,执行以下处理:

5、所述时序处理电路连接于可编程逻辑器件cpld与服务器主板之间,所述时序处理电路包含电流控制元件q1、上拉电阻r1、下拉接地电阻r2与r3。

6、在可能的实现方式中,执行以下处理:

7、若为所述第一上电状态,所述时序处理电路的状态为q1关闭状态,所述第一pg信号为低电平信号,其中,基于下拉接地电阻r2的下拉作用,将cpld的io固定为初始状态。

8、在可能的实现方式中,执行以下处理:

9、若为所述第二上电状态,所述时序处理电路的状态为q1关闭状态,所述第二pg信号为低电平信号,其中,基于下拉接地电阻r3的下拉作用,将cpld的io固定为初始状态。

10、在可能的实现方式中,执行以下处理:

11、若为所述第三上电状态,所述时序处理电路的状态为q1打开状态,所述第三pg信号为高电平信号,其中,基于r1与r3的分压作用,使q1呈打开状态。

12、在可能的实现方式中,执行以下处理:

13、cpld的io的初始状态为低电平状态,且所述初始状态下q1保持关闭状态。

14、在可能的实现方式中,执行以下处理:

15、基于所述服务器主板的多引脚接入,确定多组控制信号;遍历所述多组控制信号,配置cpld的控制逻辑块,所述控制逻辑块与所述多组控制信号一一对应,所述控制逻辑块基于上位器进行统筹管理;其中,所述多组控制信号包含pg信号组,所述pg信号组包含pg信号的多个信号状态,包含第一pg信号,第二pg信号与第三pg信号。

16、在可能的实现方式中,执行以下处理:

17、交互pg信号的历史响应记录,挖掘满足预设频次的存异响应记录;对所述存异响应记录进行溯源定位,确定诱因特征,并生成响应补偿逻辑,其中,所述响应补偿逻辑基于所述诱因特征触发;基于所述响应补偿逻辑,对cpld进行目标控制逻辑块的配置,其中,所述目标控制逻辑块为pg信号组的映射区块。

18、拟通过本申请提出的基于时序处理电路的pg信号上电响应方法,首先确定上电电源域,上电电源域限定为不早于vin上电、不晚于vout上电,然后基于时序处理电路,以上电电源域为约束,进行pg信号的上电响应管理,其中,pg信号的上电响应管理包括:若为第一上电状态,生成第一pg信号,第一上电状态为vio上电状态;若为第二上电状态,生成第二pg信号,第二上电状态为vup、vio、vin上电状态;若为第三上电状态,生成第三pg信号,第三上电状态为vout、vup、vio、vin上电状态,达到了通过准确判断电源状态信息,提高系统稳定性的技术效果。

技术特征:1.基于时序处理电路的pg信号上电响应方法,其特征在于,所述方法包括:

2.如权利要求1所述的基于时序处理电路的pg信号上电响应方法,其特征在于,所述时序处理电路连接于可编程逻辑器件cpld与服务器主板之间,所述时序处理电路包含电流控制元件q1、上拉电阻r1、下拉接地电阻r2与r3。

3.如权利要求2所述的基于时序处理电路的pg信号上电响应方法,其特征在于,若为所述第一上电状态,所述时序处理电路的状态为q1关闭状态,所述第一pg信号为低电平信号,其中,基于下拉接地电阻r2的下拉作用,将cpld的io固定为初始状态。

4.如权利要求2所述的基于时序处理电路的pg信号上电响应方法,其特征在于,若为所述第二上电状态,所述时序处理电路的状态为q1关闭状态,所述第二pg信号为低电平信号,其中,基于下拉接地电阻r3的下拉作用,将cpld的io固定为初始状态。

5.如权利要求2所述的基于时序处理电路的pg信号上电响应方法,其特征在于,若为所述第三上电状态,所述时序处理电路的状态为q1打开状态,所述第三pg信号为高电平信号,其中,基于r1与r3的分压作用,使q1呈打开状态。

6.如权利要求3所述的基于时序处理电路的pg信号上电响应方法,其特征在于,cpld的io的初始状态为低电平状态,且所述初始状态下q1保持关闭状态。

7.如权利要求2所述的基于时序处理电路的pg信号上电响应方法,其特征在于,所述方法还包括:

8.如权利要求1所述的基于时序处理电路的pg信号上电响应方法,其特征在于,所述方法还包括:

技术总结本发明公开了基于时序处理电路的PG信号上电响应方法,涉及电源管理相关领域,该方法包括:确定上电电源域,上电电源域为不早于VIN上电、不晚于VOUT上电;基于时序处理电路,进行PG信号的上电响应管理;若为第一上电状态,生成第一PG信号,第一上电状态为VIO上电状态;若为第二上电状态,生成第二PG信号,第二上电状态为VUP、VIO、VIN上电状态;若为第三上电状态,生成第三PG信号,第三上电状态为VOUT、VUP、VIO、VIN上电状态。解决了现有PG信号上电响应存在的无法准确判断电源状态,导致系统不稳定的技术问题,达到了通过准确判断电源状态信息,提高系统稳定性的技术效果。技术研发人员:何金义受保护的技术使用者:联想长风科技(北京)有限公司技术研发日:技术公布日:2024/11/18本文地址:https://www.jishuxx.com/zhuanli/20241120/331913.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表