一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法及装置

- 国知局

- 2024-12-06 12:10:02

本技术涉及向量处理器,特别涉及一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法及装置。

背景技术:

1、ft-m7032是一款多核数字信号处理器dsp(digital signal processor)向量处理器,其总体架构如图1a所示,它由一个16核中央处理器cpu(central processing unit)和四个通用计算数字信号处理器gpdsp(general-purpose digital signal processor)簇组成。其中,4个gpdsp簇提供主要的算力支持,每个gpdsp簇由8个通用dsp计算核和一个通过crossnet连接的全局共享内存gsm(global shared memory)组成。gsm支持同一gpdsp簇内的所有dsp计算核共同访问,cpu与4个gpdsp簇共享全局双倍数据速率ddr(double datarate)内存空间,但每个gpdsp簇只能访问对应的局部ddr内存空间。直接存储器存取dma(direct memory access)负责由ddr、gsm、标量存储sm(scalar memory)/向量存储am(vector memory)组成的多级存储结构之间的数据传输,单个gpdsp簇内gsm到dsp计算核的理论带宽远高于的ddr到dsp计算核的带宽。

2、现有技术中,向量处理器可实现稀疏矩阵乘法的多核计算,但不能涵盖多种计算场景,通用性低。因此,如何在实现稀疏矩阵乘法多核计算的前提下,适用于多种计算场景,高效发挥向量处理器的计算性能,成为了一个亟需解决的问题。

技术实现思路

1、基于上述问题,本技术提供了一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法及装置,以在实现稀疏矩阵乘法多核计算的前提下,适用于多种计算场景,高效发挥向量处理器的计算性能。

2、本技术公开了一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法,稀疏矩阵乘法为按稀疏格式压缩后的权值矩阵与稠密输入矩阵进行乘法计算,得到稠密输出矩阵的过程,所述方法包括:

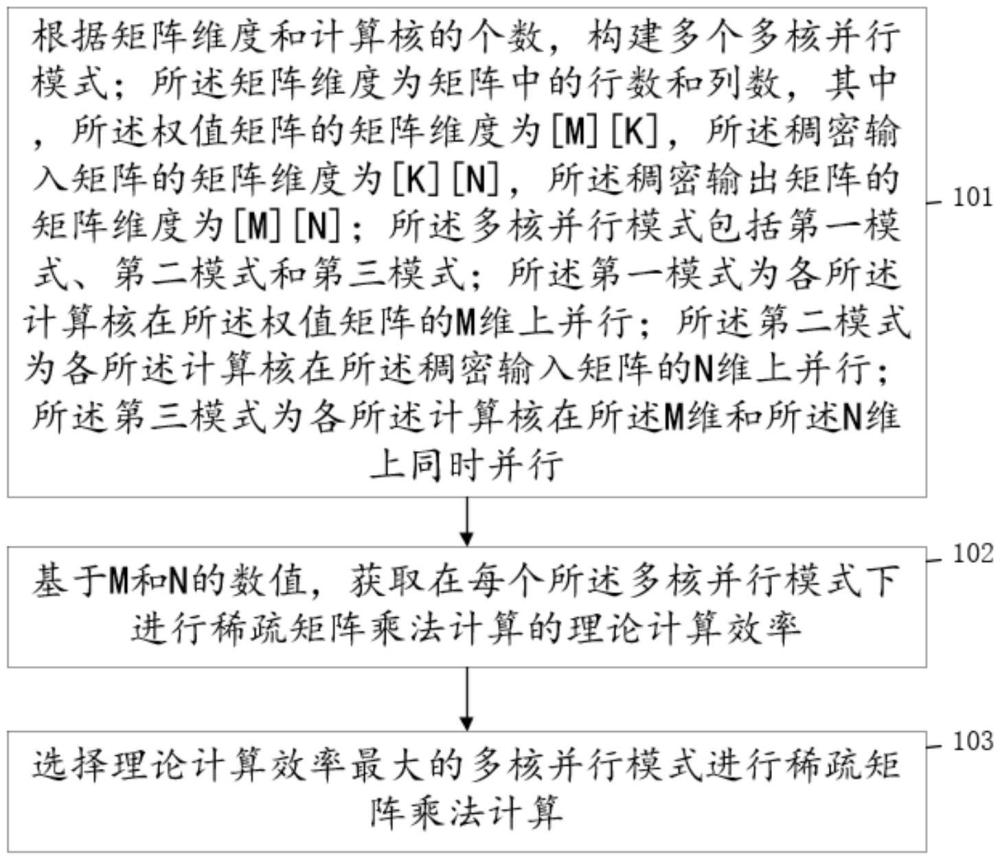

3、根据矩阵维度和计算核的个数,构建多个多核并行模式;所述矩阵维度为矩阵中的行数和列数,其中,所述权值矩阵的矩阵维度为[m][k],所述稠密输入矩阵的矩阵维度为[k][n],所述稠密输出矩阵的矩阵维度为[m][n];所述多核并行模式包括第一模式、第二模式和第三模式;所述第一模式为各所述计算核在所述权值矩阵的m维上并行;所述第二模式为各所述计算核在所述稠密输入矩阵的n维上并行;所述第三模式为各所述计算核在所述m维和所述n维上同时并行;

4、基于m和n的数值,获取在每个所述多核并行模式下进行稀疏矩阵乘法计算的理论计算效率;

5、选择理论计算效率最大的多核并行模式进行稀疏矩阵乘法计算。

6、可选的,所述计算核为8个,所述根据矩阵维度和计算核的个数,构建多个多核并行模式,包括:

7、将各所述计算核在所述权值矩阵上平均分配,构建所述第一模式;其中,每个所述计算核对应的所述权值矩阵的行数为八分之一m的向上取整,每个所述计算核对应的所述权值矩阵的列数为k。

8、可选的,所述获取在每个所述多核并行模式下进行稀疏矩阵乘法计算的理论计算效率,包括:

9、获取所述矩阵维度在所述第一模式下的理论计算效率如下式:

10、

11、式中,m_ratio为所述第一模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

12、可选的,所述计算核为8个,所述根据矩阵维度和计算核的个数,构建多个多核并行模式,包括:

13、将各所述计算核在所述稠密输入矩阵上平均分配,构建所述第二模式;其中,每个所述计算核对应的所述稠密输入矩阵的行数为k,每个所述计算核对应的所述稠密输入矩阵的列数为八分之一n的向上取整。

14、可选的,所述获取在每个所述多核并行模式下进行稀疏矩阵乘法计算的理论计算效率,包括:

15、获取所述矩阵维度在所述第二模式下的理论计算效率如下式:

16、

17、式中,n_ratio为所述第二模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

18、可选的,所述计算核为8个,所述第三模式包括第一子模式和第二子模式,所述根据矩阵维度和计算核的个数,构建多个多核并行模式,包括:

19、在所述权值矩阵的m维切分,得到2个行数为二分之一m、列数为k的第一子块,同时在所述稠密输入矩阵的n维切分,得到4个行数为k、列数为四分之一n的第二子块,构建所述第一子模式;一个所述计算核对应一种第一子块组合;所述第一子块组合为一个所述第一子块与一个所述第二子块的组合;

20、在所述权值矩阵的m维切分,得到4个行数为四分之一m、列数为k的第三子块,同时在所述稠密输入矩阵的n维切分,得到2个行数为k、列数为二分之一n的第四子块,构建所述第二子模式;一个所述计算核对应一种第二子块组合;所述第二子块组合为一个所述第三子块与一个所述第四子块的组合。

21、可选的,所述获取在每个所述多核并行模式下进行稀疏矩阵乘法计算的理论计算效率,包括:

22、获取所述矩阵维度在所述第一子模式下的理论计算效率如下式:

23、

24、获取所述矩阵维度在所述第二子模式下的理论计算效率如下式:

25、

26、式中,mn_ratio1为所述第一子模式的理论计算效率,mn_ratio2为所述第二子模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

27、可选的,所述选择理论计算效率最大的多核并行模式进行稀疏矩阵乘法计算,包括:

28、根据选择的多核并行模式,获取每个所述计算核并行时对应的权值矩阵块和稠密输入矩阵块;

29、将所述权值矩阵块发送至标量存储空间,将所述稠密输入矩阵块发送至向量存储空间;

30、将所述标量存储空间和所述向量存储空间中的矩阵块进行微内核计算,得到所述稠密输出矩阵。

31、可选的,所述微内核计算,包括:

32、将所述权值矩阵块与所述稠密输入矩阵块做稀疏矩阵乘法计算,得到大小为mb×nb的计算结果;所述mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

33、基于上述一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法,本技术还公开了一种面向向量处理器的半精度稀疏矩阵乘法多核并行的装置,稀疏矩阵乘法为按稀疏格式压缩后的权值矩阵与稠密输入矩阵进行乘法计算,得到稠密输出矩阵的过程,所述装置包括:模式构建单元、效率计算单元和计算单元;

34、所述模式构建单元,用于根据矩阵维度和计算核的个数,构建多个多核并行模式;所述矩阵维度为矩阵中的行数和列数,其中,所述权值矩阵的矩阵维度为[m][k],所述稠密输入矩阵的矩阵维度为[k][n],所述稠密输出矩阵的矩阵维度为[m][n];所述多核并行模式包括第一模式、第二模式和第三模式;所述第一模式为各所述计算核在所述权值矩阵的m维上并行;所述第二模式为各所述计算核在所述稠密输入矩阵的n维上并行;所述第三模式为各所述计算核在所述m维和所述n维上同时并行;

35、所述效率计算单元,用于基于m和n的数值,获取在每个所述多核并行模式下进行稀疏矩阵乘法计算的理论计算效率;

36、所述计算单元,用于选择理论计算效率最大的多核并行模式进行稀疏矩阵乘法计算。

37、可选的,所述计算核为8个,所述模式构建单元,包括:

38、第一分配子单元,用于将各所述计算核在所述权值矩阵上平均分配,构建所述第一模式;其中,每个所述计算核对应的所述权值矩阵的行数为八分之一m的向上取整,每个所述计算核对应的所述权值矩阵的列数为k。

39、可选的,所述效率计算单元,包括:

40、第一效率计算子单元,用于获取所述矩阵维度在所述第一模式下的理论计算效率如下式:

41、

42、式中,m_ratio为所述第一模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

43、可选的,所述计算核为8个,所述模式构建单元,包括:

44、第二分配子单元,用于将各所述计算核在所述稠密输入矩阵上平均分配,构建所述第二模式;其中,每个所述计算核对应的所述稠密输入矩阵的行数为k,每个所述计算核对应的所述稠密输入矩阵的列数为八分之一n的向上取整。

45、可选的,所述效率计算单元,包括:

46、第二效率计算子单元,用于获取所述矩阵维度在所述第二模式下的理论计算效率如下式:

47、

48、式中,n_ratio为所述第二模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

49、可选的,所述计算核为8个,所述第三模式包括第一子模式和第二子模式,所述模式构建单元,包括:

50、第三分配子单元,用于在所述权值矩阵的m维切分,得到2个行数为二分之一m、列数为k的第一子块,同时在所述稠密输入矩阵的n维切分,得到4个行数为k、列数为四分之一n的第二子块,构建所述第一子模式;一个所述计算核对应一种第一子块组合;所述第一子块组合为一个所述第一子块与一个所述第二子块的组合;

51、第四分配子单元,用于在所述权值矩阵的m维切分,得到4个行数为四分之一m、列数为k的第三子块,同时在所述稠密输入矩阵的n维切分,得到2个行数为k、列数为二分之一n的第四子块,构建所述第二子模式;一个所述计算核对应一种第二子块组合;所述第二子块组合为一个所述第三子块与一个所述第四子块的组合。

52、可选的,所述效率计算单元,包括:

53、第三效率计算子单元,用于获取所述矩阵维度在所述第一子模式下的理论计算效率如下式:

54、

55、第四效率计算子单元,用于获取所述矩阵维度在所述第二子模式下的理论计算效率如下式:

56、

57、式中,mn_ratio1为所述第一子模式的理论计算效率,mn_ratio2为所述第二子模式的理论计算效率,mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

58、可选的,所述计算单元,包括:

59、分块子单元,用于根据选择的多核并行模式,获取每个所述计算核并行时对应的权值矩阵块和稠密输入矩阵块;

60、存储子单元,用于将所述权值矩阵块发送至标量存储空间,将所述稠密输入矩阵块发送至向量存储空间;

61、输出子单元,用于将所述标量存储空间和所述向量存储空间中的矩阵块进行微内核计算,得到所述稠密输出矩阵。

62、可选的,所述输出子单元,用于:

63、将所述权值矩阵块与所述稠密输入矩阵块做稀疏矩阵乘法计算,得到大小为mb×nb的计算结果;所述mb为预设的所述m维的分块大小,nb为预设的所述n维的分块大小。

64、本技术公开了一种面向向量处理器的半精度稀疏矩阵乘法多核并行的方法及装置。根据矩阵的维度和计算核的个数,构建了三种多核并行模式,适用于多种计算场景,充分利用了向量处理器的多核架构。同时减少了部分矩阵维度规格下的计算冗余,提高了稀疏矩阵乘法计算的并行度,有助于发挥向量处理器的计算性能。其中,各多核并行模式为将多个计算核在权值矩阵和稠密输入矩阵的各维度上并行,将稀疏矩阵乘法在不同维度分核并行实现。基于两矩阵的维度规格,获取在每个多核并行模式下进行稀疏矩阵乘法计算的理论计算效率。再选择理论计算效率最大的多核并行模式进行稀疏矩阵乘法计算。如此能够自动适配性能最优的模式执行计算,通用性高,且提升了计算效率。

本文地址:https://www.jishuxx.com/zhuanli/20241204/339720.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表