一种数据处理系统、方法及计算机系统与流程

- 国知局

- 2024-12-06 13:05:04

本发明涉及计算机系统领域,特别涉及一种数据处理系统、方法及计算机系统。

背景技术:

1、在当前人工智能模型的训练过程中,由于单个gpu(graphics processing unit,图形处理单元)芯片的计算能力有限,因此需要多个gpu芯片协同计算,涉及到多个gpu芯片之间的互联通信,以及中间计算数据的传输。为解决内存不足的问题,通常采用内存扩展卡。

2、内存扩展卡通常通过pcie(peripheral component interconnect express,外围组件互连)接口与计算机系统连接,为gpu芯片提供更多的内存资源,以支持其处理更复杂的数据集和计算任务。但在gpu芯片访问这些扩展内存时,必须通过cpu(centralprocessing unit,中央处理单元)进行内存拷贝操作,这使得访问路径变长,延时增大,且扩展内存的容量也受限,从而造成了预训练模型训练通信瓶颈。

3、因此,如何提供一种解决上述技术问题的方案是本领域技术人员目前需要解决的问题。

技术实现思路

1、本发明的目的是提供一种数据处理系统、方法及计算机系统,能够使处理板可以对内存扩展板上的存储组件直接进行访问,而无需通过服务器主机进行内存拷贝,降低了处理板访问扩展内存时和服务器主机之间的耦合度,在有效扩展了处理板的内存的同时,缩短了处理板对扩展内存的访问路径,降低了访问延时,从而减小了预训练模型训练过程中的通信瓶颈。

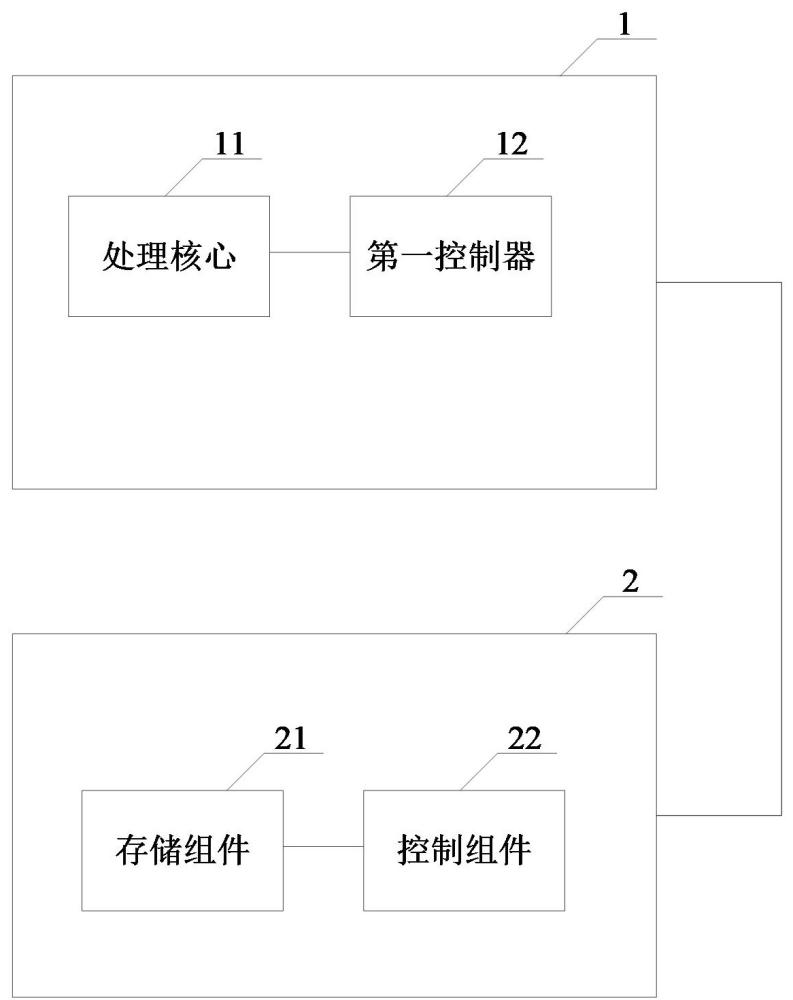

2、为解决上述技术问题,本发明提供了一种数据处理系统,包括处理板和内存扩展板;所述处理板包括:处理核心,用于通过桥接驱动线程识别存储组件,建立所述处理板的地址空间与所述存储组件之间的第一映射关系,并转发符合所述第一映射关系的内部访问请求;所述内部访问请求包括所述处理核心生成的第一内部访问请求;第一控制器,用于将接收到的所述内部访问请求转换为扩展访问请求并输出;所述内存扩展板包括所述存储组件和控制组件,所述控制组件用于响应所述扩展访问请求对所述存储组件执行访问操作。

3、其中,所述处理板还包括第二控制器,用于建立所述存储组件与服务器主机的地址空间之间的第二映射关系,并转发所述服务器主机发送的、符合所述第二映射关系的第一主机访问请求;所述第一控制器还用于将接收到的所述第一主机访问请求转换为所述扩展访问请求并输出。

4、其中,所述处理板还包括系统总线,用于将所述内部访问请求转发至所述第一控制器,和/或将所述第一主机访问请求转发至所述第一控制器。

5、其中,所述处理核心具体用于生成内部访问请求,通过桥接驱动线程识别存储组件,并建立所述处理板的地址空间与所述存储组件的物理地址之间的第一映射关系,转发目的地址与所述第一映射关系匹配的内部访问请求,丢弃所述目的地址与所述第一映射关系不匹配的内部访问请求。

6、其中,所述处理板还包括至少一个计算核心,用于生成与当前计算需求对应的第二内部访问请求;所述内部访问请求还包括所述第二内部访问请求。

7、其中,所述内存扩展板还包括监测管理模块,用于检测所述内存扩展板的运行状态。

8、其中,所述控制组件包括:分析处理模块,用于基于接收到的当前访问请求的访问地址和访问类型生成并输出目标内存访问请求;所述当前访问请求包括所述扩展访问请求;内存控制模块,用于对所述存储组件执行与所述目标内存访问请求对应的访问操作。

9、其中,所述分析处理模块包括第一硬核模块,用于基于接收到的扩展访问请求的访问地址和访问类型生成并输出第一内存访问请求;所述目标内存访问请求包括所述第一内存访问请求;所述内存控制模块具体用于响应于接收到的所述第一内存访问请求,对所述存储组件执行对应的访问操作。

10、其中,所述分析处理模块还包括第二硬核模块,用于基于接收到的第二主机访问请求的访问地址和访问类型生成并输出第二内存访问请求;所述当前访问请求还包括服务器主机发送的所述第二主机访问请求,所述目标内存访问请求还包括所述第二内存访问请求;所述内存控制模块具体用于响应于接收到的所述第二内存访问请求,对所述存储组件执行对应的访问操作。

11、其中,所述分析处理模块还包括:网络接口模块,用于接收远程访问请求;网络协议栈,用于基于所述远程访问请求的访问地址和访问类型生成并输出第三内存访问请求;所述目标内存访问请求还包括所述第三内存访问请求,所述当前访问请求还包括所述远程访问请求;所述内存控制模块具体用于响应于接收到的所述第三内存访问请求,对所述存储组件执行对应的访问操作。

12、其中,所述分析处理模块还包括访问仲裁模块,用于对接收到的所述第一内存访问请求和/或所述第二内存访问请求和/或所述第三内存访问请求进行仲裁,并输出仲裁成功的目标内存访问请求。

13、其中,所述内存扩展板还包括与所述网络接口模块连接的网络光模块,用于接收远端计算节点发送的所述远程访问请求。

14、其中,所述控制组件还包括控制寄存器模块,用于对所述内存控制模块和所述分析处理模块中的寄存器进行管理。

15、其中,所述存储组件包括非易失性存储设备;所述内存控制模块包括:共享内存控制器,用于将接收到的目标内存访问请求的访问地址的访问状态设定为锁定状态,并转发所述目标内存访问请求;内存访问控制器,用于按所述目标内存访问请求的访问地址和访问类型对所述非易失性存储设备执行对应的访问操作。

16、其中,所述存储组件还包括内存颗粒;所述内存访问控制器具体用于解析并转发所述目标内存访问请求中的访问信息;所述访问信息包括目标内存访问请求对应的访问类型和访问地址;所述内存控制模块还包括:缓存控制器,用于响应于所述访问信息中的访问类型为读操作类型,若所述访问信息中的访问地址命中缓存,从所述内存颗粒中读取对应的响应数据并返回至所述内存访问控制器,否则,转发所述访问信息,并将存储控制器返回的响应数据缓存在所述内存颗粒中;所述存储控制器,用于按所述缓存控制器发送的访问信息中的访问地址,在所述非易失性存储设备中读取对应的响应数据并返回。

17、其中,所述缓存控制器还用于响应于所述访问信息中的访问类型为写操作类型,转发所述访问信息;所述存储控制器还用于按所述缓存控制器发送的访问信息中的访问地址,将所述访问信息中的访问数据写入所述非易失性存储设备。

18、其中,所述存储控制器具体用于基于所述缓存控制器发送的访问信息中的访问地址确定包括所述访问地址的读取地址范围,按所述读取地址范围在所述非易失性存储设备中读取待缓存数据并返回;所述缓存控制器具体用于响应于所述访问信息中的访问类型为读操作类型,若所述访问信息中的访问地址命中缓存,从所述内存颗粒中读取对应的响应数据并返回至所述内存访问控制器,否则,转发所述访问信息,将所述待缓存数据缓存在所述内存颗粒中,并将所述待缓存数据中的响应数据返回至所述内存访问控制器。

19、其中,所述内存访问控制器还用于将所述响应数据返回至所述共享内存控制器,以便通过所述共享内存控制器将所述响应数据返回至所述目标内存访问请求的发送方;所述发送方为服务器主机或所述处理板或远程计算节点。

20、为解决上述技术问题,本发明还提供了一种计算机系统,包括服务器主机以及如上文任意一项所述的数据处理系统。

21、为解决上述技术问题,本发明还提供了一种数据处理方法,应用于如上文任意一项所述的数据处理系统,所述数据处理系统包括处理板和设有存储组件的内存扩展板,所述数据处理方法包括:

22、通过所述处理板上的处理核心通过桥接驱动线程识别存储组件,建立所述处理板的地址空间与所述存储组件之间的第一映射关系,并转发符合所述第一映射关系的内部访问请求;所述内部访问请求包括所述处理核心生成的第一内部访问请求;通过所述处理板上的第一控制器将接收到的所述内部访问请求转换为扩展访问请求并输出;通过所述内存扩展板上的控制组件响应所述扩展访问请求对所述存储组件执行访问操作。

23、本技术提供了一种数据处理系统,将内存扩展板和处理板通过连接器和线缆直接连接,降低了处理板访问扩展内存时和服务器主机之间的耦合度,在处理板的一个处理核心上使用一个线程实现了桥接驱动功能,对与自身连接的内存扩展板上的处理组件进行识别和地址映射,以使处理板可以对内存扩展板上的存储组件直接进行访问,而无需通过cpu进行内存拷贝,在有效扩展了处理板的内存的同时,缩短了处理板对扩展内存的访问路径,降低了访问延时,从而减小了预训练模型训练过程中的通信瓶颈。

24、本技术还提供了一种数据处理方法及计算机系统,具有和上述数据处理系统相同的有益效果。

本文地址:https://www.jishuxx.com/zhuanli/20241204/343187.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表