1.本技术案主张2020年8月18日申请的美国正式申请案第16/996,151号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开是关于一种半导体元件及其制备方法。特别是有关于一种具有石墨烯基元素(graphene-based element)的半导体元件以及其制备方法。

背景技术:

3.对于许多现代应用,半导体元件是不可或缺的。举例而言,半导体元件是广泛地运用在各种电子应用中,例如个人电脑、移动电话、数码相机以及其他电子设备。再者,随着电子科技的进步,半导体元件的尺寸变得越来越小,于此同时提供较佳的功能以及包含较大的集成电路数量。然而,随着半导体元件的按比例缩小,相邻导电元件之间的间隔是逐渐缩小,其是可缩减内连接结构的制程裕度(process window)。因此,在半导体元件中制造内连接结构则越来越困难。因此,在提高品质、良率、效能以及可靠性以及降低复杂性的方面仍持续存在挑战性。

4.上文的「先前技术」说明仅是提供背景技术,并未承认上文的「先前技术」说明揭示本公开的标的,不构成本公开的先前技术,且上文的「先前技术」的任何说明均不应作为本案的任一部分。

技术实现要素:

5.本公开的一实施例提供一种半导体元件。该半导体元件具有一堆叠栅极结构,设置在一半导体基底;一第一间隙子,设置在该堆叠栅极结构两侧;以及一第二间隙子,设置在该第一间隙子两侧,其中该第一间隙子具有一石墨烯(graphene)。

6.在一实施例中,该半导体元件还包括一多孔间隙子,设置在该第一间隙子与该第二间隙子之间。

7.在一实施例中,该多孔间隙子是具有约30%与约90%的孔隙率。

8.在一实施例中,该堆叠栅极结构包括:一介电层,设置在该半导体基底上;一底部电极层,设置在该介电层上;一顶部电极层,设置在该底部电极层上;以及一罩盖层,设置在该顶部电极层上。

9.在一实施例中,该堆叠栅极结构还包括一第一中间电极层,设置在该底部电极层与该顶部电极层之间。

10.在一实施例中,该堆叠栅极结构亦包括一第二中间电极层,设置在该第一中间电极层与该顶部电极层之间。

11.在一实施例中,该第一中间电极层的厚度是约2nm与约20nm。

12.在一实施例中,该半导体元件还包括一气隙间隙子,设置在该第一间隙子与该第二间隙子之间。

13.本公开的另一实施例提供一种半导体元件的制备方法,包括:提供一半导体基底;

形成一堆叠栅极结构在该半导体基底上;形成一第一间隙子在该堆叠栅极结构侧壁上,其中该第一间隙子包括石墨烯;形成一牺牲间隙子在该第一间隙子侧壁上;以及形成一第二间隙子在该牺牲间隙子侧壁上。

14.在一实施例中,该制备方法还包括进行一能量处理,其是引起该牺牲间隙子进行反应,进而形成一多孔间隙子。

15.在一实施例中,该多孔间隙子是具有约30%与约90%的孔隙率。

16.在一实施例中,形成一堆叠栅极结构在该半导体基底上是包括:形成一介电层在该半导体基底上,形成一底部电极层在该介电层上,形成一顶部电极层在该底部电极层上,形成一罩盖层在该顶部电极层上;以及进行一蚀刻制程是以形成该堆叠栅极结构。

17.在一实施例中,形成一堆叠栅极结构在该半导体基底上,还包括:形成一第一中间电极层在该底部电极层与该顶部电极层之间。

18.在一实施例中,形成一堆叠栅极结构在该半导体基底上,亦包括:形成一第二中间电极层在该第一中间电极层与该顶部电极层之间。

19.在一实施例中,该第一中间电极层的厚度是约2nm与约20nm。

20.在一实施例中,该制备方法还包括:进行一能量处理,其是将该牺牲间隙子转变成一气隙间隙子,该气隙间隙子是在该第一间隙子与该第二间隙子之间。

21.在一实施例中,形成一第一间隙子在该堆叠栅极结构侧壁上是包括:形成一衬垫层,覆盖该半导体基底与覆盖该堆叠栅极结构,以及进行一蚀刻制程,是以形成该第一间隙子。

22.本公开的另一实施例提供一种半导体元件。该半导体元件具有一半导体基底;一堆叠栅极结构,设置在该半导体基底上;一第一间隙子,设置在该堆叠栅极结构两侧;以及一第二间隙子,设置在该第一间隙子两侧。该第一间隙子具有一石墨烯。

23.在一实施例中,该半导体元件是具有一多孔间隙子,设置在该第一间隙子与该第二间隙子之间。

24.在一实施例中,该多孔间隙子是具有约30%与约90%的孔隙率。

25.在一实施例中,该堆叠栅极结构是具有一介电层,设置在该半导体基底上;一底部电极层,设置在该介电层上;一顶部电极层,设置在该底部电极层上;以及一罩盖层,设置在该顶部电极层上。

26.在一实施例中,该堆叠栅极结构还具有一第一中间电极层,设置在该底部电极层与该顶部电极层之间。

27.在一实施例中,该堆叠栅极结构亦具有一第二中间电极层,设置在该第一中间电极层与该顶部电极层之间。

28.在一实施例中,该第一中间电极层的厚度是约2nm与约20nm。

29.本公开的另一实施例提供一种半导体元件的制造方法,包括:提供一半导体基底;形成一第一沟槽在该半导体基底中;共形形成一埋入介电层在该第一沟槽中;共形形成一埋入覆盖层,是覆盖该第一沟槽的一上部;形成一埋入电极层在该埋入介电层上、在该埋入罩盖层之间以及在该第一沟槽中;以及形成一罩盖层在该埋入电极层上。该埋入电极层包括一石墨烯。

30.在一些实施例中,该制备方法包括:共形形成一埋入阻挡层在该埋入介电层上及

在与该第一沟槽中。

31.在一实施例中,该埋入覆盖层是由下列材料所制:氧化铝、氧化铪、氧化锆、氧化钛、氮化钛、氮化钨、氮化硅及/或氧化硅。

32.由于本公开的半导体元件设计,埋入电极层其总横截面积是以通过埋入电极层的上部而增加。结合具有石墨烯的埋入导电层的良好导电性,是可改善半导体件的导电性与效能。再者,埋入罩盖层是可防止半导体元件在制造中形成空隙。所以,半导体元件其可制性是以提高。

33.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

34.参阅实施方式与权利要求合并考量图式时,可得以更全面了解本技术案的揭示内容,图式中相同的元件符号是指相同的元件。

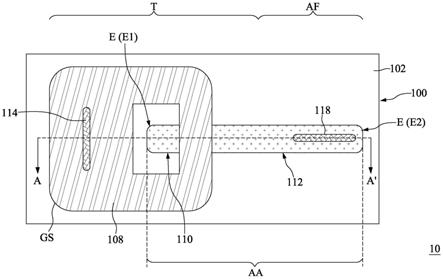

35.图1到图4为依据本公开一些实施例一种半导体元件的剖视示意图。

36.图5为依据本公开一些实施例一种半导体元件的制造方法的流程示意图。

37.图6到图15为依据本公开一实施例在制造该半导体元件的中间阶段的剖视示意图。

38.其中,附图标记说明如下:

39.303:第二隔离层

40.305:第二源极/漏极区

41.307:介电层

42.309:底部电极层

43.311:第一中间电极层

44.313:第二中间电极层

45.315:顶部电极层

46.317:罩盖层

47.319:第一间隙子

48.321:多孔间隙子

49.323:第二间隙子

50.325:气隙间隙子

51.327:轻掺杂区

52.401:第一遮罩层

53.403:衬垫层

54.405:牺牲间隙子

55.3a:半导体元件

56.3b:半导体元件

57.3c:半导体元件

58.3d:半导体元件

59.s31:步骤

60.s33:步骤

61.s35:步骤

62.s37:步骤

63.s39:步骤

64.s41:步骤

65.sgs:堆叠栅极结构

66.w1:宽度

67.w2:宽度

68.z:方向

具体实施方式

69.本公开的以下说明伴随并入且组成说明书的一部分的图式,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

70.「一实施例」、「实施例」、「例示实施例」、「其他实施例」、「另一实施例」等是指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用「在实施例中」一语并非必须指相同实施例,然而可为相同实施例。

71.为了使得本公开可被完全理解,以下说明提供详细的步骤与结构。显然,本公开的实施不会限制该技艺中的技术人士已知的特定细节。此外,已知的结构与步骤不再详述,以免不必要地限制本公开。本公开的较佳实施例详述如下。然而,除了详细说明之外,本公开亦可广泛实施于其他实施例中。本公开的范围不限于详细说明的内容,而是由权利要求定义。

72.应当理解,以下公开内容提供用于实作本发明的不同特征的诸多不同的实施例或实例。以下阐述组件及排列形式的具体实施例或实例以简化本公开内容。当然,该些仅为实例且不旨在进行限制。举例而言,元件的尺寸并非仅限于所公开范围或值,而是可相依于制程条件及/或装置的所期望性质。此外,以下说明中将第一特征形成于第二特征「之上」或第二特征「上」可包括其中第一特征及第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有附加特征、进而使得所述第一特征与所述第二特征可能不直接接触的实施例。为简洁及清晰起见,可按不同比例任意绘制各种特征。在附图中,为简化起见,可省略一些层/特征。

73.此外,为易于说明,本文中可能使用例如「之下(beneath)」、「下面(below)」、「下部的(lower)」、「上方(above)」、「上部的(upper)」等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所绘示的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或

处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

74.在本公开中,半导体元件通常是指可以通过利用半导体特性而起作用的元件,并且电光元件、发光显示元件、半导体电路及电子元件是包括在半导体元件的类别中。

75.应当注意,在本公开描述中,上方(或上)对应于方向z的箭头方向,下方(或下)对应于方向的箭头z的箭头反方向。

76.应当注意,在本公开描述中,沿着方向z位于最高垂直水平的元件(或特征)的表面被称为元件(或表面)的顶表面(特征)。沿着方向z位于最低垂直高度的元件(或特征)的表面称为元件(或特征)的底表面。

77.图1为依据本公开一些实施例一种半导体元件3a的剖视示意图。

78.如图1所示,半导体元件3a具有一半导体基底301、一第二隔离层303、一第二源极/漏极区305、一介电层307、一底部电极层309、一第一中间电极层311、一第二中间电极层313、一顶部电极层315、一罩盖层317、一第一间隙子319、一多孔间隙子321以及一第二间隙子323。

79.参考图1,半导体基底301可为一半导体晶圆,例如一硅晶圆,但并不以此为限。另外或此外,半导体基底301可包括元素(elementary)半导体材料、化合物(compound)半导体材料,及/或合金半导体材料。元素半导体材料的例子可包括晶体硅、多晶硅、非晶硅、锗及/或钻石,但并不以此为限。化合物半导体元件的例子可包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟,及/或锑化铟(indium antimonide),但并不以此为限。合金半导体材料可包括sige、gaasp、alinas、algaas、gainas、gainp,及/或gainasp,但并不以此为限。在一些实施例中,半导体基底301具有一外延层。举例来说,半导体基底301具有一外延层,是铺设在一块状(bulk)半导体上。在一些实施例中,半导体基底301为一绝缘体上覆半导体基底,其是可具有一半导体基底、一埋入式氧化物层以及一半导体层,该埋入式氧化物层是位在该半导体基底上,该半导体层是位在该埋入式氧化物层上,而该绝缘体上覆半导体基底是例如一绝缘体上覆硅(soi)半导体基底、一绝缘体上覆硅锗(sgoi)半导体基底,或绝缘体上覆锗(goi)半导体基底。第二隔离层303可通过常规微影、蚀刻与沉积制程,填入例如氧化物材料或其他合适的绝缘材料形成。第二层隔离层303材料,举例来说,例如氧化硅、氮化硅、氮氧化硅、氧氮化硅和/或掺杂氟化物的硅酸盐,但并不以此为限。

80.仍请参考图1,介电层307是设置在半导体基底301上。且在图1剖视示中,介电层307是一线形。介电层307是由下列材料所制,举例来说,例如氧化硅(sio)、磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)或低介质常数(k)的材料,例如氟硅酸盐玻璃(fsg)、有机硅酸盐玻璃(osg)或其组合,但并不以此为限。

81.仍请参考图1,第二源极/漏极区305是邻近介电层307两端设置,且设置在半导体基底301中。第二源极/漏极区305是通过一或多个离子植入制程所形成,且掺杂物,例如磷、砷、锑或硼,是植入在半导体基底301中,以形成第二源极/漏极区305。第二源极/漏极区掺杂物浓度,其是取决于半导体元件301的导电形态(conductivity type)。

82.仍请参考图1所示,底部电极层309是设置在介电层307上。底部电极层309是由下列材料所制,举例来说,例如多晶硅、多晶硅锗或其组合。在一些实施例中,底部电极层309其是植入掺杂物,例如磷、砷、锑或硼以形成底部电极层309。

83.仍请参考图1,第一中间电极层是设置在底部电极层307上。第一中间电极层311的

厚度是约2nm与约20nm。第一中间电极层311可通过下列材料所制成,举例来说,例如硅化钛、硅化镍、硅化镍铂、硅化钽或硅化钴,但并不以此为限。第一中间电极层311是可做为欧姆接触(ohmic contact),是可减低底部电极层309与顶部电极层315之间的电阻。

84.仍请参考图1,第二中间电极层313是设置在第一中间电极层311上。第二中间电极层313是由下列材料所制,例如氮化钨、氮化钛、氮化钽、类似物或其组合。第二中间电极层313是被构造以在随后的沉积制程中,防止半导体元件3a其他层被降解(degrading)。举例来说,例如在沉积制程期间,或在沉积制程之后,顶部电极层315的一些金属,其是趋于扩散到含硅层(例如底部电极层309)中。

85.仍请参考图1,顶部电极层315是设置在第二中间电极层313上。顶部电极层31513是由下列材料所制,举例来说,例如钨、铝、铜、钛、银、钌、钼以及其他合适金属及/或合金,但并不以此为限。

86.仍请参考图1,罩盖层317是设置在导电层315上。罩盖层317其是由绝缘材料所制成,举例来说,例如氮化硅(sin)或氮氧化硅(sion)的绝缘材料,但并不以此为限。

87.因此,通过介电层307、底部电极层309、第一中间电极层311、第二中间电极层313、顶部电极层315以及罩盖层317,形成一堆叠栅极结构sgs(tacked gate structur)。

88.仍请参考图1,第一间隙子319,是设置在该堆叠栅极结构sgs两侧,且设置在第二源极/漏极区上。在一些实施例中,第一间隙子319,包括例如石墨烯(graphen)材料。在一些实施例中,第一间隙子319,举例来说,是由石墨烯、石墨(graphite)或类似物材料所制。在一些实施例中,第一间隙子319,举例来说,是由具有sp2混成碳原子(hybridized carbonatom)的材料所制。在一些实施例中,第一间隔物319是由具有六方晶体结构的碳所制。由于石墨烯所形成的第一间隔物319其是具有低的薄层电阻(sheet resistance)。所以,具有第一间隙子319的半导体元件3a,其导电性是以提高。

89.仍请参考图1,多孔间隙子321,其是设置在第一间隙子319两侧,且设置在第二源极/漏极区305上。多孔间隙子321是具有约30%与约90%的孔隙率。多孔间隔子321其是可包括一骨架以及多个空隙,且该多个空隙是设置在该骨架之间。多个空隙是彼此连接,且可被空气填满。该骨架是可包括,举例来说,例如氧化硅、低介电材料或甲基倍半硅氧烷(methylsilsesquioxane)。多孔间隔子321的多个空隙是可充满空气。因此,多孔间隙子321其介电常数是可低于,例如通过氧化硅,所制的一氧化硅层的介电常数。因此,多孔间隙子321是可降低半导体元件3a的寄生电容。由于多孔间隙子321的设置,因此降低电子讯号之间的干扰效应(通过感应或施加到半导体元件3a)。

90.仍请参考图1,第二间隙子323,其是设置在多孔间隙子321两侧,且设置在第二源极/漏极区305上。第二间隙子323是由下列材料所制,例如氮化硅、氧化硅、氮氧化硅、氮氧化硅、类似物及/或其组合。第二间隙子323是可电绝缘该堆叠栅极结构sgs与相邻的导电元件之间的电连接,且可保护多孔间隙子321以及第一间隙子319。

91.图2到图4为依据一些实施例半导体元件3b、3c以及3d的剖视示意图。

92.如图2所示,半导体元件3b,其是可类似于图1所示的半导体元件3a的结构。图2中,相同于或类似于图1的元件是用相同的符号表示,且在文中不再重复其详细描述。

93.请参考图2,介电层307的宽度w1是可大于底部电极层309的宽度w2。第一间隙子319是可设置在介电层307上。第一间隙子319是可被介电层307电隔离,是隔离第一间隙子

319与第二源极/漏极之间的电连接。

94.请参考图3,半导体元件3c,其是可类似于图1所示的半导体元件3a的结构。图3中,相同于或类似于图1的元件是用相同的符号表示,且在文中不再重复其详细描述。

95.请参考图1及图3,图1所示的多孔间隙子321是可具有100%的孔隙率。意即,多孔间隙子321仅具有一空隙。因此,图1所示的多孔间隙子321是可当成图3所示的气隙间隙子325。气隙间隙子325的介电常数是为1.0,其是可降低堆叠栅极结构sgs与水平相邻导电元件之间的寄生电容。

96.请参考图4,半导体元件3d,其是可类似于图1所示的半导体元件3a的结构。图4中,相同于或类似于图1的元件是用相同的符号表示,且在文中不再重复其详细描述。

97.仍请参考图4,半导体元件3d,其是可具有轻度掺杂区327。轻度掺杂区327是可分别对应地形成在邻近介电层307的各端,且设置在半导体基底301中。第一间隙子319是可设置在轻度掺杂区327上。第二源极/漏极区305是可邻近轻度掺杂区327设置。轻度掺杂区327是可掺杂,例如磷、砷、锑或硼的掺杂剂。轻度掺杂区327的掺杂剂浓度是可小于第二源极/漏极区305的掺杂剂浓度。通过轻度掺杂区327,是可减低热载子效应(hot-carrier effect)。

98.图5为依据本公开一些实施例一种半导体元件3a的制备方法30的流程示意图。图6到图15为依据一些实施例形成半导体元件3a的各中间阶段的剖视示意图。

99.参考图5及图6到图9,如图9所示,一堆叠栅极结构sgs设置在半导体基底301上,该堆叠栅极结构sgs具有一介电层307、一底部电极层309、一第一中间电极层311、一第二中间电极层313、一顶部电极层315以及一罩盖层317。对应的步骤是绘示在如图5所示的方法30中的步骤s31。

100.请参考图6,如图1所示,第二隔离层303可通过常规微影、蚀刻与沉积制程,填入例如氧化物材料或其他合适的绝缘材料形成。在一些实施例中,一图案化遮罩(未绘示),是形成在半导体基底301上,隔离层是通过使用该图案化遮罩当作一遮罩,以使第二层隔离的部份暴露。通过例如一湿蚀刻制程、一干蚀刻制程或其组合形成一凹槽(未绘示)。在凹槽中沉积隔离材料,例如氧化硅以形成隔离层303。在一些实施例中,介电层307是由一化学气相沉积(cvd)制程、一原子层沉积(ald)制程形成在半导体基底301上。在一些实施例中,介电层307是由氧化制程所形成。底部电极层309是通过cvd制程或其他适合的沉积制程形成在介电层307上。

101.请参考图7,是可在图6所示的中间半导体元件上形成一电极材料层。电极材料层是可包括下列材料:例如钛,镍,铂,钽及/或钴。然后,进行一热处理制程。在该热处理制程期间,该电极材料层的金属原子与底部电极层309的硅原子是以进行化学反应,形成一第一中间电极层311。第一中间导电层311可包括硅化钛、硅化镍、镍铂硅化物、硅化钽或硅化钴。该热处理制程是可是一动态表面退火(dynamic surface annealing)制程。在该热处理制程之后,是可执行一清洁制程以便移除未反应的电极材料。该清洁制程是可使用蚀刻剂,例如过氧化氢以及sc-1溶液。

102.请参考图8,是可以进行一系列的沉积制程,其是依次沉积第二中间电极层313、顶部电极层315、罩盖层317以及一第一遮罩层401。该一系列沉积制程是可包括一cvd制程、一等离子体增强cvd制程、一ald制程、一pvd制程、一喷溅制程或一镀覆制程。第一遮罩层401

是可被图案化,以定义堆叠栅极结构sgs的位置处。

103.请参考图9,是可执行一蚀刻制程以移除罩盖层317、顶部电极层315、第二中间电极层313、第一中间电极层311、底部电极层309以及介电层307未被堆叠栅极结构sgs的位置所定义的部份。在堆叠栅极结构sgs的位置处上的顶部电极层315、第二中间电极层313、第一中间电极层311、底部电极层309以及介电层307结合形成堆叠栅极结构sgs。

104.请参考图5及图10,是可在半导体基底301中形成一第二源极/漏极区305。对应的步骤是绘示在如图5所示的方法30中的步骤s33。

105.如图10所示,第二源极/漏极区305是形成在邻近介电层307的两端,且在半导体基底301中。第二源极/漏极区305形成的制程请往回参考图1所描述,在文中不再重复其详细描述。然后,是可进行一退火(annealing)制程,以加强第二源极/漏极区305掺杂离子的均匀度。该退火制程是可具有大约800℃与大约1250℃的制程温度。该退火制程是可具有大约1毫秒与大约500毫秒的制程时间。该退火制程是可包括,例如快速热退火制程、激光尖峰退制程以及闪光灯退火。

106.请参考图5、图11及图12,第一间隙子319,其是设置在堆叠栅极结构sgs两侧。对应的步骤是绘示在如图5所示的方法30中的步骤s35。

107.如图11所示,一衬垫层403是可被形成,以覆盖半导体基底301的顶表面以及堆叠栅极结构sgs。衬垫层403是为一第一电极材料层。在一些实施例中,该第一电极材料层是以包括例如石墨烯的材料形成。在一些实施例中,该第一电极材料层是以下列材料,包括例如石墨烯、石墨或类似的材料形成。在一些实施例中,该第一电极材料层是可由具有sp2混成碳原子的材料形成。在一些实施例中,该第一电极材料层是可由具有六方晶格结构碳的材料形成。

108.在一些实施例中,该第一电极材料层是可形成在一催化剂半导体基底上。然后,再将该第一电极材料层转移到图10所示的中间半导体元件上。该催化剂半导体基底是可包括镍、铜、钴、铂、银、钌、铱、钯、铁镍合金、铜镍合金、镍钼合金、金镍合金以及/或钴铜合金。

109.在一些实施例中,该第一电极材料层是可通过催化剂形成。催化剂是可为下列材料:单晶/或多晶金属、二元合金或液态金属。举例来说,单晶或多晶金属可例如镍、铜、钴、铂、银、钌、铱及/或钯。举例来说,二元合金是可为下列合金:铁镍合金、铜镍合金、镍钼合金、金镍合金以及钴铜合金。举例来说,液态金属是可为液态镓、液态铟及/或液态铜。

110.请参考图12,是可进行一蚀刻制程(间隙子蚀刻)以形成第一间隙子319。蚀刻制程可为一非等向性蚀刻制程,其是进行其是垂直移除在所有位置处的相同数量的第一电极材料,并留下第一间隙子319。

111.请参考图5及图13,牺牲间隙子405是可形成在第一间隙子319侧壁上。对应的步骤是绘示在如图5所示的方法30中的步骤s37。

112.请参考图13,是可在图12所示的中间半导体元件上形成一可移除能量的材料层。可移除能量的材料是可包括下列材料,例如热可分解材料、光子可分解材料、电子束可分解材料及/或其组合的材料。举例来说,可移除能量的材料是可包括一基础材料及一可分解致孔剂(decomposable porogen material)材料,其是在暴露于能量源时被移除。该基础材料是可包括甲基硅氧烷(methylsilsesquioxane,msq)。该可分解致孔剂材料是可包括一致孔有机化合物(porogen organic compound)。该致孔有机化合物是为该可移除能量的材料的

该基础材料进行反应,以形成孔隙。然后,可移除能量的材料层可以一非等向性蚀刻制程进行蚀刻,其是垂直移除在所有位置处的相同数量的可移除能量的材料,并留下牺牲间隙子405在第一间隙子319侧壁上。

113.请参考图5及图14,第二间隙子323是可形成在牺牲间隙子405的侧壁上。对应的步骤是绘示在如图5所示的方法30中的步骤s39。

114.如图14所示,一绝缘材料层是可被形成在图13所示的该中间半导体元件上。该绝缘材料层的材料是可下列材料:例如氮化硅、氧化硅、氮氧化硅、氮氧化硅、类似材料及/或其组合。然后,该绝缘材料层可以一非等向性蚀刻制程进行蚀刻,其是垂直移除在所有位置处的相同数量的绝缘材料层的材料,并留下第二间隙子323在牺牲间隙子405侧壁上。

115.请参考图5及图15,一能量处理制程被执行在牺牲间隙子405上。因此,牺牲间隙子405被形成为多孔间隙子物321。对应的步骤是绘示在如图5所示的方法30中的步骤s41。

116.如图15所示,一能量被加到图14所示的中间半导体元件上,引起牺牲间隙子405进行反应,牺牲间隙子405被形成多孔间隙子物321。在反应后,形成具有堆叠栅极结构sgs的半导体元件3a。该能量源可以包括热、光及/或其组合。当热是能量源时,能量处理的温度是为大约800℃与大约900℃。当光是能量源时,可使用一紫外线。能量处理制程是可移除该能量的材料的可分解的致孔剂材料,形成空隙(空孔),且基础材料保留在原位。在能量处理之后,是可牺牲间隙子405形成多孔间隙子321。

117.本公开的一实施例提供一种半导体元件。该半导体元件具有一埋入介电层,设置在该半导体基底中。该半导体元件亦具一埋入导电层,具有一下部及一上部。该下部设置在该埋入介电层上,该上部设置在该下部上。该半导体元件亦具有一罩盖层,设置在该罩盖层与该介电层之间,且设置在该埋入导电层上部与该介电层之间。该埋入导电层是具有石墨烯。

118.由于本公开的半导体元件设计,埋入导电层113其总横截面积是以通过埋入导电层113上部113-3而增加。结合具有石墨烯的埋入导电层113的良好导电性,可以改善半导体元件1a的导电性和效能。再者,埋入罩盖层111是可防止半导体元件1a在制造中形成空隙。所以,半导体元件1a其可制性是以提高。

119.本公开的一实施例提供一种半导体元件。该半导体元件具有一半导体基底,一堆叠栅极结构,一第一间隙子以及一第二间隙子,该堆叠栅极结构设置在该半导体基底上,该第一间隙子设置在该堆叠栅极结构两侧,该第二间隙子设置在该第一间隙子两侧,其中该第一间隙子具有一石墨烯(graphene)。

120.本公开的另一实施例提供一种半导体元件的制备方法,包括:提供一半导体基底;形成一堆叠栅极结构在该半导体基底上;形成一第一间隙子在该堆叠栅极结构侧壁上,其中该第一间隙子包括石墨烯;形成一牺牲间隙子在该第一间隙子侧壁上;以及形成一第二间隙子在该牺牲间隙子侧壁上。

121.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

122.再者,本技术案的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本

公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本技术案的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。