1.本发明涉及半导体存储器测试技术领域,具体涉及一种铁电存储器耐久性测试的电路和方法。

背景技术:

2.目前,新型非易失性存储器主要包括铁电存储器(feram)、相变存储器(pcram)、磁阻存储器(stt-mram)、阻变存储器(rram)等。其中,铁电存储器的存储机制是利用铁电材料在外加电场的作用下具有极化的特性实现二值存储。合格的铁电存储器产品要求保证抗疲劳次数达到10

12

次以上,达到无限寿命要求的理想存储器则需经受至少10

15

次的极化翻转,且所保存的数据至少10年不会挥发。因此对铁电存储器的测试便提出了相应的要求。

3.传统的耐久性测试,是通过进行写入读出、再写入再读出......如此反复循环操作,对每次读出数据进行判断,并记录读写周期次数,从而测试feram产品的反复读写和数据保存能力的可靠性。这是一个非常耗时的过程,测试时间长,效率低,成本高,不利于产业化发展。因此需要设计一种较为灵活的、低成本的耐久性测试电路与方法,区别于传统耐久测试流程,能够有效缩短测试时间,从而提升测试效率,降低成本,加速获得铁电存储器产品的耐久性评估数据。

4.研究学者们对铁电薄膜的疲劳失效现象进行了探究,研究结果表明:铁电薄膜的疲劳往往也伴随着漏电流的增大,体电阻率的降低,这可以归因于疲劳导致的薄膜体内的氧空位数量随疲劳进程急剧增大。利用这一电学特性,本发明提出一种基于监测铁电存储器位线上漏电流变化、有效减小耐久性测试时间的测试电路和方法。

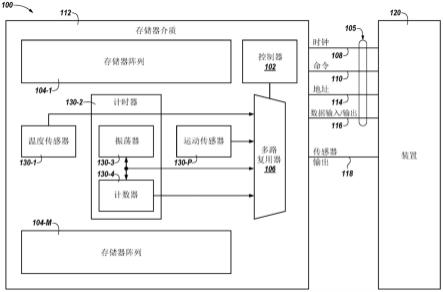

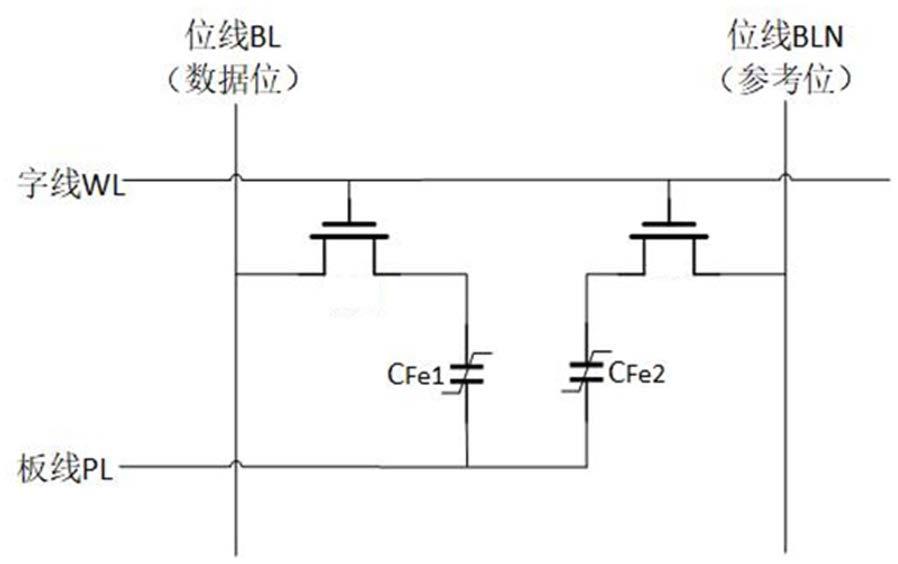

5.这里介绍常见的铁电存储器结构,其基本存储单元一般有两种结构:单管单电容(1t1c型)和双管双电容(2t2c型),如图1a和图1b所示,前者使用一个晶体管及一个铁电电容组成一个存储单元,后者则各为两个。其中,wl(wordline)为字线,连接到晶体管栅极;bl(bitline)、bln分别为数据位和参考位的位线;pl(plateline)为板线;cfe1和cfe2为铁电电容,其一极连接至pl,另一极分别与晶体管相连,当wl开启时,这一极便与bl或bln相连。本发明可适用于两种结构的铁电存储器耐久性测试。

技术实现要素:

6.为了解决现有技术中存在的上述技术问题,本发明提出了一种加速铁电存储器耐久性测试的电路和方法,极大地减少了铁电存储器的耐久性测试时间成本,其具体技术方案如下:一种加速铁电存储器耐久性测试的电路,包括依次连接的pmos晶体管p1、nmos晶体管n1、恒流源电路,所述pmos晶体管p1的源极连接有电源vdd;pmos晶体管p1的漏极和nmos晶体管n1的漏极相连接,在pmos晶体管p1和nmos晶体管n1的连接间节点设有监测电压点vout;nmos晶体管n1的源极连接至恒流源电路的一端,恒流源电路的另一端接地;nmos晶体管n1和恒流源电路的连接间节点与铁电存储器的位线bl连接;在pmos晶体管p1和nmos晶

体管n1的栅极分别输入电压vbias1和电压vbias2。

7.进一步地,所述电压vbias1为pmos晶体管p1提供栅极偏置电压,电压vbias2为nmos晶体管n1提供栅极偏置电压,使得pmos晶体管p1和nmos晶体管n1都工作在饱和区。

8.进一步地,所述pmos晶体管p1工作在饱和区,饱和区电流公式为:,即流经pmos晶体管p1的支路电流为;其中,表示空穴迁移率,表示宽长比,表示单位面积的栅氧化层电容,表示阈值电压,表示栅、源极电压差;当减小,由饱和区电流公式可以推出,减小,即pmos晶体管p1的源、漏极电压差减小,则电压监测点vout处电压升高。

9.进一步地,所述恒流源电路为到地回路,提供恒定的电流,所述恒定的电流由两路支路的电流构成,所述两路支路分别为恒流源电路连接pmos晶体管p1和nmos晶体管n1的支路、恒流源电路连接铁电存储器位线bl的支路;当铁电存储器中的铁电电容呈现疲劳失效时,铁电电容的体电阻率降低,漏电流增大,即恒流源连接位线bl的支路电流增大,同时恒流源连接pmos晶体管p1和nmos晶体管n1的支路电流减小。

10.进一步地,所述恒流源电路为带隙基准结构,具体包括pmos晶体管p2~pmos晶体管p10,nmos晶体管n2~ nmos晶体管n6,电阻r1~电阻r3,双极型晶体管q0,三极管q1~三极管qn,n为大于1的整数,运放opa;所述恒流源电路为带隙基准结构,具体包括pmos晶体管p2~pmos晶体管p10,nmos晶体管n2~ nmos晶体管n6,电阻r1~电阻r3,双极型晶体管q0,三极管q1~三极管qn,运放opa;所述pmos晶体管p2、p3串联后与nmos晶体管n3的漏极连接,其中pmos晶体管p2的漏极与其栅极相连接,pmos晶体管p3的漏极与其栅极相连接;pmos晶体管p4、p5串联后与双极型晶体管q0的集电极连接;pmos晶体管p6、p7串联后通过电阻r2与三极管q1的集电极连接;pmos晶体管p8、p9串联后与nmos晶体管n4的漏极连接;pmos晶体管p10的源极与pmos晶体管p1、p2、p4、p6、p8的源极均连接至电源vdd,栅极均连接至pmos晶体管p1的栅极;pmos晶体管p3、p5、p7、p9的栅极相连接;nmos晶体管n6的源极连接nmos晶体管n5的漏极,nmos晶体管n6的漏极和栅极均连接至pmos晶体管p10的漏极,nmos晶体管n1的栅极连接nmos晶体管n6的栅极;nmos晶体管n5的栅极与nmos晶体管n4的栅极均连接至nmos晶体管n2的栅极,nmos晶体管n2、n4、n5的源极相连接后接地,其中,nmos晶体管n4的漏极与栅极连接;三极管q1~三极管qn并联连接后一端接电阻r2的一端,另一端 与电阻r3的一端连接后接地;电阻r3的另一端与电阻r2的另一端连接后接入运放opa的反相输入端;双极型晶体管q0的基极与其集电极、电阻r1的一端相连接后接入运放opa的同相输入端;双极型晶体管q0的发射极与电阻r1的另一端、nmos晶体管n3的源极相连接后接地;nmos晶体管n3的栅极连接至运放opa的输出端。

11.进一步地,所述pmos晶体管p2、p4、p6、p8、p10的尺寸与pmos晶体管p1一致,pmos晶体管p3、p5、p7、p9的尺寸一致,nmos晶体管n6和nmos晶体管n1尺寸一致,nmos晶体管n4、n5和nmos晶体管n2尺寸一致;电阻r1和电阻r3相同;三极管q1~三极管qn尺寸一致。

12.进一步地,基于所述恒流源电路为带隙基准结构,流经pmos晶体管p10和nmos晶体管n6的支路电流=,其中,r0表示电阻r1的阻值,与电阻r3相同;v

be

是双极型晶体管q0的发射极偏压,呈负温度特性;vt是与温度呈正相关的参数,三极管q1~三极管qn是尺寸一致的三极管,等效于n个三极管q1并联,通过设置n值,使得正温度系数与负温度系数相互抵消,从而产生和温度无关的基准电流,所述基准电流被镜像到nmos晶体管n2所在支路,为所在支路提供恒流源。

13.进一步地,还包括报警电路,所述报警电路由比较器和报警器组成,将电压监测点vout电压输入比较器,与比较器的参考基准电压进行比较,后将比较的结果反馈给报警器,实现报警。

14.进一步地,所述监测电压点vout电压与比较器的参考基准电压进行比较,超过参考基准电压时,报警器报警,表示铁电存储器的位线bl漏电流变大;再对铁电存储器进行读出操作,若读出数据正确,则提高比较器的参考基准电压,再进行下一周期的写入操作;若读出数据有误,则记录目前为止反复写入的周期数,获得耐久性测试数据。

15.一种采用所述的加速铁电存储器耐久性测试的电路进行加速铁电存储器耐久性测试的方法,包括以下步骤:步骤1:在耐久性测试之前对铁电存储器的初始数据进行读出,以确定起始向铁电存储器写入的数据是1还是0;若初始数据读出为1,则耐久性测试第一次写入数据0;若初始数据读出为0,则耐久性第一次写入数据为1;步骤2:开始耐久性测试,对铁电存储器进行反复写入操作,下一次总是写入上一次数据的取反值,使得铁电存储器的铁电电容每次进行极化翻转;步骤3:在耐久性测试期间,报警电路对监测电压点vout电压进行实时监测,若报警电路出现报警,此时对铁电存储器进行数据读出;若报警电路没有出现报警,则继续对铁电存储器进行耐久性测试,进行反复写入操作;步骤4:报警电路出现报警后,对铁电存储器的读出数据进行判断;若读出数据有误,则记录目前为止对铁电存储器反复写入的周期数,获取耐久性评估参数,即失效周期数;若读出数据正确,则说明报警电路报警异常,调整报警电路的参考基准电压,继续进行耐久性测试,直到读出数据真实有误,记录最后使铁电存储器失效的周期数。

16.有益效果:本发明提供了一种加速铁电存储器耐久性测试的电路和方法,无需像传统耐久性测试那样对铁电存储器进行每次写入每次读出数据进行对比,大大减少了耐久性测试中读出操作的次数,有效节约了测试时间成本,只需对铁电存储器进行反复写入,等待报警电路出现报警,记录最后使铁电存储器失效的周期数,即获得待测器件的耐久性评估参数;对比传统耐久性测试流程,本发明极大地加快了耐久性参数的获取,加速铁电产品的面市周期。

附图说明

17.图1a为常见的单管单电容1t1c型的铁电存储器结构示意图;图1b为常见的双管双电容2t2c型的铁电存储器结构示意图;图2为本发明提供的加速铁电存储器耐久性测试的电路图;

图3为本发明采用的报警电路的示意图;图4为使本发明测试电路的电压监测点vout电压随位线bl漏电流变化更为灵敏的电路示意图;图5为本发明提供的加速铁电存储器耐久性测试的方法流程图;图6为本发明实施例的恒流源电路图。

具体实施方式

18.为了使本发明的目的、技术方案和技术效果更加清楚明白,以下结合说明书附图,对本发明作进一步详细说明。

19.为了有效缩小铁电存储器的耐久性测试时间成本,加速获取耐久性评估参数,提升测试效率,加快铁电产品的面市周期,本发明设计一种加速铁电存储器耐久性测试的电路,如图2所示,包括依次连接的pmos晶体管p1、nmos晶体管n1、恒流源电路,电源vdd连接至pmos晶体管p1的源极;pmos晶体管p1的漏极和nmos晶体管n1的漏极相连接,在pmos晶体管p1和nmos晶体管n1的连接间节点设有监测电压点vout,以监测该支路路径的电流变化;nmos晶体管n1的源极连接至恒流源电路的一端,恒流源电路的另一端接地;nmos晶体管n1和恒流源电路的连接间节点与铁电存储器的位线bl连接;在pmos晶体管p1和nmos晶体管n1的栅极分别输入电压vbias1和电压vbias2。

20.本发明适用于两种常见的铁电存储器结构,如图1a和图1b所示,分别是:单管单电容(1t1c型)和双管双电容(2t2c型)。

21.所述vbias1电压为pmos晶体管p1提供栅极偏置电压,vbias2电压为nmos晶体管n1提供栅极偏置电压,使得pmos晶体管p1和nmos晶体管n1都工作在饱和区。

22.所述恒流源电路为到地回路,提供恒定的电流,该电流由两路支路电流构成,分别为恒流源电路连接pmos晶体管p1和nmos晶体管n1的支路、恒流源电路连接铁电存储器单元位线bl的支路;当铁电电容呈现疲劳失效时,铁电电容的体电阻率降低,漏电流增大,即该测试电路中所连接位线bl的支路电流增大。由于两支路之和为恒定电流源,一支路电流增大,另一支路电流减小,即所连接至两个晶体管的支路电流减小。

23.所述pmos晶体管p1工作在饱和区,饱和区电流公式为:,即流经pmos晶体管p1的支路电流为;其中,表示空穴迁移率,表示宽长比,表示单位面积的栅氧化层电容,表示阈值电压,表示栅、源极电压差;减小,由公式可以推出,v

ds

减小,即pmos晶体管p1的源、漏极电压差减小,则电压监测点vout处电压升高。

24.在传统的铁电存储器耐久性测试中,对铁电存储器进行反复写入读出,每次写入每次读出,持续判断读出数据的正确与否,当读出数据有误时则认为铁电电容疲劳失效,这种传统测试方法消耗很长的测试时间,测试成本极高。

25.本发明规定在耐久性测试中只需要对铁电存储器进行反复写入,而无需每次读出。在持续写入的过程中对电压监测点vout电压进行实时监测,将电压监测点vout电压与

比较器的参考基准电压进行比较,输出比较结果,再将比较结果反馈给报警器,实现报警,如图3所示。当监测电压超过参考基准电压时,报警器报警,代表铁电存储器的位线bl漏电流变大,这时再对铁电存储器进行读出操作,若读出数据正确,可以适当提高报警电路比较器的参考基准,再进行下一周期的写入操作;若读出数据有误,则记录目前为止反复写入的周期数,获得耐久性测试数据。

26.为使本发明测试电路的电压监测点vout电压随位线bl漏电流变化更为灵敏,设置加入多级的pmos晶体管和nmos晶体管,如图4所示。

27.所述恒流源电路为带隙基准结构,具体的,如图6所示,包括pmos晶体管p2~pmos晶体管p10,nmos晶体管n2~ nmos晶体管n6,电阻r1~电阻r3,双极型晶体管q0,三极管q1~三极管qn,n为大于1的整数,运放opa。

28.所述pmos晶体管p2、p3串联后与nmos晶体管n3的漏极连接,其中pmos晶体管p2的漏极与其栅极相连接,pmos晶体管p3的漏极与其栅极相连接;pmos晶体管p4、p5串联后与双极型晶体管q0的集电极连接;pmos晶体管p6、p7串联后通过电阻r2与三极管q1的集电极连接;pmos晶体管p8、p9串联后与nmos晶体管n4的漏极连接;pmos晶体管p10的源极与pmos晶体管p1、p2、p4、p6、p8的源极均连接至电源vdd,栅极均连接至pmos晶体管p1的栅极;pmos晶体管p3、p5、p7、p9的栅极相连接;nmos晶体管n6的源极连接nmos晶体管n5的漏极,nmos晶体管n6的漏极和栅极均连接至pmos晶体管p10的漏极,nmos晶体管n1的栅极连接nmos晶体管n6的栅极;nmos晶体管n5的栅极与nmos晶体管n4的栅极均连接至nmos晶体管n2的栅极,nmos晶体管n2、n4、n5的源极相连接后接地,其中,nmos晶体管n4的漏极与栅极连接;三极管q1~三极管qn并联连接后一端接电阻r2的一端,另一端 与电阻r3的一端连接后接地;电阻r3的另一端与电阻r2的另一端连接后接入运放opa的反相输入端;双极型晶体管q0的基极与其集电极、电阻r1的一端相连接后接入运放opa的同相输入端;双极型晶体管q0的发射极与电阻r1的另一端、nmos晶体管n3的源极相连接后接地;nmos晶体管n3的栅极连接至运放opa的输出端。

29.基于电流镜和运放opa电路的工作原理,可以推导得到,流经pmos晶体管p10和nmos晶体管n6的支路电流=。其中,电阻r1和电阻r3相同,阻值等于r0。v

be

是双极型晶体管q0的发射极偏压,呈负温度特性。由于vt是一个与温度呈正相关的参数,三极管q1~三极管qn是尺寸一致的三极管,等效于n个三极管q1并联,通过设置n的值,使得正温度系数与负温度系数相互抵消,从而可以产生和温度无关的基准电流。

30.所述基准电流被镜像到nmos晶体管n2所在支路,为其提供恒流源。

31.在所述恒流源电路中,晶体管p2、p4、p6、p8、p10均是与晶体管p1尺寸一致的pmos晶体管,p3、p5、p7、p9是尺寸一致的pmos晶体管。晶体管n6是和晶体管n1尺寸一致的nmos晶体管,晶体管n4、n5和n2是尺寸一致的nmos晶体管。图6中晶体管均工作在饱和区。

32.如图5所示,一种加速铁电存储器耐久性测试的方法,包括以下步骤:步骤1:在耐久性测试之前对铁电存储器的初始数据进行读出,以确定起始向铁电存储器写入的数据是1还是0。若初始数据读出为1,则耐久性测试第一次写入数据0;若初始数据读出为0,则耐久性第一次写入数据为1。

33.步骤2:开始耐久性测试,对铁电存储器进行反复写入操作,下一次总是写入上一次数据的取反值,使得铁电存储器的铁电电容每次进行极化翻转。

34.步骤3:在耐久性测试期间,报警电路对监测电压点vout电压进行实时监测,若报警电路出现报警,此时对铁电存储器进行数据读出;若报警电路没有出现报警,则继续对铁电存储器进行耐久性测试,进行反复写入操作。

35.步骤4:报警电路出现报警后,对铁电存储器的读出数据进行判断;若读出数据有误,则记录目前为止对铁电存储器反复写入的周期数,获取耐久性评估参数,即失效周期数;若读出数据正确,说明报警电路报警异常,需要适当调整报警电路的参考基准,继续进行耐久性测试,直到读出数据真实有误,记录最后使铁电存储器失效的周期数。

36.以上所述,仅为本发明的优选实施案例,并非对本发明做任何形式上的限制。虽然前文对本发明的实施过程进行了详细说明,对于熟悉本领域的人员来说,其依然可以对前述各实例记载的技术方案进行修改,或者对其中部分技术特征进行同等替换。凡在本发明精神和原则之内所做修改、同等替换等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。