一种应用于sar adc的高速动态并行逻辑电路

技术领域

1.本发明属于模拟电路设计技术领域,具体涉及一种应用于sar adc的高速动态并行逻辑电路。

背景技术:

2.如图1所示,传统异步sar adc逻辑时序图中,一个转换周期由比较器延时、逻辑延时、dac建立延时组成,其中比较器延时有比较器的速度决定,dac建立延时由驱动开关和电容大小决定。dac的建立需要在sar adc逻辑产生位选信号的逻辑延时之后进行,因此一个转换周期的时间被延长,减慢了速度。

技术实现要素:

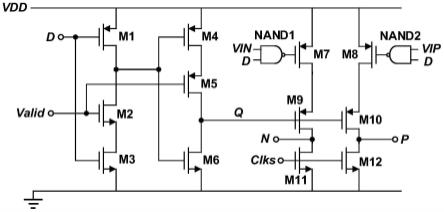

3.针对上述问题,本发明提出了一种并行的sar adc控制逻辑,如图2所示。本发明dac 的建立过程在比较器得出结果之后立即进行,从而省去了逻辑延时,缩短了一个转换器周期所需要的时间,提高了整体转换速度。

4.本发明通过产生为位选关断信号代替传统的sar adc逻辑的位选导通信号,当dac完成建立之后,将当前位的控制通路关断,使得后续的比较对前一位的电容翻转控制信号不产生影响。而通过位选关断信号依次的变为高电平输入给下一级的控制逻辑,使得下一级的控制通过依次使能。

5.本发明采取的技术方案是:包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10、第十一晶体管m11、第十二晶体管m12、第一与非门nand1、第二与非门nand2,其中

6.第一晶体管m1的源极接电源vdd,漏极接自身的第二晶体管m2的漏极、第四晶体管 m4和第六晶体管m6的栅极,栅极接第一控制信号d;

7.第二晶体管m2的源极与第三晶体管m3的漏极连接,漏极接第一晶体管m1的漏极,栅极接第二控制信号valid和第五晶体管m5的栅极;

8.第三晶体管m3的源极接地,漏极接第二晶体管m2的源极、栅极接第一控制信号d;

9.第四晶体管m4的源极接电源vdd,漏极接第五晶体管m5的源极,栅极接第六晶体管 m6的栅极、第一晶体管m1和第二晶体管m2的漏极;

10.第五晶体管m5的源极接第四晶体管m4的漏极,漏极接第三输出信号q且接第六晶体管m6的漏极、第九晶体管m9和第十晶体管m10的栅极,栅极接第二控制信号valid和第二晶体管m2的栅极;

11.第六晶体管m6的源极接地,漏极接第三输出信号q,栅极接第四晶体管m4的栅极、第一晶体管m1和第二晶体管m2的漏极;

12.第七晶体管m7的源极接电源vdd,漏极接第九晶体管m9的源极,栅极接第一与非门 nand1的输出;

13.第八晶体管m8的源极接电源vdd,漏极接第十晶体管m10的源极,栅极接第二与非门nand2的输出;

14.第九晶体管m9的源极接第七晶体管m7的漏极,漏极接第十一晶体管m11的漏极和第一输出信号n;栅极接第五晶体管m5和第六晶体管m6的漏极且连接第三输出信号q;

15.第十晶体管m10的源极接第八晶体管m8的漏极,漏极接第十二晶体管m12的漏极和第二输出信号p;栅极接第五晶体管m5和第六晶体管m6的漏极且连接第三输出信号q;

16.第十一晶体管m11的源极接地,漏极接第九晶体管m9的漏极和第一输出信号n,栅极接第三控制信号clks;

17.第十二晶体管m12的源极接地,漏极接第十晶体管m10的漏极和第二输出信号p,栅极接第三控制信号clks;

18.第一与非门nand1的输入接第一输入信号vin和第一控制信号d,输出接第七晶体管 m7的栅极;

19.第二与非门nand2的输入接第二输入信号vip和第一控制信号d,输出接第八晶体管 m8的栅极;

20.第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5和第六晶体管m6组成动态d触发器,其触发输入信号为第一控制信号d,时钟驱动信号为第二控制信号valid,第二控制信号valid由比较器的输出端通过或门产生,一旦比较器的输出有效,valid信号变为高电平,否则为低电平。动态d触发器的作用是产生位选关断功能和为下一级并行逻辑提供触发信号,当第二控制信号valid从高电平跳变为低电平时,第三输出信号q被拉高,使得第九晶体管m9和第十晶体管m10不导通,以此来保证之后的比较器输出结果不影响前一位电容的翻转,实现了位不选的功能。

21.第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10、第十一晶体管 m11、第十二晶体管m12、第一与非门nand1、第二与非门nand2组成电容翻转逻辑。其中第一输入信号vin和第二输入信号vip分别接比较器的正向输出端和反向输出端,第一控制信号d为上一位电容控制逻辑产生的第三输出信号q;n和p分别为第一输出信号和第二输出信号,接组合逻辑分别控制差分电容阵列的正端和负端相应位电容翻转;第三控制信号 clks为采样信号,用来将第一输出信号n和第二输出信号p复位至地。

22.本发明的有益效果为,本发明电路产生拥有高速、并行、低功耗的特点。传统的异步saradc逻辑需要等待位选信号到来之后再去进行电容翻转,接着进行下一次比较,产生位选的逻辑延时使得两次比较间隙延长,这减慢了sar adc可运行的最高速度,限制了sar adc 的采样率。本发明采用并行逻辑控制电容阵列的翻转,当比较器得到比较结果之后,立即产生电容翻转信号,避免了通过先产生位选信号再翻转,有效的解决了传统异步sar adc逻辑受到逻辑延迟导致的速度受限的缺点。

附图说明

23.图1为传统的sar adc控制逻辑的时序图;

24.图2为本发明的应用于sar adc的高速动态并行逻辑电路;

25.图3为利用本发明的高速动态并行逻辑电路构成的6位sar adc控制逻辑实例;

26.图4为利用本发明的高速动态并行逻辑电路构成的6位sar adc控制逻辑实例的时

序图;

具体实施方式

27.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图、和具体实施方式进行详细地说明。

28.本发明应用于sar adc的高速动态并行逻辑电路,包括第一晶体管m1、第二晶体管 m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10、第十一晶体管m11、第十二晶体管m12、第一与非门nand1、第二与非门nand2,其中,第一晶体管m1的源极接电源vdd,漏极接自身的第二晶体管m2的漏极、第四晶体管m4和第六晶体管m6的栅极,栅极接第一控制信号d;第二晶体管m2的源极与第三晶体管m3的漏极连接,漏极接第一晶体管m1 的漏极,栅极接第二控制信号valid和第五晶体管m5的栅极;第三晶体管m3的源极接地,漏极接第二晶体管m2的源极、栅极接第一控制信号d;第四晶体管m4的源极接电源vdd,漏极接第五晶体管m5的源极,栅极接第六晶体管m6的栅极、第一晶体管m1和第二晶体管m2的漏极;第五晶体管m5的源极接第四晶体管m4的漏极,漏极接第三输出信号q且接第六晶体管m6的漏极、第九晶体管m9和第十晶体管m10的栅极,栅极接第二控制信号 valid和第二晶体管m2的栅极;第六晶体管m6的源极接地,漏极接第三输出信号q,栅极接第四晶体管m4的栅极、第一晶体管m1和第二晶体管m2的漏极;第七晶体管m7的源极接电源vdd,漏极接第九晶体管m9的源极,栅极接第一与非门nand1的输出;第八晶体管m8的源极接电源vdd,漏极接第十晶体管m10的源极,栅极接第二与非门nand2的输出;第九晶体管m9的源极接第七晶体管m7的漏极,漏极接第十一晶体管m11的漏极和第一输出输出信号n;栅极接第五晶体管m5和第六晶体管m6的漏极且连接第三输出第三输出信号q;第十晶体管m10的源极接第八晶体管m8的漏极,漏极接第十二晶体管m12的漏极和第二输出信号p;栅极接第五晶体管m5和第六晶体管m6的漏极且连接第三输出信号q;第十一晶体管m11的源极接地,漏极接第九晶体管m9的漏极和第一输出信号n,栅极接第三控制信号clks;第十二晶体管m12的源极接地,漏极接第十晶体管m10的漏极和第二输出信号p,栅极接第三控制信号clks;第一与非门nand1的输入接第一输入信号vin和第一控制信号d,输出接第七晶体管m7的栅极;第二与非门nand2的输入接第二输入信号 vip和第一控制信号d,输出接第八晶体管m8的栅极;

29.附图2所示高速动态并行逻辑电路结合附图3所示的6位sar adc控制逻辑及其附图4 所示的时序图可以更好的对所发明的电路的工作模式进行描述:附图三中的6位sar adc 控制逻辑由6个所发明的高速动态并行逻辑电路组成,依次表示为c1~c6,最左侧第一个控制逻辑控制dac阵列中第一位电容,依次往右控制后几位电容。clks_b为采样信号clks的反向信号,且clks_b作为第一个电容控制逻辑的第一控制信号d的输入。当采样信号clks 为高电平时,比较器复位,附图4中所示的outp和outn即为比较器的输出正端和负端均复位到低电平,所以第二控制信号valid为低电平;sar adc进行采样,此时第十一晶体管 m11和第十二晶体管m12导通,将第一输出信号n和第二输出信号p拉到地,6个控制逻辑的输第一输出信号n和第二输出信号p均处于复位状态,电容阵列正端和负端的所有电容的下极板均为地,c1~c6中的第九晶体管m9和第十晶体管m10的栅极为低电平,因此导通。而第一与非门nand1和第二与非门nand2的输出均为高电平,因此第七晶体管m7和第八晶体管m8均不导

通。

30.当采样信号clks为低时,此时比较器使能信号clkc为高电平,比较器开始比较;clks_b 为高电平,因此控制逻辑c1的第一控制信号d为高电平,将第三晶体管m3的漏极拉到地。当通过一定比较器结果之后,比较器得到输出结果,比较器的输出正端和负端outp和outn 一个为高电平一个为低电平,所以c1~c6中的第一与非门nand1和第二与非门nand2的第一输入信号vin和第二输入信号vip一个为高电平一个为低电平,而此时只有c1中的第一控制信号d为高电平,第一与非门nand1和第二与非门nand2的输出受到第一输入信号vin和第二输入信号vip控制,c2~c6中的第一与非门nand1和第二与非门nand2的其中一端输入第一控制信号d仍为低电平,两者输出仍为高电平,因此第七晶体管m7和第八晶体管m8均不导通。c1中的第一与非门nand1和第二与非门nand2的输出因第一输入信号vin和第二输入信号vip的不同而一个为高电平一个为低电平,又因为此时第九晶体管m9和第十晶体管m10导通,所以第一输出信号n和第二输出信号p其中一端会被快速拉高,由其所控制的电容下极板一个快速充电至参考电压vref,一个仍然接地。同时,第二控制信号valid因为比较器的输出有效而变为高电平,第二晶体管m2导通,其漏极被放电至低电平,则第四晶体管m4导通,其漏极被拉到高电平。当第二控制信号valid为高电平后,比较器的比较信号clkc被拉低,比较器进行复位,经过一定延迟后,第二控制信号valid因为比较器两端被复位到低电平而拉低,当第二控制信号valid被拉低之后,第五晶体管m5导通,第三输出信号q被拉高,导致第九晶体管m9和第十晶体管m10截止,此,则下次比较之后的结果不会影响到c1中第一输出信号n和第二输出信号p点电位,即下次比较之前,c1中第一输出信号n和第二输出信号p电位即被锁定。且因为第二控制信号valid被拉低,clkc 则又被拉高,开始下次比较,又因为c2中的第一与非门nand1和第二与非门nand2的第一控制信号d接c1的第三输出信号q,所以c2中第一与非门nand1和第二与非门nand2 的第一控制信号d被拉高,此时第二次比较得到的结果对c2中第七晶体管m7和第八晶体管m8有效。

31.c1~c6的输出sc1~sc6依次被拉高,c1~c6的第一输出信号n和第二输出信号p依次被锁定,时序了位选关断的功能;c1~c6的第一控制信号d依次被拉高,其第一与非门nand1 和第二与非门nand2依次使能,由第一输出信号n和第二输出信号p所控制电容依次翻转。直至c6当被拉高之后,比较器的比较信号clkc被拉低,停止比较,当下一个采样信号来临时,c1~c6中的第一输出信号n和第二输出信号p再次被复位,第三输出信号q复位为低,即sc1~sc6复位为低电平。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。