1.本发明涉及微纳加工、重分布层(rdl)和晶上集成技术领域,尤其是涉及一种适用于晶上集成的晶圆基板标准集成区域布线结构与方法。

背景技术:

2.随着摩尔定律和登纳德缩放定律逐渐失效,工艺进步对计算性能的提升明显放缓,而万物互联的数据量却在指数级爆炸式增长,数据规模和计算能力的“剪刀差”鸿沟越来越大,集成电路正在迎来“后摩尔时代”的技术与产业重大变革期。

3.针对摩尔定律已存在不可延续的难题,晶圆级系统(system on wafer,sow)受到学术界和产业界的重点关注,并藉此来对摩尔定律进行扩展。其主要内涵是将未封装的芯片直接贴合到布有金属走线的晶圆基板上,以此降低芯片间的互连距离,缩小互连线的线宽与间距,提升系统的连接带宽。与传统的芯片封装后再集成到pcb的方案相比,晶圆的集成密度能提升2500倍。

4.然而,不同于传统的pcb集成方案,通过晶圆基板走线的替代方案,在缺乏灵活性的同时,不仅受半导体机台工艺的约束,还面临巨大的良率问题。首先,为了控制芯片良率,半导体的光罩掩膜尺寸远小于晶圆,一般是通过相同的光罩重复在晶圆上刻蚀,才能得一个个芯片。因此受机台工艺的约束,晶圆基板上的走线网络必须有一个个重复的标准集成区域拼接而成。其次,尽管是控制光罩掩膜的尺寸,在金属层数过多的条件下,仍不能保证较高的的良率。研究表明,即使将金属层数控制到4层,在10%的金属利用率下,良率也仅有85.11%。因此如何在晶圆基板的标准集成区域用较少的金属层数满足提供一个丰富的走线网络成为一个关键技术难题。

技术实现要素:

5.为解决现有技术的不足,本发明通过三层走线和标准集成区域的信号线互连,实现提高良率,提高晶圆走线网络互通性的目的,本发明采用如下的技术方案:一种适用于晶上集成的晶圆基板标准集成区域布线结构,在晶圆基板上划分区域作为标准集成区域,标准集成区域向上提供管脚,通过连接管脚构建晶上走线网络,每个标准集成区包括三层金属层,顶层金属层包括核心电压管脚、互连信号管脚和复杂功能管脚,中层金属层包括时钟信号管脚,底层金属层包括地线管脚;连接所述核心电压管脚,构建核心电压网络,用于获取核心电压供电能力;连接分布在两个标准集成区域的所述互连信号管脚,构建互连信号网络,为两个标准集成区域提供互连通道;通过所述复杂功能管脚,将标准集成区域与外接信号单独连通,用于复杂功能;连接所述时钟信号管脚,构建时钟信号网络;连接所述地线管脚,构建地线网络。

6.进一步地,所述标准集成区是在晶圆基板上划分的紧密排布的正方形区域,标准

集成区根据配合设置的管脚,在顶层金属层进行区域的划分,以核心电压区为中心,按中心对称的原则,设置四个端角的对角互连信号区、四边的平行互连信号区,以及位于对角互连信号区与平行互连信号区之间的复杂功能区;所述核心电压区设有核心电压管脚,用于获取核心电压供电能力,面积为标准集成区域的1/4;所述对角互连信号区设有互连信号管脚,为对角的标准集成区域提供可配置的互连通道,每个区域面积为标准集成区域的1/16;所述平行互连信号区设有互连信号管脚,为相邻标准集成区域提供高密度的高速并行互连通道,长度为标准集成区域的1/2;所述复杂功能区与核心电压区连接,设有的复杂功能管脚直接通过硅通孔(tthrough silicon via,tsv),与外接信号单独连通,以满足系统测试、多电源域供电等复杂功能。

7.进一步地,所述核心电压网络和/或地线网络,基于核心电压区域,向四周呈“井字形”延展,使得核心电压网络和/或地线网络能够覆盖到整个标准集成区域, 以减少芯片面积内的直流压降,使芯片可以得到均衡的供电电压。

8.进一步地,所述对角互连信号区的互连信号管脚,呈l字形串接成对角互连信号网络,信号路径跨越多个标准集成区域,通过选取走线网络上的两对管脚,形成距离等长的高速差分信号对,以满足高速信号传输的信号质量需求。

9.进一步地,所述时钟信号网络环绕排布于对应的所述核心电压区,以减少布线层数,提高制造良率。

10.进一步地,所述标准集成区域的尺寸小于相应集成电路工艺光罩的最大尺寸,以满足标准化的半导体制造工艺。

11.进一步地,所述复杂功能管脚,除复杂管脚功能区外,在版图主体设计完毕后,错落分布于整个标准集成区,在整体走线网络的基础上,为测试、配置需求形成有效补充,可以充分利用设计空间。

12.进一步地,以条纹交错方式排布所述核心电压管脚和/或地线管脚构成的网络,形成最短的回流路径。

13.一种适用于晶上集成的晶圆基板标准集成区域布线方法,包括如下步骤:步骤s1:在晶圆基板上划分出规则排布的标准集成区域;步骤s2:确定标准集成区域向上提供的管脚分布,包括核心电压管脚、互连信号管脚、复杂功能管脚、时钟信号管脚和地线管脚;步骤s3:通过连接管脚构建晶上走线网络,并绘制三层金属层的光刻掩模版:步骤3.1:在顶层金属层,通过核心电压管脚,根据网格化原则绘制核心电压网络走线,用于获取核心电压供电能力;通过互连信号管脚,根据不交错原则绘制互连信号网络走线;通过复杂功能管脚,将标准集成区域与外接信号单独连通,用于复杂功能;步骤3.2:在中层金属层,通过时钟信号管脚,绘制时钟信号网络;步骤3.3:在底层金属层,通过地线管脚,根据网格化原则绘制地线网络;步骤s4:确定各走线网络连接晶圆基板硅通孔tsv的扇出坐标;步骤s5:通过不同标准集成区域的互连信号管脚,绘制互联信号网络,为两个标准

集成区域提供互连通道。

14.进一步地,所述步骤s4中,确定原则包括:选取中层金属层、底层金属层未经过的核心电压管脚坐标,作为核心电压网络对接硅通孔tsv扇出的连接点;选取底层金属层未经过的时钟信号管脚坐标,作为时钟信号网络对接硅通孔tsv扇出的连接点;选取地线管脚坐标,作为地线网络对接硅通孔tsv扇出的连接点;复杂功能管脚直接连通硅通孔tsv进行扇出;互连信号管脚无需通过tsv扇出。

15.本发明的优势和有益效果在于:本发明仅通过三层走线,便可提供覆盖核心电压供电、地线走线、多电源域供电、调试、时钟网络等功能的管脚分布,由于层数的减少,大大提升晶圆基板的生产良率,并提升晶上集成的兼容度;同时本发明提出的互连走线网络跨越多个标准集成区域,通过标准集成区域的互连信号线,将整个晶圆系统构筑成一个发达互通网络,可以灵活支持更大规模的晶上芯粒间互连。

附图说明

16.图1为本发明实施例中晶上集成系统晶圆基板上的标准集成区域分布示意图。

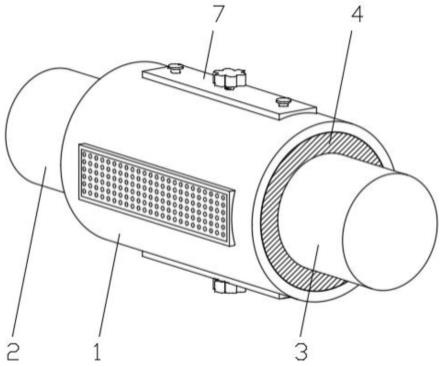

17.图2为本发明实施例中晶上集成系统立体结构截面示意图。

18.图3为本发明实施例中标准集成区域顶层金属层走线网络示意图。

19.图4为本发明实施例中标准集成区域中层金属层走线网络示意图。

20.图5为本发明实施例中标准集成区域底层金属层走线网络示意图。

21.图6为本发明实施例中标准集成区域信号管脚的分区示意图。

22.图7为本发明实施例中标准集成区域布线方法流程图。

23.图8为本发明实施例中标准集成区域三层技术走线的立体层次图。

24.图9a为本发明实施例中对角标准集成区域通过对角互连信号网络连接的通路示意图。

25.图9b为本发明实施例中相邻标准集成区域通过对角互连信号网络连接的通路示意图。

26.其中:1、晶圆基板,2、标准集成区域,3、标准集成件,4、硅通孔,5、复杂功能管脚,6、互连信号管脚,7、核心电压管脚,8、核心电压网络,9、互连信号网络,10、时钟信号管脚,11、时钟信号网络,12、地线管脚,13、地线网络,14、对角互连信号区,15、核心电压区,16、平行互连信号区,17、复杂功能区。

具体实施方式

27.以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

28.适用于晶上集成的晶圆基板标准集成区域布线结构,如图1、图2所示,在晶圆基板1上划分区域作为标准集成区域2,标准集成区域2向上提供管脚,通过连接管脚构建晶上走线网络,每个标准集成区包括三层金属层,如图3至图5所示,顶层金属层包括核心电压管脚7、互连信号管脚6和复杂功能管脚5,中层金属层包括时钟信号管脚10,底层金属层包括地线管脚12;

连接核心电压管脚7,构建核心电压网络8,用于获取核心电压供电能力;连接分布在两个标准集成区域2的所述互连信号管脚6,构建互连信号网络9,为两个标准集成区域2提供互连通道;通过复杂功能管脚5,将标准集成区域2与外接信号单独连通,用于复杂功能;连接时钟信号管脚10,构建时钟信号网络11;连接地线管脚12,构建地线网络13。

29.标准集成区是在晶圆基板1上划分的紧密排布的正方形区域,如图6所示,标准集成区根据配合设置的管脚,在顶层金属层进行区域的划分,以核心电压区15为中心,按中心对称的原则,设置四个端角的对角互连信号区14、四边的平行互连信号区16,以及位于对角互连信号区14与平行互连信号区16之间的复杂功能区17;核心电压区15设有核心电压管脚7,用于获取核心电压供电能力,面积为标准集成区域2的1/4;对角互连信号区14设有互连信号管脚6,为对角的标准集成区域2提供可配置的互连通道,每个区域面积为标准集成区域2的1/16;平行互连信号区16设有互连信号管脚6,为相邻标准集成区域2提供高密度的高速并行互连通道,长度为标准集成区域2的1/2;复杂功能区17与核心电压区15连接,设有的复杂功能管脚5直接通过硅通孔4(tthrough silicon via,tsv),与外接信号单独连通,以满足系统测试、多电源域供电等复杂功能。

30.核心电压网络8和/或地线网络13,基于核心电压区15,向四周呈“井字形”延展,使得核心电压网络8和/或地线网络13能够覆盖到整个标准集成区域2。

31.对角互连信号区14的互连信号管脚6,呈l字形串接成对角互连信号网络,信号路径跨越多个标准集成区域2,通过选取走线网络上的两对管脚,形成距离等长的高速差分信号对。

32.时钟信号网络11环绕排布于对应的所述核心电压区15。

33.标准集成区域2的尺寸小于相应集成电路工艺光罩的最大尺寸。

34.复杂功能管脚5,除复杂管脚功能区外,在版图主体设计完毕后,错落分布于整个标准集成区,在整体走线网络的基础上,为测试、配置需求形成有效补充。

35.以条纹交错方式排布所述核心电压管脚7和/或地线管脚12构成的网络。

36.适用于晶上集成的晶圆基板标准集成区域布线方法,如图7所示,包括如下步骤:步骤s1:在晶圆基板1上划分出规则排布的标准集成区域2;本发明的实施例中,在晶圆基板1上按照20mm*20mm的正方形区域大小划分出规则排布的标准集成区域2,如图1所示;晶圆基板1上每个标准集成区域2都将采用相同的光刻掩膜进行刻蚀。根据目标工艺,确定向上生长的管脚直径尺寸与管脚间距。本实施例选取管脚直径尺寸为10um,管脚间距为10um作为说明。在此条件下标准集成区域2每行最大可以支持1000个管脚。

37.步骤s2:确定标准集成区域2向上提供的管脚分布,包括核心电压管脚7、互连信号管脚6、复杂功能管脚5、时钟信号管脚10和地线管脚12;2.1、在标准集成区域2的正中心位置10mm*10mm的区域按照条纹交错的方式排布

500*500个核心电压管脚7与地线管脚12,如图3所示;此处为方便展示,图上一个管脚点代表50个实际管脚;2.2、在标准集成区域2的正中心位置10mm*10mm的区域对齐核心电压管脚7向外延伸出“井字形”网络,使得核心电压网络8的供电管脚可以覆盖到整个标准集成区域2;2.3、在标准集成区域2的正中心位置10mm*10mm的区域对齐地线管脚12向外延伸出“井字形”网络,使得地线网络13也可以覆盖到整个标准集成区域2;2.4、在每个平行互连信号区16均匀分布一排250个管脚,管脚按照“核心电压管脚-互连信号管脚-互连信号管脚-接地管脚

‑‑

互连信号管脚-互连信号管脚-核心电压管脚”方式交错排布,共2个核心电压管脚7、82个接地信号管脚、166个互连信号管脚6;互连信号管脚6用于连接相邻的两个标准集成区域2。

38.2.5、在对角互连信号区145mm*5mm大小的面积均匀分布250*250个信号管脚,其中45

°

对角线上的一排管脚设为配置管脚,其余的设为对角互连信号管脚,用于支撑l型互连信号网络9,如图3、图6对应的右上角与左下角所示。

39.2.6、环绕10mm*10mm的核心供电区,在复杂功能区17设置复杂功能管脚5与时钟信号管脚10,复杂功能管脚5与时钟信号管脚10数量的比率为2:1;如图6所示步骤s3:通过连接管脚构建晶上走线网络,并绘制三层金属层的光刻掩模版:步骤3.1:在顶层金属层,通过核心电压管脚7,根据网格化原则绘制核心电压网络走线,用于获取核心电压供电能力;通过互连信号管脚6,根据不交错原则绘制互连信号网络走线;通过复杂功能管脚5,将标准集成区域2与外接信号单独连通,用于复杂功能;如图3所示;步骤3.2:在中层金属层,通过时钟信号管脚10,绘制时钟信号网络11,如图4所示;步骤3.3:在底层金属层,通过地线管脚12,根据网格化原则绘制地线网络13,如图5所示;步骤s4:确定各走线网络连接晶圆基板1的硅通孔4tsv的扇出坐标;选择原则遵循:选取中层金属层、底层金属层未经过的核心电压管脚坐标,作为核心电压网络8对接硅通孔4tsv扇出的连接点;选取底层金属层未经过的时钟信号管脚坐标,作为时钟信号网络11对接硅通孔4tsv扇出的连接点;选取地线管脚坐标,作为地线网络13对接硅通孔4tsv扇出的连接点;复杂功能管脚5直接连通硅通孔4tsv进行扇出;互连信号管脚6无需通过tsv扇出;如图8所示。

40.步骤s5:通过不同标准集成区域2的互连信号管脚6,绘制互联信号网络,为两个标准集成区域2提供互连通道。

41.晶圆基板1的目的是为标准集成件3的集成提供丰富可靠的走线网络。在晶圆基板1制备完毕后,标准集成件3与标准集成区域的热压贴合拼装并不需要将全部管脚键合。如图9a、图9b所示的a、b、c、d四个标准集成区域交界处,用户可选取b、c标准集成区域上的对角互连信号管脚通过l型网络构成多对差分信号对,以完成对角标准集成区域上标准集成件3的信号连接,如图9a所示;亦可选取a、c标准集成区域上的管脚与b标准集成区域上的管脚形成连接网络,以此来加强标准集成区域b的带宽汇聚能力,如图9b所示。

42.综上所述,本发明实施例首次提供了一种适用于晶上集成的晶圆基板标准集成区域布线结构与方法,仅利用三层金属走线层就为标准集成件3提供涵盖供电、接地、时钟、调

试、多电源域等丰富晶上互连走线资源,大大地提升了晶圆基板1的制备良率;同时针对晶上集成的不同功能区域带宽汇聚能力的差异化需求,本发明实施例给出的对角互连信号网络还支持灵活配置的跨区域连接。

43.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。