1.本技术涉及电子电路技术领域,尤其涉及一种上电防过冲电路、芯片及电子设备。

背景技术:

2.随着芯片集成度增加,工艺节点更新,集成电路设计所使用的常规器件的最小沟道长度也越来越小,工作电压也越来越低,因而其电压耐受能力也随之降低。为了保证工作及电路关断时,电路中所有的cmos器件的栅源电压|v

gs

|、栅漏电压|v

gd

|、源漏电压|v

sd

|均在工艺要求的电压范围内,比如1.5v数字器件,一般工艺要求上述电压均在1.5v

±

10%范围内,否则会引起可靠性降低、寿命降低、漏电或者工作不正常的情况。

3.电压输出电路为芯片提供电源,在电压输出电路上电过程中,由于工作状态不定,输出电压可能会输出一个过冲,导致后续电路产生冲击损坏,直接影响相关电子产品的寿命和可靠性。

技术实现要素:

4.本技术提供一种上电防过冲电路、芯片及电子设备,其主要目的在于防止电源在上电过程中产生过冲,有效提高电源输出的稳定性,减小后续电路被损坏的概率。

5.第一方面,本技术实施例提供一种上电防过冲电路,包括:

6.电流镜电路,所述电流镜电路用于在电源上电过程中产生第一电流信号;

7.势差电路,连接于所述电流镜电路,所述势差电路用于在电源上电过程中产生第二电流信号,并在所述势差电路与所述电流镜电路的连接节点输出势差信号;

8.电荷泄放电路,连接于所述连接节点以及目标电路,并用于根据所述势差信号泄放所述目标电路的电荷。

9.第二方面,本技术实施例提供一种带隙基准电路,包括第一方面提供的上述任一种上电防过冲电路和带隙基准单元,所述目标电路为所述带隙基准单元,所述防过冲电路与所述带隙基准电路的输出端连接。

10.第三方面,本技术实施例提供一种线性稳压源电路,包括第一方面提供的上述任一种上电防过冲电路和线性稳压源单元,所述目标电路为所述线性稳压源单元,所述防过冲电路与所述线性稳压源单元的输出端连接。

11.第四方面,本技术实施例提供一种防过冲的电压产生电路,包括第一方面提供的上述任一种上电防过冲电路和电压产生电路,所述目标电路为所述电压产生电路,所述电压产生电路包括带隙基准电路和防过冲的线性稳压源电路。

12.第五方面,本技术实施例提供一种芯片,包括第一方面提供的上述任一种上电防过冲电路。

13.第六方面,本技术实施例提供一种电子设备,包括第五方面提供的芯片。

14.本技术实施例提供一种上电防过冲电路、芯片及电子设备,该防过冲电路包括电流镜电路、势差电路和电荷泄放电路三部分,当利用该防过冲电路对目标电路进行防电压

过冲时,在目标电路上电的过程中,电流镜电路首先产生第一电流信号,势差电路在电流镜电路产生第一电流信号之后,在目标电路继续上电的过程中产生第二电流信号,并且势差电路在与电流镜电路的连接节点出输出势差信号,电荷泄放电路的第一端接收到该势差信号后,将目标电路的电压输出端口处累积的电荷进行泄放,可以有效避免目标电路在上电过程中的过压问题。

附图说明

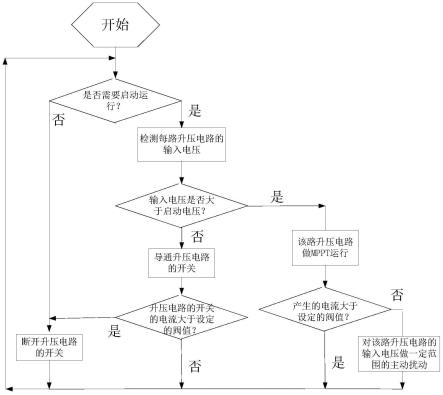

15.图1为本技术实施例中提供的一种上电防过冲电路的应用示意图;

16.图2为本技术实施例中提供的一种上电防过冲电路的结构示意图;

17.图3为本技术一实施例提供的一种上电防过冲电路的结构示意图;

18.图4为本技术实施例中电流镜电路的结构示意图;

19.图5为本技术实施例中第一电流支路和第二电流支路的结构示意图;

20.图6为本技术一实施例中一种上电防过冲电路的结构示意图;

21.图7为本技术又一实施例中一种上电防过冲电路的结构示意图;

22.图8为本技术提供的一种带隙基准电路的结构示意图;

23.图9为本技术提供的一种线性稳压源电路的结构示意图;

24.图10为本技术实施例提供的一种防过冲的电压产生电路的结构示意图;

25.图11为本技术实施例提供的一种电子设备的结构示意图。

26.附图说明:

27.100,上电防过冲电路;200,电压输出电路;

28.210,电流镜电路;220,势差电路;

29.230,电荷泄放电路;310,第一电流支路;

30.320,第二电流支路;m1,第一晶体管;

31.m2,第二晶体管;c,电容;

32.m3,第三晶体管;m4,第四晶体管;

[0033]vout

,电压输出端口;vb,偏置电压;

[0034]

m5,第五晶体管;m6,第六晶体管;

[0035]

m7,第七晶体管;enp,第一使能信号;

[0036]

enn,第二使能信号;avd,电源电压;

[0037]

300,带隙基准电路;400,防过冲的带隙基准电路;

[0038]

500,线性稳压源单元;600,防过冲的线性稳压源电路;

[0039]

700,电子设备。

[0040]

本技术目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

[0041]

下面详细描述本技术的实施方式,实施方式的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施方式是示例性地,仅用于解释本技术,而不能理解为对本技术的限制。

[0042]

为了使本技术领域的人员更好地理解本技术的方案,下面将结合本技术实施例中

的附图,对本技术实施例中的技术方案进行清楚、完整的描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

[0043]

本技术实施例中,至少一个是指一个或多个;多个,是指两个或两个以上。在本技术的描述中,“第一”、“第二”、“第三”等词汇,仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。

[0044]

在本说明书中描述的参考“一种实施方式”或“一些实施方式”等意味着在本技术的一个或多个实施方式中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。

[0045]

需要指出的是,本技术实施例中“连接”可以理解为电连接,两个电学元件连接可以是两个电学元件之间的直接或间接连接。例如,a与b连接,既可以是a与b直接连接,也可以是a与b之间通过一个或多个其它电学元件间接连接。

[0046]

本技术实施例提供的一种上电防过冲电路100可应用在如图1所示的电压输出电路200中,本技术实施例中上电防过冲电路以下简称防过冲电路100,该电压输出电路200的电源电压avd与防过冲电路100的电流镜电路210连接,该电压输出电路200的电压输出端口v

out

与电荷泄放电路230连接,在电压输出电路200工作时,电源电压avd在上电过程中,该防过冲电路100中的电流镜产生第一电流信号,紧接着势差电路220生成第二电流信号,势差电路220在与电流镜电路210的连接节点出输出势差信号;电荷泄放电路230与该势差电路220的连接节点进行相连,电压输出电路200与该电荷泄放电路230连接,电荷泄放电路230根据该势差信号泄放电压输出电路200累积的电荷。本技术实施例可以通过该防过冲电路100释放电压输出电路200在上电过程中电压输出端口v

out

处累积的电荷,从而可以防止电压过冲,保障后续电路中电子器件的安全,提高电压输出电路200的稳定性和使用寿命。

[0047]

本技术实施例提供一种上电防过冲电路100,该防过冲电路100的结构如图2所示,该防过冲电路100包括电流镜电路210、势差电路220和电荷泄放电路230,电流镜电路210,所述电流镜电路210用于在电源上电过程中产生第一电流信号;势差电路220,连接于所述电流镜电路210,所述势差电路220用于在电源上电过程中产生第二电流信号,并在所述势差电路220与所述电流镜电路210的连接节点输出势差信号;电荷泄放电路230,连接于所述连接节点以及目标电路,并用于根据所述势差信号泄放所述目标电路的电荷。

[0048]

本技术实施例中提供的防过冲电路100包括电流镜电路210、势差电路220和电荷泄放电路230,防过冲电路100是为了防止目标电路的在上电过程中产生电压过冲,目标电路可以是带隙基准电路、线性稳压源电路、电压生成电路等等,具体可以根据实际需要进行确定,本技术实施例对此不做具体限定。目标电路在电源上电过程中,电压输出端口v

out

处容易累积过量电荷,从而容易对连接的相关电子器件产生过冲,从而导致电子器件的损坏,本技术实施例中的目标电路是挂载在电源电压avd上的,通过该电源电压avd为目标电路提供初始电源。

[0049]

具体地,本技术实施例中的电流镜电路210的第一端与电源电压avd连接,电流镜电路210的第二端与势差电路220的一端连接,电流镜电路210和势差电路220的连接节点与电荷泄放电路230的第一端连接,目标电路的电压输出端口v

out

与电荷泄放电路230的第二

端连接。本技术实施例中电流镜电路210的功能是在目标电路上电的过程中产生第一电流信号,具体地,在目标电路上电过程中,电源的瞬时电压是在逐渐变大的,当电源的瞬时电压大于一定阈值时,该电流镜电路210被触发导通,开始产生第一电流信号;本技术实施例中的电流镜电路210可以是由两个晶体管连接组成的模拟电路来实现,也可以是由具有相同功能的数字芯片实现,还可以通过编程语言配置出相应功能的可编程逻辑器件来实现,具体可以根据实际情况进行确定,本技术实施例对此不做具体限定。在电流镜电路210产生第一电流信号之后,势差电路220被触发,并且在电源电压avd继续上电的过程中,电源的瞬时值也继续增大,当电源的瞬时值继续增大到又一阈值时,触发势差电路220,势差电路220产生第二电流信号;势差电路220可以是由二极管、晶体管等组成的模拟电路实现,也可以是由触发器、控制器等数字芯片组成的数字电路来实现,具体可以根据实际情况进行确定,本技术实施例对此不做具体限定。

[0050]

本技术实施例中势差电路220在与电流镜电路210的连接节点出输出势差信号,而电荷泄放电路230的第一端正好与该连接节点相连,电荷泄放电路230的第一端接收到该势差信号后,将目标电路的电压输出端口处累积的电荷进行泄放,可以有效避免目标电路在上电过程中的过压问题。本技术实施例中的电荷泄放电路230可以是由开关管组成的模拟电路来实现,也可以是由具有相同功能的数字芯片实现,还可以通过编程语言配置出相应功能的可编程逻辑器件来实现,具体可以根据实际情况进行确定,本技术实施例对此不做具体限定。

[0051]

本技术实施例提供一种上电防过冲电路100,该防过冲电路100包括电流镜电路210、势差电路220和电荷泄放电路230三部分,当利用该防过冲电路100对目标电路进行防电压过冲时,在目标电路上电的过程中,电流镜电路210首先产生第一电流信号,势差电路220在电流镜电路210产生第一电流信号之后,在目标电路继续上电的过程中产生第二电流信号,并且势差电路220在与电流镜电路210的连接节点出输出势差信号,电荷泄放电路230的第一端接收到该势差信号后,将目标电路的电压输出端口处累积的电荷进行泄放,可以有效避免目标电路在上电过程中的过压问题。

[0052]

在上述实施例的基础上,优选地,所述第一电流信号大于所述第二电流信号,所述势差信号根据所述第一电流信号和所述第二电流信号之差产生;

[0053]

所述电荷泄放电路230被配置为:根据所述势差信号使得所述电荷泄放电路230的工作电压大于阈值电压,所述电荷泄放电路230导通,以使得所述目标电路的电压输出端口通过所述电荷泄放电路230释放电荷。

[0054]

具体地,本技术实施例中第一电流信号大于第二电流信号,势差电路220利用第一电流信号和第二电流信号之间的电流差,根据该电流差产生势差信号,电荷泄放电路230根据该势差信号,控制电荷泄放电路230的工作电压大于阈值电压,从而使得该电荷泄放电路230导通,从而使得目标电路的电压输出端口通过该电荷泄放电路230释放电荷,防止电压过冲。

[0055]

在具体实施过程中,如图3所示,电流镜电路210的第一端与电源电压avd连接,电流镜电路210的第二端与势差电路220的一端连接,势差电路220的另一端接地,电流镜电路210和势差电路220之间的连接节点与电荷泄放电路230的控制端连接,目标电路的电压输出端口v

out

与电荷泄放电路230的第一端连接,电荷泄放电路230的第二端接地。

[0056]

该电荷泄放电路230中包括充电单元和开关单元,该充电单元可以是电容或其它可以实现充电功能的电子器件,开关单元可以是晶体管或其它可以实现开关功能的电子器件;势差电路220利用第一电流信号和第二电流信号之间的差值对电荷泄放电路230中的充电单元进行充电,当充电达到一定的电势后,开关单元的工作电压大于开关单元的阈值电压,从而开关单元导通,即电荷泄放电路230导通,目标电路的电压输出端口v

out

通过电荷泄放电路230释放累积的电荷,避免了目标电路在上电过程中发生电压过冲,从而可以保障目标电路后续连接的电子器件不会因电压过冲而损坏,提高了目标电源电路的稳定性和使用寿命。

[0057]

本技术实施例中由于第一电流信号大于第二电流信号,利用电流镜电路210产生的第一电流信号和势差电路220产生的第二电流信号之间的差值,对电荷泄放电路230进行充电,当电荷泄放电路230的第一端电压达到一定电势值时,电荷泄放电路230的第二端和第三端导通,而目标电路的电压输出端口v

out

与电荷泄放电路230的第二端连接,电荷泄放电路230导通后,在电压输出端口v

out

处累积的电荷可以通过电荷泄放电路230释放到地中,本技术实施例中的电荷泄放电路230通过一定的直流电压通过初级回路对电荷泄放电路230电容充电,当电容电压大于放电管击穿电压时,开关放电管迅速击穿,使得电荷泄放电路230导通,因此该电荷泄放电路230可以是开关三极管、晶体管等半导体器件,利用半导体器件做电荷泄放电路230,既能实现开关功能,又能最大限度减少防过冲电路100中使用的电子器件数量,从而降低防过冲电路100的占用面积,并降低成本。

[0058]

本技术实施例提供一种上电防过冲电路100,该防过冲电路100包括电流镜电路210、势差电路220和电荷泄放电路230三部分,当利用该防过冲电路100对目标电路进行防电压过冲时,在目标电路上电的过程中,电流镜电路210首先产生第一电流信号,势差电路220在电流镜电路210产生第一电流信号之后,在目标电路继续上电的过程中产生第二电流信号,并且第一电流信号大于第二电流信号,然后利用第一电流信号和第二电流信号之间的差值对电荷泄放电路230进行充电,当充电达到一定的电势后,电荷泄放电路230导通,目标电路的电压输出端口v

out

通过电荷泄放电路230释放累积的电荷,避免了目标电路在上电过程中发生电压过冲,从而可以保障目标电路后续连接的电子器件不会因电压过冲而损坏,提高了目标电源电路的稳定性和使用寿命。

[0059]

在上述实施例的基础上,优选地,所述电流镜电路210还被配置为:在所述电源上电稳定后,所述电流镜电路210停止生成所述第一电流信号,以使得所述电荷泄放电路230截止。

[0060]

本技术实施例中当目标电路上电稳定之后,为了不影响目标电路的正常工作,且在目标电路上电稳定之后也没有防过冲需求,因此需要断开该防过冲电路100,为了达到这一目的,该电流镜电路210在电源上电稳定之后,电流镜电路210断开,停止生成第一电流信号,电荷泄放电路230第一端的电压通过势差电路220进行放电,当电荷泄放电路230放电后,第一端的电压无法使得电荷泄放电路230导通,电荷泄放电路230也截止,因此电压输出端口v

out

无法通过电荷泄放电路230继续释放电荷。本技术实施例中在目标电路上电完成后,通过势差电路220释放电荷泄放电路230第一端的电荷,使得电荷泄放电路230截止,电压输出端口v

out

无法再通过电荷泄放电路230继续释放电荷,防过冲电路100处于不工作的状态,从而后续电路能正常工作。

[0061]

在上述实施例的基础上,优选地,所述电流镜电路210包括:第一电流支路310,所述第一电流支路310用于在所述电源上电过程中产生初始电流信号;以及第二电流支路320,与所述第一电流支路310连接,用于镜像所述初始电流信号,并产出所述第一电流信号。

[0062]

具体地,电流镜电路210包括第一电流支路310和第二电流支路320,其中:第一电流支路310用于在所述电源上电过程中,产生初始电流信号,并将初始电流信号输送至第二电流支路320;第二电流支路320用于将初始电流信号放大预设倍数后,输出第一电流信号。

[0063]

本技术实施例中的电流镜电路210具体电流镜功能,电流镜是模拟集成电路中普遍存在的一种标准部件,它的受控电流与输入参考电流相等或者放大若干倍,即输入电路和输出电流的传输比等于n,输出电流是对输入电流按一定比例的“复制”,用来产生偏置电流或作为有源负载。具体地,本技术实施例中的电流镜电路210包括第一电流支路310和第二电流支路320,第一电流支路310用于在电源上电过程中,第一电流支路310产生初始电流信号,并且将该初始电流信号输送至第二电流支路320,然后第二电流支路320对初始电流信号放大预设倍数,输出第一电流信号,此处预设倍数即为上述的n,该预设倍数的取值可以根据实际情况进行确定,本技术实施例对此不做具体限定。本技术实施例中通过第一电流支路310和第二电流支路320来实现电流镜电路210,具有结构简单、使用电子器件少的优点。

[0064]

在上述实施例的基础上,优选地,所述第一电流支路310包括第一晶体管和电容,所述第一晶体管的第一端与所述电源连接,第二端与所述电容的一端连接,所述第一晶体管的控制端与所述第二电流支路320连接,所述电容的另一端接地,所述第一晶体管的第二端还与所述第一晶体管的控制端连接。

[0065]

具体地,第一电流支路310包括第一晶体管m1,第一晶体管m1的第一端与电源连接,第一晶体管m1的第二端与电容的一端连接,第一晶体管的控制端与第二电流支路320连接,电容的另一端接地,第一晶体管的第二端与第一晶体管的控制端连接。

[0066]

在上述实施例的基础上,优选地,所述第二电流支路320包括第二晶体管,所述第二晶体管的第一端与所述电源连接,所述第二晶体管的第二端与所述势差电路220连接,所述第二晶体管的控制端与所述第一晶体管的控制端连接。

[0067]

作为一种实施方式,参见图4,该电流镜电路210的第一电流支路310包括第一晶体管m1,上述所说的第一电流支路310对应的阈值电压即为第一晶体管m1的阈值电压,本技术实施例中的第一晶体管m1为pmos晶体管,也可以为p型三极管,具体可以根据实际情况进行确定,本技术实施例以pmos晶体管为例进行说明。本技术实施例中,该第一晶体管m1的源极(第一端)和电源电压avd连接,该第一晶体管m1的栅极(控制端)和第二电流支路320连接,该第一晶体管m1的漏极(第二端)和第一晶体管m1的栅极(控制端)连接。该第二电流支路320包括第二晶体管m2,第二晶体管m2一般为与第一晶体管m1同类型的晶体管,当第一晶体管m1为p型三极管时,该第二晶体管m2也是p型三极管,第二晶体管m2的源极(第一端)和电源电压avd连接,第二晶体管m2的栅极(控制端)和第一晶体管m1的栅极(控制端)连接,该第二晶体管m2的漏极(第二端)和势差电路220连接。当该目标电路在上电过程中,电源的瞬时电压值慢慢上升到大于m1的阈值电压时,m1导通,产生初始电流信号,电源继续上电,瞬时电压值继续变大,当变大到大于m2的阈值电压时,m2导通,m2作为m1的镜像管,对第一电流

信号放大预设倍数后,得到第二电流信号。本技术实施例中利用pmos晶体管来实现电流镜电路210,具有能准确复制电流、不受工艺和温度影响的优点。

[0068]

具体地,该第一电流支路310还包括电容c,第一晶体管m1的第三端通过电容c接地。

[0069]

作为一种可选的实施方式,参见图5,该电流镜电路210中第一电流支路310包括电容c,第一晶体管m1的第三端通过电容c接地。该电容c的作用是为了在电源电压avd上电稳定之后使得电流镜电路210断开,不再生成第一电流信号,其工作原理如下:在目标电路上电的过程中,由于第一晶体管m1采用的是二极管接法,因此在上电过程中,电源电压avd在大于第一晶体管m1的阈值电压之后,第一晶体管m1的漏极(和栅极短接)电压还是0,从而使第一晶体管m1管导通,从而电源电压avd通过第一晶体管m1的源极和漏极的导通给电容c充电,当电容c上级板的电压达到足够高时,甚至等于电源电压avd的额定电压,使得第一晶体管m1的栅源电压小于第一晶体管m1的阈值电压,这时第一晶体管m1截止,而第二晶体管m2为第一晶体管m1的镜像管,因此第二晶体管m2的栅源电压也小于第二晶体管m2的阈值电压,第二晶体管m2关断,从而不再提供第一电流信号,从而电荷泄放电路230关断,不再泄放电荷,防过冲电路100停止工作,目标电路可以继续为后续连接的电子器件正常供电。本技术实施例中充分利用电容c充电和放电的特点,并结合晶体管的导通特性,使得仅仅通过一个电容c就可以实现目标电路上电稳定之后的正常工作,具有结构简单、使用方便的优点。

[0070]

还需要说明的是,当电源电压avd最终上电到稳定电压,电容c的上极板将最终通过二极管接法的第一晶体管m1充电到avd,此时|vgs1|=0,第一晶体管m1截至。而第二晶体管m2为第一晶体管m1的镜像管,有|vgs2|=0,第二晶体管m2关断,不在提供电流。第四晶体管m4的栅极将最终通过第三晶体管m3的导通电流放电到avs地,使第四晶体管m4关断,不再泄放电荷。

[0071]

在上述实施例的基础上,优选地,所述第二晶体管m2尺寸为所述第一晶体管m1尺寸的所述预设倍数。

[0072]

具体地,第二晶体管m2的尺寸为第一晶体管m1尺寸的预设倍数,此处,晶体管的尺寸是指宽度与长度之比,宽度是指晶体管的通道宽度,长度是指晶体管的通道长度,通过控制第二晶体管m2的尺寸与第一晶体管m1的尺寸之比,可以精准的控制第二晶体管m2输出的第一电流信号大于势差电路220输出的第二电流信号,从而可以保证利用电流镜电路210的第一电流信号和势差电路220的第二电流信号之间的差值,对电荷泄放电路230进行充电。

[0073]

在上述实施例的基础上,优选地,所述势差电路220包括第三晶体管m3,所述第三晶体管m3的第一端与所述电流镜电路210连接,所述第三晶体管m3的控制端接收一偏置电压vb,所述第三晶体管m3的第二端接地,所述偏置电压vb初始值可以为0,并随着所述电源电压avd的增大而增大。

[0074]

作为一种实施方式,参见图6,该势差电路220包括第三晶体管m3,第三晶体管m3为nmos晶体管,第三晶体管m3的漏极(第一端)和电流镜电路210连接,即第三晶体管m3的漏极和第二晶体管m2的漏极连接,第三晶体管m3的栅极(控制端)和偏置电压vb连接,第三晶体管m3的源极(第二端)接地,该偏置电压vb在电源电压avd上电之前取值为0,并随着电源电压avd上电过程中随着电源电压avd瞬时值的增大而增大。在该第三晶体管m3工作的过程中,随着电源电压avd的继续增大,偏置电压vb的值也不断增大,当偏置电压vb的取值大于

第三晶体管m3的阈值电压时,第三晶体管m3导通,产生第二电流信号。本技术实施例中利用晶体管来实现势差电路220的功能,具有结构简单、使用方便的优点。

[0075]

在上述实施例的基础上,优选地,所述电荷泄放电路230为第四晶体管m4,所述第四晶体管m4的第一端与所述电压输出端口v

out

连接,所述第四晶体管m4的控制端与所述势差电路220连接,所述第四晶体管m4的第二端接地。

[0076]

作为一种实施方式,参见图6,本技术实施例中的电荷泄放电路230为第四晶体管m4,该第四晶体管m4为nmos晶体管,第四晶体管m4的漏极(第一端)和电压输出端口v

out

连接,第四晶体管m4的栅极(控制端)和势差电路220连接,即第四晶体管m4的栅极(控制端)和第三晶体管m3的漏极连接,第四晶体管m4的源极(第二端)接地。在目标电路上电过程中,利用第二晶体管m2产生的第一电流信号和第三晶体管m3产生的第二电流信号之间的差值,对第四晶体管m4的栅极寄生电容进行充电,直到第四晶体管m4的栅源电压大于第四晶体管m4的阈值电压,使得第四晶体管m4导通,从而目标电路的电压输出端口v

out

处累积的电荷通过第四晶体管m4排出到地中。

[0077]

对于图6所示的上电防过冲电路100,在目标电路的电源电压avd上电之前,电容上极板的初始电压为0,当电源电压avd的瞬时电压达到第一晶体管m1的阈值电压时,第一晶体管m1导通,并通过第一晶体管m1给电容上极板充电,此时第一晶体管m1的栅源电压绝对值大于第一晶体管m1的阈值电压,由于第二晶体管m2为第一晶体管m1的镜像管,因此第二晶体管m2的栅源电压绝对值也大于第二晶体管m2的阈值电压,第二晶体管m2导通,输出第一电流信号。随着电源电压avd继续上电,电源电压avd的瞬时值继续变大,当偏置电压vb大于第三晶体管m3的阈值电压时,第三晶体管m3导通,产生第二电流信号,通过合理设置第一晶体管m1和第二晶体管m2的尺寸大小,可以保证第二晶体管m2的导通电流大于第三晶体管m3的导通电流,因此第一电流信号大于第二电流信号,利用第一电流信号和第二电流信号之间的差值对第四晶体管m4的栅极寄生电容进行充电,直到第四晶体管m4的栅源电压大于第四晶体管m4的阈值电压,第四晶体管m4开始导通。由于第四晶体管m4的漏极直接连接产生电压过冲的电压输出端口v

out

,上电过程中由于v

out

处过量电荷积累产生过冲的电荷将通过第四晶体管m4释放到地gnd,从而防止上电过程中过冲电压的产生。

[0078]

当电源电压avd最终上电到稳定电压,电容的上极板将最终通过二极管接法的第一晶体管m1充电到额定电压,此时第一晶体管m1的栅源电压为0,第一晶体管m1截至。而第二晶体管m2为第一晶体管m1的镜像管,有第二晶体管m2的栅源电压为0,第二晶体管m2关断,不再提供第一电流信号。第四晶体管m4的栅极电压通过第三晶体管m3的导通释放到地,使第四晶体管m4关断,不再泄放电荷。自此整个目标电路上电过程完成,防过冲电路100关闭,其他电路正常工作中不产生功耗。

[0079]

在上述实施例的基础上,优选地,该防过冲电路100还包括:第五晶体管m5、第六晶体管m6和第七晶体管m7,其中:所述第五晶体管m5的第一端与所述电源连接,所述第五晶体管m5的控制端接收第一使能信号enp,所述第五晶体管m5的第二端与所述第一晶体管m1的第二端连接;所述第六晶体管m6的第一端与所述第一晶体管m1的第二端连接,所述第六晶体管m6的控制端接收第二使能信号enn,所述第六晶体管m6的第二端与所述电容远离地线的一端连接;所述第七晶体管m7的第一端与所述第六晶体管m6的第二端连接,所述第七晶体管m7的控制端连接于所述第二使能信号enn,所述第七晶体管m7的第二端接地。

[0080]

作为一种可选的实施例,参见图7,该防过冲电路100还包括第五晶体管m5、第六晶体管m6和第七晶体管m7,第五晶体管m5为pmos晶体管,第六晶体管m6为pmos晶体管,第七晶体管m7为nmos晶体管,第五晶体管m5的源极(第一端)和电源电压avd连接,第五晶体管m5的栅极(控制端)接收第一使能信号enp,第五晶体管m5的漏极(第二端)和第一晶体管m1的漏极(第二端)连接,第六晶体管m6的源极(第一端)和第一晶体管m1的漏极(第二端)连接,第六晶体管m6的栅极接收第二使能信号enn,第六晶体管m6的漏极(第二端)和电容的上极板连接,第七晶体管m7的漏极(第一端)和第六晶体管m6的漏极(第二端)连接,第七晶体管m7的栅极(控制端)接收第二使能信号enn,第七晶体管m7的源极(第二端)接地。

[0081]

第五晶体管m5、第六晶体管m6和第七晶体管m7均起到电荷泄放电路230的作用,第一使能信号enp和第二使能信号enn均为控制信号,第一使能信号enp和第二使能信号enn互为相反,在上电过程中,第一使能信号enp为高电平,第二使能信号enn为低电平,第五晶体管m5和第七晶体管m7截止,第六晶体管m6导通,使得防过冲电路100正常工作;当目标电路上电完成之后,第一使能信号enp为低电平,第二使能信号enn为高电平,第五晶体管m5和第七晶体管m7导通,第六晶体管m6截止,电容上极板的电荷可以通过第七晶体管m7释放到地,并且通过第六晶体管m6将第一晶体管m1和电容隔开,可以保证上电完成后电容上极板的初始电压为0,从而确保了防过冲电路100下次上电时正常工作。本技术实施例中通过第五晶体管m5、第六晶体管m6和第七晶体管m7对防过冲电路100中的电子器件进行隔开,在不影响防过冲电路100正常使用的情况下,可以有效保证防过冲电路100在每次上电时的初始值准确,从而保证了该防过冲电路100能正常工作。

[0082]

还需要说明的是,第一使能信号enp和第二使能信号enn可以通过控制器提供,也可以通过反相器、与门、非门、异或门等数字芯片按照一定规则进行组合后提供,具体可以根据实际情况进行确定。

[0083]

本技术实施例提供一种上电防过冲电路100,通过该防过冲电路100对目标电路进行防电压过冲,在目标电路的电源电压avd上电过程中,随着瞬时电压的升高,第一晶体管m1开始导通,而第二晶体管m2为第一晶体管m1的镜像管,第一晶体管m1也开始导通,并且输出第一电流信号;随着瞬时电压继续升高,第三晶体管m3也开始导通,输出第二电流信号,由于第一电流信号大于第二电流信号,通过第一电流信号和第二电流信号之间的差值,可以对第四晶体管m4的栅极电容进行充电,当第四晶体管m4的栅源电压大于阈值电压时,第四晶体管m4导通,目标电路在电压输出端口v

out

处累积的电荷可以通过第四晶体管m4排出,从而可以防止电压过冲,保证了目标电路正常工作,提高了目标电路的稳定性。当目标电路的电源逐渐稳定,上升到额定电压,电容上极板充电到该额定电压,由于此时第一晶体管m1的栅源电压为0,因此第一晶体管m1截止,由于镜像管的作用,第二晶体管m2也相应截止,第四晶体管m4的栅极的电压通过第三晶体管m3的导通电流释放到地,使得第四晶体管m4截止,不再释放电荷,从而在目标电路上电完成后,防过冲电路100不再工作,以保证后续电路继续正常工作。并且,通过第五晶体管m5、第六晶体管m6和第七晶体管m7对防过冲电路100中的电子器件进行隔开,在不影响防过冲电路100正常使用的情况下,可以有效保证防过冲电路100在每次上电时的初始值准确,从而保证了该防过冲电路100能正常工作。最后,仅仅通过若干晶体管和一个电容就可以实现整个防过冲电路100,具有结构简单、使用方便、占用面积小和成本低的优点。

[0084]

本技术实施例提供的一种带隙基准电路400,该带隙基准电路400的结构如图8所示,该带隙基准电路400包括上述描述的防过冲电路100和带隙基准单元300,将该带隙基准单元300作为防过冲电路100的目标电路,两者组成防过冲的带隙基准电路400,此处的带隙基准单元300具体结构见图中300模块所示,mb1、mb2和mb3为pmos晶体管,r1、r2为电阻,q1、q2和q3为pnp型三极管,这些器件和运算放大器a1构成带隙基准单元300。

[0085]

对于带隙基准单元300,在目标电路上电之初,vx点电压接近0,随着电源的瞬时电压上升,运算放大器a1给vx点充电,由于vx点的寄生电容(pmos管mb1、mb2和mb3的栅极寄生电容)存在,vx点电压变化速度慢于电源的瞬时电压上升速度。当电源的瞬时电压分别上升到为vx v

th1

、vx v

th2

、vx v

th3

时,v

th1

表示mb1的阈值电压,v

th2

表示mb2的阈值电压,v

th3

表示mb3的阈值电压,mb1、mb2和mb3分别导通,内部环路开始建立,vx同样缓慢上升。当电源的瞬时上升到电源的额定电压时,vx点还没有稳定,且vx的电压值远小于正常工作时的电压。此时,对于pmos管mb3来说,栅源电压较大,使流过mb3的电流远大于流过电阻r2和q3的电流,两者之间的电流差会给电压输出端口v

out

的寄生电容充电,使电压输出端口v

out

电压上升,产生过冲。

[0086]

传统方法中通常为了减小过冲,常在电压输出端口v

out

处添加rc低通滤波网络,以过滤掉过冲,但该方法因为加入了电容c,通常在面积上较大。针对该情况,本技术实施例提供的一种防过冲的带隙基准电路400,通过在带隙基准电路中增加防过冲电路100,构成防过冲的带隙基准电路400,该防过冲的带隙基准电路400通过防过冲电路100释放v

out

处累积的电荷,防止电压过冲,其具体原理可以参考上述实施例,本技术实施例对此不再赘述,并且电路结构简洁,使用器件少,在带隙基准电路正常工作是不会产生额外功耗。

[0087]

本技术实施例提供的一种线性稳压源电路600,该线性稳压源电路600结构如图9所示,该线性稳压源电路600包括防过冲电路100和线性稳压源单元500,此处的线性稳压源单元500可以是传统的稳压源电路,将线性稳压源单元500作为防过冲电路100的目标电路,即可得到防过冲的线性稳压源电路600。

[0088]

该线性稳压源具体结构如图9中500所示,其中ml1、ml2、ml5、ml6为nmos晶体管,ml3、ml4、ml7为pmos晶体管,其中nmos管ml1、ml2、ml5和pmos管ml3、ml4共同构成一个运算放大器。在目标电路上电之前,各点电压均为0v。当目标电路刚开始上电时,由于ml4为二极管接法,ml4的栅极和漏极通过ml4从电源电压avd汲取电流,从而使vx点通过ml3管充电,此时ml7管处于关断状态,并且ml2管的栅极电压为0。当目标电路上电过程中电源的瞬时电压达到一定幅值时,运算放大器开始工作,此时负反馈环路还没有建立,运算放大器工作在比较器状态,并且有vref》ml2管栅极电压,从而使vx翻转为0v,由于ml7管一般在设计中w/l(宽度与长度之比)取值较大,此时ml7管的栅源电压大于ml7的阈值电压,从而使ml7管导通,并且有较大电流为负载电容充电。当负载电容大小固定时,其存储的电荷量与ml7的电流和导通时间成正比,在这个过程中容易在电压输出端口v

out

处产生过冲,过冲的值与ml7尺寸大小正相关,与负载电容大小负相关。

[0089]

传统的避免线性稳压源过冲的方法中,当环路建立之后,负反馈最终会使得v

out

=vref

×

r2/(r1 r2),但是负载电容上由于上电过程中的大电流储存了大量电荷,使得v

out

》vref

×

r2/(r1 r2),而此时只能通过负载电阻rl和r1、r2的电阻通路来给电容cl放电,从而使电压稳定到v

out

=vref

×

r2/(r1 r2)。通常为了减小过冲,通过增加负载电容cl,但是增

大负载电容cl对于线性稳压源的负反馈系统的稳定性提出更大的挑战,同时也对片外集成提出更高的要求。针对该问题,本技术实施例提供的一种防过冲的线性稳压源电路600,通过在线性稳压源单元500中增加防过冲电路100,构成防过冲的线性稳压源电路600,该防过冲的线性稳压源电路600通过防过冲电路100释放v

out

处累积的电荷,防止电压过冲,其具体原理可以参考上述实施例,本技术实施例对此不再赘述,并且电路结构简洁,使用器件少,在线性稳压源单元500正常工作是不会产生额外功耗。

[0090]

本技术实施例提供的一种防过冲的电压产生电路,该防过冲的电压产生电路结构如图10所示,其中电源电压avd通常为3.3v或者5v,带隙基准电路产生参考电压vref,a1为运算放大器,m1为pmos管,r1、r2为分压电阻,由运算放大器a1、pmos管m1、分压电阻r1和r2共同构成传统的线性稳压源,rl、cl和数字电路均为线性稳压源的负载。其中运算放大器a1为负反馈连接方式。

[0091]

工作原理如下:带隙基准电路产生参考电压vref,由于运算放大器a1为负反馈连接方式,由运算放大器的正负输入端的虚短特性可推出运算放大器a1的正负输入端电压均为vref,而v

out

通过r1、r2的分压产生vref,可推出输出电压v

out

=vref

×

r2/(r1 r2),pmos管m1在保证输出电压v

out

=vref

×

r2/(r1 r2)的前提下,提供输出电流驱动电阻rl和数字电路。

[0092]

数字电路通常由数字器件构成,为了减小数字电路的动态功耗,通常工作电压较低(如1.5v),而为了集成度和工作速度考虑,数字电路中的数字器件通常使用工艺推荐的最小沟道长度l,器件的电压耐受能力也是有限的。传统结构电压v

out

产生电路的其中一个问题就是在avd上电的过程中,带隙基准的输出vref和线性稳压源的输出v

out

都会有电压过冲,而电压过冲可能造成v

out

下的数字电路存在如下问题:当过冲幅值较大或持续时间较长时,可能会导致数字电路中电路元器件的失效和损坏。针对该问题,本技术实施例提供的一种防过冲的电压产生电路,通过防过冲电路100可以防止产生的电压过冲,其具体原理可以参考上述实施例,本技术实施例对此不再赘述,从而可以保证数字电路中电路元器件不会被损坏,并且电路结构简洁,使用器件少,在线性稳压源单元500正常工作是不会产生额外功耗。

[0093]

本技术实施例还提供一种芯片,该芯片包括上述的上电防过冲电路100。芯片(integrated circuit,ic)可以是但不限于是soc(system on chip,芯片级系统)芯片、sip(system in package,系统级封装)芯片。该芯片通过在上电过程中释放电压输出端口v

out

处累积的电荷,能够解决电压过冲的技术问题。

[0094]

本技术实施例还提供一种电子设备,如图11所示,该电子设备700包括设备主体以及设于设备主题内的如上述的芯片。其中,该电子设备700可以是但不限于体重秤、体脂秤、营养秤、红外电子体温计、脉搏血氧仪、人体成分分析仪、移动电源、无线充电器、快充充电器、车载充电器、适配器、显示器、usb(universal serial bus,通用串行总线)扩展坞、触控笔、真无线耳机、汽车中控屛、汽车、智能穿戴设备、移动终端、智能家居设备。智能穿戴设备包括但不限于智能手表、智能手环、颈椎按摩仪、tws(true wireless stereo,真无线智能)耳机。移动终端包括但不限于智能手机、笔记本电脑、平板电脑、pos(point of sales terminal,销售点终端)机。智能家居设备包括但不限于智能插座、智能电饭煲、智能扫地机、智能灯。

[0095]

所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各功能单元、模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能单元、模块完成,即将所述装置的内部结构划分成不同的功能单元或模块,以完成以上描述的全部或者部分功能。

[0096]

以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。