一种智能布置光刻掩膜版制版图纸的方法与流程

- 国知局

- 2024-06-21 12:35:07

本发明涉及半导体封装,更具体涉及一种智能布置光刻掩膜版制版图纸的方法。

背景技术:

1、在传统设计中,光刻掩膜版的制版文件是由手动绘制,光刻掩膜版制版文件一般由三个小单元(单颗设计芯片di e、对位/测试芯片mark d ie及无效芯片dummy d i e)阵列成三个大的单元:第一单元域(fie l d1/f1)、第二单元域(fie l d2/f2)、第三单元域(fie l d3/f3)组成。

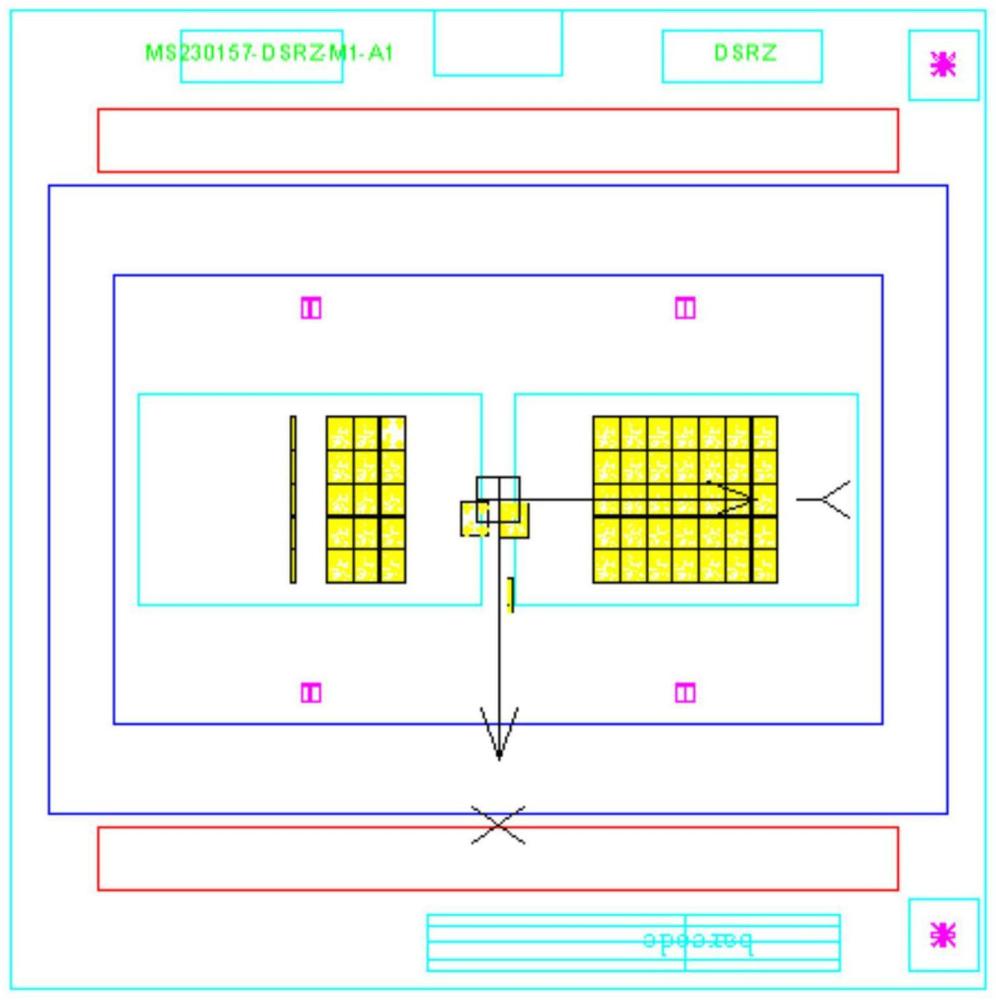

2、f1、f2、f3是曝光mappi ng作业时的单个曝光的区域(如图一所示),在手动绘制光刻掩膜版制版文件时,经常会出现fie l d位置在光刻掩模版模板中放置不居中、同一产品不同层的光刻掩膜版制版文件的名称需要重复手动输入,经常出现文件名称输入错误的现象,同一产品不同层的光刻掩膜版制版文件中的fie l d图形是单个小单元图形重复阵列得出,重复阵列浪费时间且阵列的行列数容易输错,导致各层fie l d的尺寸不一致,上述问题均会导致光刻掩膜版报废,无法使用,因此影响产品交期以及成本。

3、传统的手动绘制光刻掩膜版的制版文件方法,由于人工操作的不可控性,会容易出现遗误差,极大可能性会使制作的光刻版报废,造成产品返工延误交期,重新制版增加成本。

4、因此,亟需提供一种能够智能布置光刻掩膜版制版图纸的方法。

技术实现思路

1、为了解决上述问题,本发明提供了智能布置光刻掩膜版制版图纸的方法,该方法能够有效避免人工复判缺陷芯片时出现误判,也通过本发明能够保证缺陷芯片全部复判到位;极大的提高芯片检测的准确性最大可能的保证交期与节约成本。

2、本发明公开了一种智能布置光刻掩膜版制版图纸的方法,该方法包括以下步骤:

3、s1、建立光刻掩膜版数据库,所述数据库存储有多个封装结构的制版文件,每个制版文件名称唯一对应一个封装结构;

4、s2、建立第一cad文件,在第一cad文件中新建光刻掩膜版模板,所述光刻掩膜版模板包括第一有效区域框和第二有效区域框;在第一有效区域框和第二有效区域框内完成待制版封装产品的晶圆图谱,所述晶圆图谱包括完成植球布局且需要制版的所有图层;

5、s3、剥离待制版封装产品需要制版的单个图层,并将该图层的图形放置到第一cad文件中的第一有效区域框和/或第二有效区域框;

6、s4、根据待制版封装产品调用数据库中对应的制版文件,形成制版图纸。

7、在一些实施方式中,步骤s3中,晶圆图谱的设计方法为:

8、a、根据待制版封装产品,在第一cad文件中绘制正常芯片、对位/测试芯片和无效芯片3种芯片,并分别建块;完成f1、f2、f3三种不同的植球布局;

9、b、在第一有效区域框内定义f1的外框,选取f1外框的一个顶点坐标设置正常芯片外框,并以该正常芯片作为起始芯片,在f1外框范围内向x、y方向阵列所有正常芯片的外框;

10、c、在第二有效区域框内定义f2、f3的外框,f2、f3呈上下位置关系布置,且f2、f3之间的间距为4000-8000μm;按照b中阵列设置方法,在f2外框范围内向x、y方向阵列所有对位/测试芯片的外框,在f3外框范围内向x、y方向阵列所有无效芯片的外框;

11、d、将正常芯片、对位/测试芯片和无效芯片分别放置到f1、f2、f3的相应位置。

12、在一些实施方式中,步骤c中,第二有效区域框内f2、f3的上下位置通过修改waferid在wafer上的位置来确定。

13、在一些实施方式中,f1的外框在第一有效区域框内居中位置放置;f2、f3的外框在第二有效区域框内居中位置放置。

14、在一些实施方式中,执行步骤d时,可以先在步骤c中将f1、f2、f3中需要放置不同芯片的外框分别定义为颜色a、颜色b和颜色c;3种芯片再按照颜色区分分别放置到f1、f2、f3中。

15、与现有技术相比,本发明的有益效果是:

16、本发明能够节约制版图纸的设计时间,在提高设计效率同时也能够减少审核人员的工作量,如同一封装结构产品只需检查一层单元域尺寸,位置是否居中,无需每层重复测量。

17、本发明根据封装产品尺寸自动绘制光刻掩膜版制版文件,可有效避免各种人为重复操作的误差,极大的提高制版文件准确性,避免返工,避免重新制版带来的重大损失,最大可能的保证交期与节约成本。

技术特征:1.一种智能布置光刻掩膜版制版图纸的方法,其特征在于,所述方法包括以下步骤:

2.根据权利要求1所述的一种智能布置光刻掩膜版制版图纸的方法,其特征在于,步骤s3中,晶圆图谱的设计方法为:

3.根据权利要求2所述的一种智能布置光刻掩膜版制版图纸的方法,其特征在于,步骤c中,第二有效区域框内f2、f3的上下位置通过修改wafer id在wafer上的位置来确定。

4.根据权利要求3所述的一种智能布置光刻掩膜版制版图纸的方法,其特征在于,f1的外框在第一有效区域框内居中位置放置;f2、f3的外框在第二有效区域框内居中位置放置。

5.根据权利要求4所述的一种智能布置光刻掩膜版制版图纸的方法,其特征在于,执行步骤d时,可以先在步骤c中将f1、f2、f3中需要放置不同芯片的外框分别定义为颜色a、颜色b和颜色c;3种芯片再按照颜色区分分别放置到f1、f2、f3中。

技术总结本发明公开了一种智能布置光刻掩膜版制版图纸的方法,包括以下步骤:建立光刻掩膜版数据库,数据库存储有多个封装结构的制版文件,每个制版文件名称唯一对应一个封装结构;建立第一CAD文件,在第一CAD文件中新建包括第一有效区域框和第二有效区域框的光刻掩膜版模板;完成待制版封装产品的晶圆图谱;剥离待制版封装产品需要制版的单个图层,并将该图层的图形放置到第一CAD文件中的第一有效区域框和/或第二有效区域框;根据待制版封装产品调用数据库中对应的制版文件,形成制版图纸。本发明能够节约制版图纸的设计时间,在提高设计效率同时也能够减少审核人员的工作量,还可有效避免各种人为重复操作的误差,最大可能的保证交期与节约成本。技术研发人员:张玉,谢雨龙,王晓平,张亚文,刘实,姜乔受保护的技术使用者:江苏芯德半导体科技有限公司技术研发日:技术公布日:2024/6/11本文地址:https://www.jishuxx.com/zhuanli/20240618/28017.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。