一种应用于3DIC的正/背面套刻集成方法

- 国知局

- 2024-06-21 12:37:22

本发明属于微纳制造,具体涉及一种应用于3d ic的正/背面高精度对准集成方法。

背景技术:

1、以3d soc(system on chip)为代表的系统级芯片成为延续摩尔定律的方案之一。立方体式的3d集成芯片解决方案,可以在垂直方向上提供非常高密度的互连,在缩减芯片面积、降低功耗、缩减成本的同时,能够提供更高水平的性能。特别是,作为先进节点芯片微缩的一种优化路径,背面配电网络(bpdn)使用纳米通孔技术将所有功率(电源和供电网络)直接路由到晶体管的背面,从而将功率传输从背面与保留在芯片正面内部的数据传输垂直互连。通过该电源电路和数据传输(i/o)互连分开的方式,可改善ir-drop压降特性,从而实现更快的晶体管开关,同时在芯片顶部实现更密集的信号路由,并且简化的布线可以更快地连接电阻和电容,进而对芯片信号完整性也有好处。为实现以背部供电网络等为代表的3d ic集成技术方案,往往都将利用到晶圆到晶圆序列工艺(wafer-to-wafer sequentialprocessing,wwsp)。例如,晶圆到晶圆混合键合、晶圆翻转(flip)及背部减薄等方法,执行来自两个晶圆衬底的后端生产线(beol:back end ofline)流程,实现芯片到芯片3d直接的互连。与此同时,如何实现不同晶圆衬底各自后道工艺之间、以及晶圆翻转之后正/背面晶体管或者结构的高精度对准集成,成为推动3d ic发展的关键共性技术难题。

2、采用高端光刻机,如(asml的twinscan nxe3400b euv、nxt2000i/2050i duv等),依赖高端设备自身配置的正/背面套刻集成系统,在芯片背面光刻过程中可实现<10nm的套刻精度,但是成本极其高昂。更关键的是,大部分双面光刻设备的背部套刻精度往往低于其正面套刻精度(如suss ma8双面接触式光刻机,正面对准精度优于±0.5μm,背面对准精度仅仅优于±1.0μm)。另外,关键问题在于现有集成方案中芯片正/背面图形的对准集成依赖于各自前道工艺所定位、集成于芯片正/背面的套刻标记(alignment标记),当光刻工艺(即正/背面套刻标记)的定位产生偏移误差时,随着误差持续传递,会导致后续工艺的对准集成过程中偏差更大,进而导致正/背面图案出现加大的overlay和对准偏差。

技术实现思路

1、鉴于以上所述技术的缺点,本发明目的在于提出一种应用于3d ic的正/背面套刻集成方法,其特征在于所述套刻集成方法,通过正/背面工艺共享同一组套刻标记(alignment标记)的方式,可有效提升芯片正/背面结构的对准精度,克服3d ic芯片制造过程中所面临的正/背面高精度集成难题。

2、本发明的技术问题通过以下的技术方案予以解决:

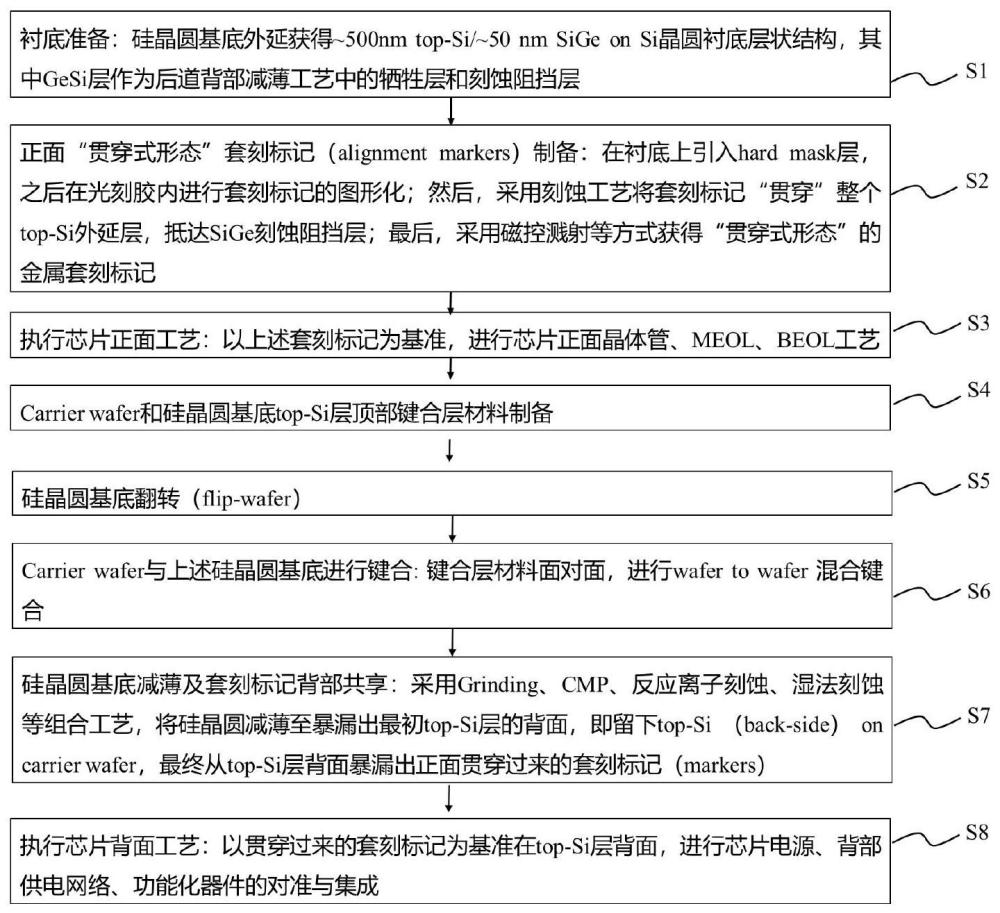

3、为实现上述目的及其他相关目的,本发明提供了一种应用于3d ic的正/背面套刻集成方法,包括步骤:步骤1)外延衬底准备(top-si/sige-牺牲层on si基底);步骤2)正面“贯穿式形态”套刻标记(alignment标记)制备;步骤3)芯片正面器件/结构制备:在硅衬底所外延的top-si层顶部(正面),以“贯穿式形态”套刻标记为基准,确定光刻和图形化位置,套刻定义正面芯片结构;步骤4)在carrier wafer和硅基底top-si层同时沉积键合层材料:如sicn;步骤5)硅基底晶圆翻转;步骤6)carrier wafer和硅基底top-si层顶部的键合层材料face to face键合;步骤7)硅基底背部减薄直至暴漏出从top-si层正面贯穿过来的套刻标记;步骤8)芯片背面结构制备:共享正面贯穿过来的同一组套刻标记,以此作为基准,确定背面光刻和图形化位置,套刻定义背面器件/结构,实现正/背面器件/结构的高精度对准和集成。

4、具体包括以下步骤:

5、步骤1,衬底制备(top-si/sige-牺牲层on si衬底):采用lpcvd或者外延等技术在硅基底上获得~50nm sige/500nm top-si叠层结构;

6、步骤2,正面“贯穿式形态”套刻标记(alignment标记)制备:

7、步骤21,cvd沉积sio2作为刻蚀掩模,即硬掩模;

8、步骤22,芯片正面套刻标记图形化:涂覆光刻胶、并进行曝光和显影,在光刻胶材料内获得套刻标记结构;

9、步骤23,硬掩模刻蚀及去胶:以光刻胶结构为掩模,采用干法刻蚀或者湿法刻蚀手段,刻蚀硬掩模,将标记转移至硬掩模层。之后,采用等离子体干法去除光刻胶;

10、步骤24,衬底top-si层刻蚀:以硬掩模层标记为掩模,采用干法刻蚀或者湿法刻蚀手段,刻蚀top-si层,刻蚀深度直至贯穿到sige牺牲层(刻蚀阻挡层),获得正面“贯穿式形态”套刻标记;

11、步骤25,正面“贯穿式形态”套刻标记金属化:采用磁控溅射,对刻蚀后的标记进行金属填充。

12、步骤3)芯片正面结构制备:在硅衬底所外延的top-si层顶部(正面),以“贯穿式形态”套刻标记为基准,确定光刻和图形化位置,套刻定义正面芯片结构;

13、步骤4)在carrier wafer和硅基底top-si层顶部同时沉积键合层材料:如sicn;

14、步骤5)硅基底晶圆翻转;

15、步骤6)采用wafer to wafer方式,将carrier wafer和硅基底top-si层顶部的键合层材料face to face键合;

16、步骤7)硅基底背部减薄直至暴漏出从top-si层正面贯穿过来的套刻标记(alignment标记):去除硅基底,获得top-si/bonding layer/carrier wafer叠层结构。此时,芯片最顶部为最初在硅基底上所外延top-si层的背面,并且暴漏出了正面贯穿过来的同一套套刻标记;

17、步骤8)芯片背面结构制备:在晶圆翻转、减薄后的top-si层顶部(背面),共享正面贯穿过来的同一组套刻标记,作为基准,确定光刻和图形化位置,套刻定义背面芯片结构。最终,实现3d ic正/背面器件结构的高精度对准和集成。

18、作为本发明的一种应用于3d ic的正/背面套刻集成方法的一种优选方案,在一些实施例中,所述步骤1)中采用~500nm top-si/50nm sige on si基底作为晶圆衬底,因为其内部存在一个sige的牺牲层/刻蚀阻挡层,有助于晶圆背部减薄厚度推进至~500nm(甚至更低)的极端减薄厚度。

19、作为本发明的一种应用于3d ic的正/背面套刻集成方法的一种优选方案,在一些实施例中,所述步骤2)中正面“贯穿式形态”套刻标记(alignment标记)的优点如下:

20、第一,能够减小3d ic中至少一道光刻步骤,即去除背面套刻标记的制备过程,缩减工艺复杂度和降低工艺成本;

21、第二,通过刻蚀方法,将正面套刻标记1:1且高精度的传递到背面,能大幅提升背面套刻标记的定位精度,以此提升后续工艺的精准度,降低overlay和对准误差。

22、如上所述,作为本发明的种应用于3d ic的正/背面套刻集成方法,具有以下有益效果:

23、(1)该方法和现代cmos工艺完全兼容,可引进fab进行批量化生产;

24、(2)该方法不仅可以应用于背部供电网络等3d ic的集成过程中,还适用于光电子器件(如3d堆叠cmos图像传感器、ccd、背/正面照射式inp/ingaas偏振芯片、超表面功能集成化探测器件等)、以及sip、chiplet等封装架构中。

本文地址:https://www.jishuxx.com/zhuanli/20240618/28255.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表