有机电致发光显示装置的制作方法

- 国知局

- 2024-06-21 13:47:51

本技术涉及显示,具体涉及一种有机电致发光显示装置。

背景技术:

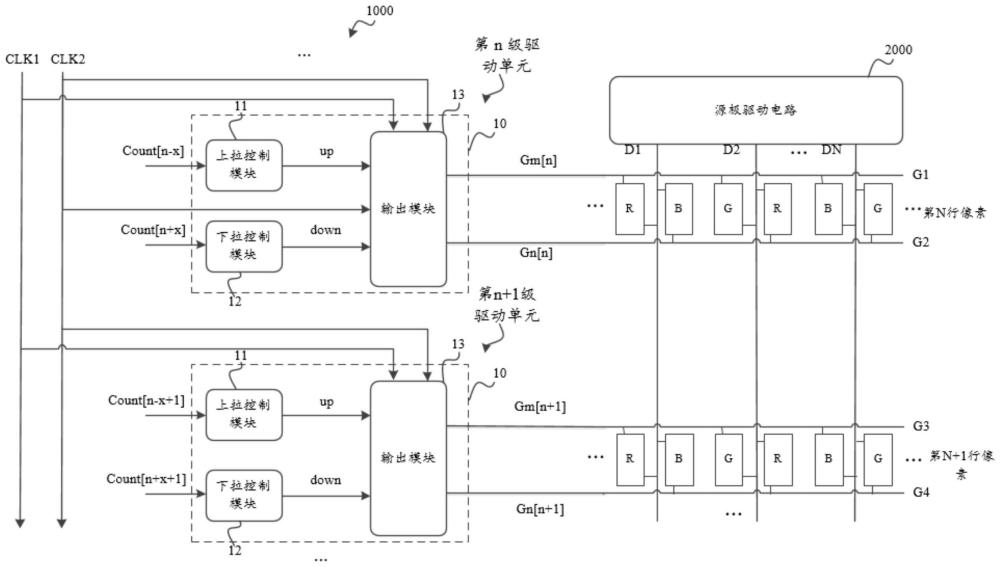

1、目前,为适配与有机电致发光显示装置绑定的芯片的引脚数量有限或者有机电致发光显示装置的边框宽度较窄的情形,相关技术中采用数据信号线共享(date lineshare,dls)技术来减少显示面板中数据信号线的数量。参阅图1,其中,数据信号线d1与第m列像素单元以及第m+1列像素单元电连接,数据信号线d2与第m+2列像素单元以及第m+3列像素单元电连接,数据信号线d3与第m+4列像素单元以及第m+5列像素单元电连接,即每条数据信号线与两列子像素单元电连接,从而使得数据信号线的数量减少一半。

2、然而,虽然采用数据信号线共享技术可以减少数据信号线的数量,但有机电致发光显示装置的栅极驱动电路需要针对每一行像素单元设置两个驱动电路,两个驱动电路控制同一行像素单元,这导致了栅极驱动电路的结构较为复杂的问题。

技术实现思路

1、本技术提供一种有机电致发光显示装置,旨在解决采用数据信号线共享技术的有机电致发光显示装置中的栅极驱动电路的结构复杂的技术问题。

2、第一方面,本技术提供一种有机电致发光显示装置,包括:

3、呈阵列设置的多个像素;

4、多条数据线,一条数据线与相邻的两列像素电连接;

5、多组扫描线,一组扫描线与一行像素电连接,一组扫描线包括第一扫描线和第二扫描线,在一行像素中,与第一扫描线电连接的像素和与第二扫描线电连接的像素交错排列;

6、源极驱动电路,源极驱动电路与多条数据线电连接;以及

7、栅极驱动电路,栅极驱动电路包括多级驱动单元,一级驱动单元与一组扫描线电连接,多级驱动单元中的第n级驱动单元包括驱动信号输出模块,驱动信号输出模块包括:

8、上拉控制模块,上拉控制模块与第n-x级驱动单元电连接,上拉控制模块用于接收第n-x级驱动单元的下传级传信号输出端输出的下传级传信号并输出上拉控制信号;

9、下拉控制模块,下拉控制模块与第n+x级驱动单元电连接,下拉控制模块用于接收第n+x级驱动单元的上传级传信号输出端输出的上传级传信号并输出下拉控制信号;

10、输出模块,输出模块与上拉控制模块和下拉控制模块电连接,以及与第一扫描线和第二扫描线电连接,输出模块用于根据上拉控制信号、下拉控制信号以及第一时钟信号生成第一栅极驱动信号,并向第一扫描线输出第一栅极驱动信号,以及用于根据上拉控制信号、下拉控制信号以及第二时钟信号生成第二栅极驱动信号,并向第二扫描线输出第二栅极驱动信号,其中,第一时钟信号与第二时钟信号不同步,n和x均为正整数,x<n。

11、在一些实施例中,有机电致发光显示装置还包括:

12、多组补偿线,一组补偿线与一行像素电连接,一组补偿线包括第一补偿线和第二补偿线,在同一行像素中,第一补偿线和第一扫描线电连接相同的像素,第二补偿线和第二扫描线电连接相同的像素;

13、第n级驱动单元还包括:

14、驱动信号补偿模块,驱动信号补偿模块与第n-1级驱动单元电连接,驱动信号补偿模块用于根据第n-1级驱动单元输出的第一栅极驱动信号生成第一补偿信号,并向第一补偿线输出第一补偿信号,以及根据第n-1级驱动单元输出的第二栅极驱动信号生成第二补偿信号,并向第二补偿线输出第二补偿信号;

15、其中,第一补偿信号对第一扫描线电连接的像素进行的第一补偿时长的亮度补偿,第二补偿信号对第二扫描线电连接的像素进行第二补偿时长的亮度补偿,第一补偿时长与第二补偿时长相等。

16、在一些实施例中,驱动信号补偿模块包括第一子补偿模块以及第二子补偿模块;

17、第一子补偿模块用于根据第n-1级驱动单元输出的第一栅极驱动信号以及补偿启动信号输出第一补偿信号;

18、第二子补偿模块用于根据第n-1级驱动单元输出的第二栅极驱动信号以及第一补偿信号输出第二补偿信号;

19、其中,第一补偿信号的下降沿在第二补偿信号的下降沿之后。

20、在一些实施例中,有机电致发光显示装置还包括:

21、多组复位线,一组复位线与一行像素电连接,一组复位线包括第一复位线和第二复位线,在同一行像素中,第一复位线和第一扫描线电连接相同的像素,第二复位线和第二扫描线电连接相同的像素;

22、输出模块还用于根据上拉控制信号、下拉控制模块以及第三时钟信号生成第一复位信号,并向第一复位线输出第一复位信号,以及根据上拉控制信号、下拉控制模块以及第四时钟信号生成第二复位信号,并向第二复位线输出第二复位信号;

23、第一复位信号用于对第一扫描线电连接的像素进行亮度补偿复位,第二复位信号用于对第一扫描线电连接的像素进行亮度补偿复位,第三时钟信号与第四时钟信号不同步;

24、其中,第一复位信号的下降沿与第一补偿信号的下降沿之间相差第一补偿时长,第二复位信号的下降沿与第二补偿信号的下降沿之间相差第二补偿时长,且补偿启动信号为第一复位信号与第二复位信号中的一者。

25、在一些实施例中,第二子补偿模块包括第一晶体管以及第二晶体管;

26、第一晶体管的第一端与第一子补偿模块的输出端电连接,第一晶体管的第二端与第二晶体管的第一端电连接,第二晶体管的第二端与接地端电连接;

27、第一晶体管与第二晶体管之间的第一节点输出第二补偿信号,第一晶体管为低电位导通晶体管,第二晶体管为高电位导通晶体管;

28、第一晶体管以及第二晶体管的控制端与第n-1级驱动单元的第二栅极驱动信号输出端电连接。

29、在一些实施例中,第一子补偿模块包括第三晶体管以及第四晶体管;

30、第三晶体管的第一端与电源端电连接,第三晶体管的第二端与第四晶体管的第一端电连接,第四晶体管的第二端与接地端电连接,第一晶体管的第一端电连接于第三晶体管与第四晶体管之间的第二节点;

31、第二节点用作第一补偿信号输出端,第三晶体管的控制端与第一复位信号输出端或者第二复位信号输出端电连接,第四晶体管与第n-1级驱动单元的第一栅极驱动信号输出端电连接。

32、在一些实施例中,第一子补偿模块还包括第五晶体管、第六晶体管、第七晶体管以及第八晶体管;

33、第五晶体管的第一端与电源端电连接,第五晶体管的第二端与第六晶体管的第一端电连接,第六晶体管的第二端与接地端电连接,第三晶体管的控制端电连接于第五晶体管与第六晶体管之间的第三节点;

34、第七晶体管的第一端与电源端电连接,第七晶体管的第二端与第八晶体管的第一端电连接,第八晶体管的第二端与接地端电连接,第四晶体管的控制端电连接于第七晶体管与第八晶体管之间的第四节点;

35、第五晶体管与第一复位信号输出端电连接,第六晶体管与第n-1级驱动单元的第一栅极驱动信号输出端电连接;

36、第七晶体管与第n-1级驱动单元的第一栅极驱动信号输出端电连接,第八晶体管与第一复位信号输出端电连接。

37、在一些实施例中,第二子补偿模块还包括第九晶体管、第十晶体管、第十一晶体管以及第十二晶体管;

38、第九晶体管的第一端与电源端电连接,第九晶体管的第二端与第十晶体管的第一端电连接,第十晶体管的第二端与接地端电连接,第一晶体管的控制端电连接于第九晶体管与第十晶体管之间的第五节点;

39、第十一晶体管的第一端与电源端电连接,第十一晶体管的第二端与第十二晶体管的第一端电连接,第十二晶体管的第二端与接地端电连接,第二晶体管的控制端电连接于第十一晶体管与第十二晶体管之间的第六节点;

40、其中,第九晶体管以及第十一晶体管的控制端与第n-1级驱动单元的第二栅极驱动信号输出端电连接,且第十晶体管以及第十二晶体管的控制端电连接于第四节点。

41、在一些实施例中,输出模块包括第一子晶体管、第二子晶体管、第三子晶体管以及第四子晶体管;

42、第一子晶体管的第一端与第一时钟信号输出端电连接,第一子晶体管的第二端与第二子晶体管的第一端电连接,第二子晶体管的第二端电连接接地端,第一子晶体管与第二子晶体管之间的第一子节点用作第一栅极驱动信号输出端;

43、第三子晶体管的第一端与第二时钟信号输出端电连接,第三子晶体管的第二端与第四子晶体管的第一端电连接,第四子晶体管的第二端电连接接地端,第三子晶体管与第四子晶体管之间的第二子节点用作第二栅极驱动信号输出端;

44、第一子晶体管以及第三子晶体管的控制端与上拉控制信号输出端电连接,第二子晶体管以及第四子晶体管的控制端与下拉控制信号输出端电连接。

45、在一些实施例中,输出模块还包括第五子晶体管、第六子晶体管、第七子晶体管以及第八子晶体管;

46、第五子晶体管的第一端与第三时钟信号输出端电连接,第五子晶体管的第二端与第六子晶体管的第一端电连接,第六子晶体管的第二端电连接接地端,第五子晶体管与第六子晶体管之间的第三子节点用作第一复位信号输出端;

47、第七子晶体管的第一端用于接入第四时钟信号输出端电连接,第七子晶体管的第二端与第八子晶体管的第一端电连接,第八子晶体管的第二端电连接接地端,第七子晶体管与第八子晶体管之间的第四子节点用作第二复位信号输出端;

48、第五子晶体管以及第七子晶体管的控制端与上拉控制信号输出端电连接,第六子晶体管以及第八子晶体管的控制端与下拉控制信号输出端电连接。

49、在一些实施例中,还输出模块还包括第九子晶体管以及第十子晶体管;

50、第九子晶体管的第一端与第五时钟信号输出端电连接,第九子晶体管的第二端与第十子晶体管的第一端电连接,第十子晶体管的第二端电连接接地端,第九子晶体管与第十子晶体管之间的第五子节点用于输出级传信号;

51、第九子晶体管的控制端与上拉控制信号输出端电连接,第十子晶体管的控制端与下拉控制信号输出端电连接。

52、在本技术中,由于输出模块可以根据上拉控制信号、下拉控制信号以及第一时钟信号输出第一栅极驱动信号,并可以根据上拉控制信号、下拉控制信号以及第二时钟信号输出第二栅极驱动信号,因此可以利用第一栅极驱动信号驱动一行像素单元中一部分像素单元发光,并利用第二栅极驱动信号驱动一行像素单元中另一部分像素单元发光,当栅极驱动电路应用于数据信号线共享的像素驱动方案时,无需采用两个驱动单元驱动一行像素单元发光,进而有利于简化栅极驱动电路的结构并有利于实现显示面板的窄边框设计。

本文地址:https://www.jishuxx.com/zhuanli/20240618/34530.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种新型电子教学黑板

下一篇

返回列表