一种高性能扫码主板电路及主板的制作方法

- 国知局

- 2024-08-05 13:52:36

本技术涉及扫码设备领域,具体涉及一种高性能扫码主板电路及主板。

背景技术:

1、随着国人生活水平得提高,一维码、二维码等已逐渐在日常生活、生产中普及,给生活带来便捷的同时、很大程度上提高了生产效率。扫码自然离不开扫码设备,形态各异、功能多样、性能卓越的各种扫码终端应运而生。支付、快递录入等各种场景要求设备运行流畅,扫码识别率高,兼容性强等,但同时对设备成本控制要求也非常高。而现有的扫码设备通常功能单一,不能够兼容市面上广泛使用的不同扫码头。

技术实现思路

1、针对上述存在的问题,本实用新型的目的在于提供一种高性能扫码主板电路及主板,达到在保证扫码平板性能的同时提高兼容性的目的。

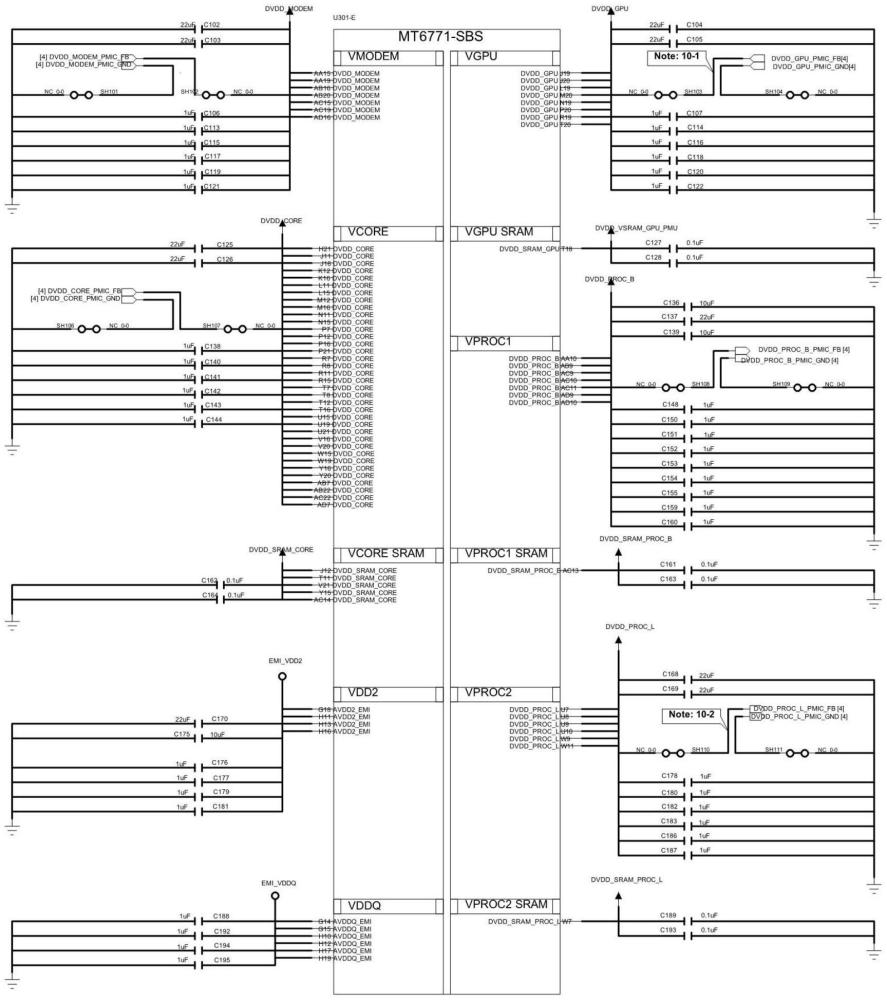

2、为实现上述目的,本实用新型提供了一种高性能主板电路,包括主控芯片和电源电路,所述主控芯片通过连接器可拆卸连接有多个扫码模组,所述连接器包括两通道mipi信号、多个电源接口、一组i2c信号和电源io控制口;所述主控芯片还连接有存储模块,所述存储模块包括分离式rom和ram,所述存储模块与所述扫码模组通信连接。

3、进一步,所述主控芯片通过i2c总线连接有电池连接器,所述电池连接器连接有电量计,所述电量计与所述主控芯片通讯连接。

4、进一步,所述主板电路还包括rfid模块,所述rfid模块电连接有第一电平转换器,所述第一电平转换器连接至所述电源电路。

5、进一步,所述rfid模块包括电源开关,所述电源开关选用30vp mos管。

6、进一步,所述主控芯片集成ap和md子系统,以实现多格式多媒体图像处理。

7、进一步,所述两通道mipi信号支持3组4通道c-phy接口,实现同时支持三路mipi图像处理。

8、进一步,所述i2c信号与所述主控芯片通讯连接,所述i2c信号和所述电源io控制口与所述第一电平转换器电连接。

9、进一步,所述rom选用emmc存储,所述rom通过8-bit位宽msdc接口与所述主控芯片的msdc0实现数据通讯,所述ram选用lpddr4x存储,所述ram通过16-bit数据位宽与所述主控芯片的emi0和emi1两组数据总线缓存接口实现通讯。

10、进一步,所述i2c总线的io电平连接有第二电平转换器,所述第二电平转换器连接有r859和r837,以实现对不同规格的所述电量计兼容。

11、本实施例进一步公开了一种主板,包括上述的主板电路。

12、本实用新型的有益效果是:

13、通过将多个扫码模组通过连接器电路可更换连接到主控芯片,可以实现在需要不同规格的扫码头是可以快速更换,无需更换完整的扫码枪,同时,通过将rom和ram设计为分离式,可以实现自由组合,根据扫码枪的用途合理选择,降低配置成本。

技术特征:1.一种高性能扫码主板电路,其特征在于,包括主控芯片和电源电路,所述主控芯片通过连接器可拆卸连接有多个扫码模组,所述连接器包括两通道mipi信号、多个电源接口、一组i2c信号和电源io控制口;

2.根据权利要求1所述的主板电路,其特征在于,所述主控芯片通过i2c总线连接有电池连接器,所述电池连接器连接有电量计,所述电量计与所述主控芯片通讯连接。

3.根据权利要求1所述的主板电路,其特征在于,所述主板电路还包括rfid模块,所述rfid模块电连接有第一电平转换器,所述第一电平转换器连接至所述电源电路。

4.根据权利要求3所述的主板电路,其特征在于,所述rfid模块包括电源开关,所述电源开关选用30vp mos管。

5.根据权利要求1所述的主板电路,其特征在于,所述主控芯片集成ap和md子系统,以实现多格式多媒体图像处理。

6.根据权利要求1所述的主板电路,其特征在于,所述两通道mipi信号支持3组4通道c-phy接口,实现同时支持三路mipi图像处理。

7.根据权利要求3所述的主板电路,其特征在于,所述i 2c信号与所述主控芯片通讯连接,所述i 2c信号和所述电源io控制口与所述第一电平转换器电连接。

8.根据权利要求1所述的主板电路,其特征在于,所述rom选用emmc存储,所述rom通过8-bit位宽msdc接口与所述主控芯片的msdc0实现数据通讯,所述ram选用lpddr4x存储,所述ram通过16-bit数据位宽与所述主控芯片的emi 0和emi 1两组数据总线缓存接口实现通讯。

9.根据权利要求2所述的主板电路,其特征在于,所述i 2c总线的io电平连接有第二电平转换器,所述第二电平转换器连接有r859和r837,以实现对不同规格的所述电量计兼容。

10.一种主板,其特征在于,包括如权利要求1-9任一所述的主板电路。

技术总结本技术公开了一种高性能主板电路,包括主控芯片和电源电路,所述主控芯片通过连接器可拆卸连接有多个扫码模组,所述连接器包括两通道MIPI信号、多个电源接口、一组I2C信号和电源IO控制口;所述主控芯片还连接有存储模块,所述存储模块包括分离式ROM和RAM,所述存储模块与所述扫码模组通信连接;通过将多个扫码模组通过连接器电路可更换连接到主控芯片,可以实现在需要不同规格的扫码头是可以快速更换,无需更换完整的扫码枪,同时,通过将ROM和RAM设计为分离式,可以实现自由组合,根据扫码枪的用途合理选择,降低配置成本。技术研发人员:柴成军,朱占伟受保护的技术使用者:上海天奕达电子科技有限公司技术研发日:20231204技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240720/269621.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表