一种基于绝缘体上硅的低应力硅基厚膜的制作方法

- 国知局

- 2024-07-27 12:33:04

[0001]本实用新型涉及一种基于绝缘体上硅的低应力硅基厚膜,属于半导体制备技术领域。背景技术:[0002]绝缘体上硅(silicon-on-insulator,soi)技术因具有功耗低、速度高、寄生电容小、抗辐照能力强等特点,被广泛应用于卫星、电子、计算机、航空航天等领域。根据器件层厚度的不同,沉积的膜层可分为厚膜和薄膜两类。厚膜通常指器件层厚度大于1μm,主要用于微机电系统(mems)和功率器件;薄膜指器件层厚度在0.1~1μm,主要用于互补金属氧化物半导体(cmos)等亚微米集成电路。[0003]近年来,随着mems和智能功率器件市场的迅速发展,硅基厚膜材料引起了产业界的广泛关注;但是通过常规方法制备的厚膜中残存应力,它的产生机制是由厚膜本身结构、缺陷及厚膜与基体间物理性能差异所决定,过大的拉伸残余应力(张应力)会使得膜结构发生破裂,而过大的压缩残余应力(压应力)则会使得晶圆片发生膨胀或者翘曲。上述两种情况都会增大工艺难度,并有可能使得器件失效。技术实现要素:[0004]针对上述现有技术存在的问题及不足,本实用新型目的在于克服制备得到的膜残余应力过大导致微器件单元甚至整个器件结构发生形变、失稳、信号误传导,乃至系统失效等难以避免的缺陷,提供一种基于绝缘体上硅的低应力硅基厚膜,该膜具有良好的绝缘性、稳定性和机械性。[0005]本实用新型的目的通过以下方案实现:所述基于绝缘体上硅的低应力硅基厚膜包括衬底硅层、硅氧化物层,包覆层和硅基厚膜层,衬底硅层上设有硅氧化物层,硅氧化物层上沉积有硅基厚膜层,硅基厚膜层上设有网格状沟槽,网格状沟槽将硅基薄膜分割成数个独立单元,网格状沟槽内填充有包覆层。[0006]优选的,本实用新型所述硅基厚膜层的厚度为1微米以上,硅氧化物层的厚度为2~3微米。[0007]优选的,本实用新型所述独立单元的尺寸为5-25mm×5-32mm;沟槽的宽度180~220nm,长度横跨整个衬底。[0008]优选的,本实用新型所述的厚膜材料的组分为sin、si3n4、sin2、si(oh)4或多晶硅,其他满足要求的膜材料也可以用于本实用新型。[0009]优选的,本实用新型所述沟槽填充材料为sio2或sion,其他满足要求的低应力填充材料也可以用于本实用新型。[0010]本实用新型有益效果是:[0011](1)本实用新型是对目前大应力硅基厚膜制备方法的有效改进,通过在沉积过程中增加刻蚀沟槽并填充低应力包覆层材料的工艺,将原本连续的硅基厚膜沉积过程划分为若干个重复制备低应力薄膜阶段,每个阶段均需要在沉积薄膜后刻蚀沟槽将硅基薄膜划分为数个独立单元,之后将沟槽中沉积低应力的包覆层材料,这样一方面可以改善沉积过程中,厚膜内部所受应力不均匀的情况,减小厚膜应力;另一方面,应力的减小,增大了所沉积的厚膜的最大厚度。[0012](2)本实用新型通过形成沟槽的方法释放应力,减小厚膜应力积累,增大了所能沉积的厚膜最大厚度;同时,本实用新型中所有的工艺与目前cmos工艺完全兼容,能够实现器件的大规模量产,有助于推动硅光子集成器件的广泛应用。附图说明[0013]图1是本实用新型所制备的低应力硅基厚膜的层结构示意图。[0014]图2是本实用新型所制备厚膜的俯视图。[0015]图1中:1-衬底硅层;2-硅氧化物层;3-包覆层;4-硅基厚膜层。具体实施方式[0016]下面结合实施例,对本实用新型的具体实施方式作进一步描述;以下实施例仅用于更加清楚地说明本实用新型的技术方案,而不能以此来限制本实用新型的保护范围。[0017]实施例1[0018]本实施例所述基于绝缘体上硅的低应力硅基厚膜包括衬底硅层、硅氧化物层,包覆层和硅基厚膜层,衬底硅层上设有硅氧化物层,硅氧化物层上沉积有硅基厚膜层,硅基厚膜层上设有网格状沟槽,沟槽的宽度为200nm,长度横跨整个衬底,网格状沟槽将硅基薄膜分割成数个独立单元,网格状沟槽内填充有包覆层;硅氧化物层的厚度为2微米,硅基厚膜层的厚度为2微米;所述独立单元的尺寸为32mm*25mm,所述的厚膜材料的组分为si3n4,沟槽填充材料为sio2;如图1和2所示。[0019]本实施例所述基于绝缘体上硅的低应力硅基厚膜通过以下方法制备得到:[0020](1)提供厚度为750微米的硅片作为衬底,衬底表面有热氧化生长的二氧化硅层,二氧化硅层的厚度为2微米,采用含有碱性溶液的清洗剂对所述半导体衬底及二氧化硅膜进行清洗。[0021](2)将步骤(1)预处理的衬底通过pecvd设备沉积一层厚度为500纳米的si3n4薄膜层;本实施例沉积硅基厚膜材料采用等离子体增强化学的气相沉积法,亦可采用任何合适的沉积工艺,均为常规方法,本实用新型对此并不做限定。[0022](3)通过刻蚀工艺,沿纵向与横向等间距刻蚀沟槽,沟槽的宽度为200nm,长度横跨整个衬底,将si3n4薄膜划分成若干个32mm*25mm规格的薄膜块。[0023](4)去胶并清洗后,用pecvd沉积方法,进行第二次沉积,沉积一层厚度为800纳米的低应力二氧化硅层。[0024](5)通过反向刻蚀sio2包覆层暴露出被二氧化硅层包覆的si3n4薄膜后,通过化学机械平坦化工艺得到平整的上表面;之后,重复(2)~(5)的步骤,重复次数为2,得到1微米厚度的si3n4薄膜,并保持晶圆低的翘曲度。[0025]实施例2[0026]本实施例所述基于绝缘体上硅的低应力硅基厚膜包括衬底硅层、硅氧化物层,包覆层和硅基厚膜层,衬底硅层上设有硅氧化物层,硅氧化物层上沉积有硅基厚膜层,硅基厚膜层上设有网格状沟槽,沟槽的宽度为180nm,长度横跨整个衬底,网格状沟槽将硅基薄膜分割成数个独立单元,网格状沟槽内填充有包覆层;硅氧化物层的厚度为3微米,硅基厚膜层的厚度为2微米;所述独立单元的尺寸为5×5,所述的厚膜材料的组分为sin,沟槽填充材料sion,如图1和2所示。[0027]实施例3[0028]本实施例所述基于绝缘体上硅的低应力硅基厚膜包括衬底硅层、硅氧化物层,包覆层和硅基厚膜层,衬底硅层上设有硅氧化物层,硅氧化物层上沉积有硅基厚膜层,硅基厚膜层上设有网格状沟槽,沟槽的宽度为220nm,长度横跨整个衬底,网格状沟槽将硅基薄膜分割成数个独立单元,网格状沟槽内填充有包覆层;硅氧化物层的厚度为2微米,硅基厚膜层的厚度为3微米;所述独立单元的尺寸为20mm×25mm,所述的厚膜材料的组分为多晶硅,沟槽填充材料为sio2,如图1和2所示。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122359.html

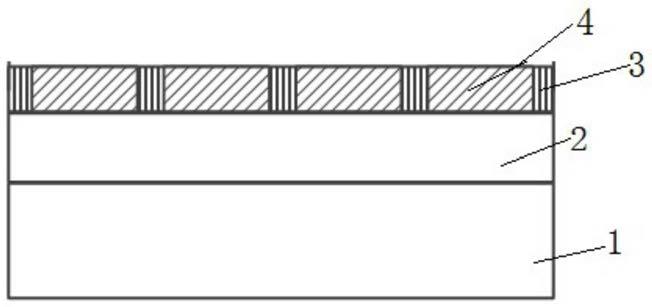

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表