一种MEMS加速度计低应力集成封装结构及方法与流程

- 国知局

- 2024-07-27 12:37:35

一种mems加速度计低应力集成封装结构及方法技术领域1.本发明涉及一种mems加速度计低应力集成封装结构及方法,属于芯片封装技术领域。背景技术:2.加速度计是测量载体加速度的器件,随着微机电系统(mems)技术的飞速发展,利用硅半导体等材料优良的机械特性和成熟的半导体微细加工工艺,可以将惯性仪表的机械结构和相应的电子线路集成在一个小的壳体内,从而使大批量生产微型、低价并具有中等精度的惯性仪表成为可能。相比于传统加工方法制造的加速度计,mems加速度计以集成电路工艺和微机械加工工艺为基础进行制作,具有体积小,重量轻、成本低、功耗低、可靠性好、易集成、过载能力强和可批量生产等优点,成为微型惯性测量组合的核心元件,在军民两用方面有着广泛的应用前景。3.对于高精度mems加速度计而言,性能指标的稳定性是判断器件优劣的重要指标。影响mems加速度计长期稳定性的因素包括环境因素(温度、振动、冲击、湿度等)及内在因素(材料老化、残余应力释放等),其中,器件封装后残余应力的变化可导致器件的零位和标度因数产生变化,是制约加速度计精度提升甚至导致加速度计失效的一个重要因素。因此,如何实现加速度计的低应力封装和设计合理可行的应力隔离集成封装方案对保证其性能的长期稳定具有关键作用。此外,mems加速度计芯片与asic芯片的集成化封装对于缩小器件体积,提高加速度计与后续惯性测量系统的集成度具有重要的应用价值。技术实现要素:4.本发明解决的技术问题是:克服现有技术不足,提供一种mems加速度计低应力集成封装结构及方法,在实现mems加速度计与asic芯片全集成封装的同时,可有效降低mems加速度计的封装应力。5.本发明解决技术的方案是:一种mems加速度计低应力集成封装结构,该封装结构包括应力隔离框架、封装管壳和封装盖板;6.mems加速度计包括mems加速度计芯片和用于加速度计芯片信号的调理与采集的asic芯片,被封装mems加速度计芯片固定在封装管壳基底上;应力隔离框架为倒u型盖板,倒u型盖板与封装管壳底部相粘结,跨在被封装mems加速度计芯片上,所述被封装asic芯片粘结在应力隔离框架上表面,实现与mems加速度计芯片的隔离式堆叠布置;被封装mems加速度计芯片的电极焊盘与对应的被封装asic芯片电极焊盘互连,所述被封装asic芯片的电极焊盘与对应的封装管壳上的焊盘进行金丝键合,实现mems器件的电气连接。7.所述被封装mems加速度计芯片包括被封装mems加速度计敏感结构、封帽层和衬底层;8.所述被封装mems加速度计芯片位于封帽层和衬底层之间,通过锚区与封帽层和衬底层键合,所述锚区键合面形貌呈岛式分布。9.所述被封装mems加速度计芯片通过第一粘结剂固定在封装管壳基底上;所述第一粘结剂粘结位置位于被封装mems加速度计芯片内部锚区在封装管壳基底的投影位置。10.所述第一粘结剂通过点胶的方式使被封装mems加速度计芯片呈圆柱状粘结在封装管壳基底上。11.所述应力隔离框架通过第二粘结剂与封装管壳底部相粘结。12.所述应力隔离框架材料为硅。13.所述被封装asic芯片通过第三粘结剂粘结在应力隔离框架平板上表面,第三粘结剂选用asic专用粘结胶,且采用平铺的方式实现被封装asic芯片与应力隔离框架上表面的粘结。14.本发明另一个技术方案是:一种mems加速度计低应力集成封装方法,该方法包括如下步骤:15.s1、对封装管壳、应力隔离框架、被封装mems加速度计芯片、被封装asic芯片进行清洗;16.s2、通过点胶的方式将被封装mems加速度计芯片固定在封装管壳基底上;所述第一粘结剂粘结位置位于mems加速度计芯片内部锚区在封装管壳(8)基底的投影位置;17.s3、将应力隔离框架粘结在封装管壳上;18.s4、将被封装asic芯片在应力隔离框架上表面的粘结;19.s5、将被封装mems加速度计芯片的电极焊盘与对应的被封装asic芯片电极焊盘互连;20.s6、将被封装asic芯片的电极焊盘与对应的封装管壳上的焊盘进行金丝键合,实现mems器件的电气连接;21.s7、采用共晶熔合的方式实现封装管壳和封装盖板的集成封装。22.步骤s3中,所述应力隔离框架为倒u型盖板,倒u型盖板与封装管壳底部相粘结,跨在被封装mems加速度计芯片上。23.所述步骤s4中,被封装asic芯片粘结在应力隔离框架上表面,实现与被封装mems加速度计芯片的隔离式堆叠布置。24.所述mems加速度计芯片包括mems加速度计敏感结构、封帽层和衬底层;25.所述被封装mems加速度计芯片位于封帽层和衬底层之间,通过锚区与封帽层和衬底层键合,所述锚区键合面形貌呈岛式分布。26.所述被封装mems加速度计芯片通过第一粘结剂固定在封装管壳基底上;所述第一粘结剂粘结位置位于mems加速度计芯片内部锚区在封装管壳基底的投影位置。27.所述第一粘结剂通过点胶的方式使被封装mems加速度计芯片呈圆柱状粘结在封装管壳基底上。28.所述应力隔离框架通过第二粘结剂与封装管壳底部相粘结。29.所述应力隔离框架材料为硅。30.所述被封装asic芯片通过第三粘结剂粘结在应力隔离框架平板上表面,第三粘结剂选用asic专用粘结胶,且采用平铺的方式实现asic芯片与应力隔离框架上表面的粘结。31.本发明与现有技术相比的有益效果是:32.(1)、本发明通过采用mems加速度计芯片和asic芯片隔离堆叠结构设计,相较于传统的mems加速度计芯片和asic芯片堆叠结构设计,可实现mems加速度计芯片和asic芯片之间的应力隔离,使mems加速度计芯片的性能保持稳定;33.(2)、本发明通过敏感结构的分布式岛状锚区设计,岛与岛之间可实现横向应力自抵消,具有应力释放的作用,可有效降低结构圆片级封装过程中的残余应力,减小残余应力对加速度计性能的影响;34.(3)、本发明通过对应mems加速度计芯片的锚区位置进行粘结固定在封装管壳基底的方法,可实现粘结应力和键合应力的纵向自抵消,可降低mems加速度计芯片由于环境力学参数和温度参数改变而导致的应力;35.(4)、本发明通过采用mems加速度计芯片和asic芯片隔离堆叠结构设计,相较于传统的mems加速度计芯片和asic芯片平铺结构设计,可有效减小表头整体体积,并利于后续小型惯组的集成化;36.(5)、本发明所用mems加速度计芯片与封装管壳基底的粘结剂采用软胶,对应力具有吸收作用,并可降低固化过程中器件受到的残余应力。37.(6)、本发明成本低廉,工艺简单,稳定可靠,具有重要的应用价值。附图说明38.图1为本发明实施例的一种mems加速度计低应力集成封装方法结构示意图;39.图2为本发明实施例的一种mems加速度计低应力集成封装方法mems加速度计芯片锚区结构示意图;40.图3为本发明实施例的一种mems加速度计低应力集成封装方法封装管壳示意图;41.图4为本发明实施例的一种mems加速度计低应力集成封装方法mems加速度计芯片粘结示意图;42.图5为本发明实施例的一种mems加速度计低应力集成封装方法应力隔离框架粘结示意图;43.图6为本发明实施例的一种mems加速度计低应力集成封装方法asic芯片粘结及电极引线示意图;44.图7为本发明实施例的一种mems加速度计低应力集成封装方法封装后示意图。具体实施方式45.下面结合附图和实施例对本发明作进一步的详细说明。本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。46.实施例1:47.如图1为本发明的一种mems加速度计结构示意图,mems加速度计包括mems加速度计芯片1和用于mems加速度计芯片的采集的asic芯片6,整体封装结构包括应力隔离框架7、封装管壳8和封装盖板9。封装管壳、封装盖板、应力隔离框架7材料为陶瓷但不仅限于陶瓷。在实施例中,优选陶瓷材料,其封装的电、热性能优良,可靠性高。48.被封装mems加速度计芯片1,固定在封装管壳8基底上;应力隔离框架7为倒u型盖板,倒u型盖板与封装管壳8底部相粘结,跨在被封装mems加速度计芯片1上,所述被封装asic芯片6粘结在应力隔离框架7上表面,实现与mems加速度计芯片1的隔离式堆叠布置;mems加速度计芯片1的电极焊盘与对应的被封装asic芯片6电极焊盘互连,所述被封装asic芯片6的电极焊盘与对应的封装管壳8上的焊盘进行金丝键合,实现mems器件的电气连接。本发明通过被封装mems加速度计芯片和被封装asic芯片的隔离式堆叠结构设计,在降低器件体积并实现被封装mems加速度计芯片与被封装asic芯片全集成封装的同时,实现被封装mems加速度计芯片与被封装asic芯片之间的应力隔离。49.所述应力隔离框架7包括平板、第一立板、第二立板,第一立板和第二立板完全相同,并且相对平行放置,第一立板、第二立板的一侧与平板下表面固定连接,与平板构成一个倒u型盖板,第一立板、第二立板的另一侧与封装管壳8底部相粘结,使得倒u型盖板跨在被封装mems加速度计芯片1上。所述第一立板、第二立板的另一侧通过第二粘结剂10与封装管壳8底部相粘结。所述应力隔离框架7材料为硅;所述应力隔离框架7在被封装mems加速度计芯片电极区域的端面呈u型分布,以实现被封装mems加速度计芯片电极与被封装asic芯片的电学信号互连;所述第二粘结剂10为硬胶,如导电银胶jm7000。50.所述被封装mems加速度计芯片1包括mems加速度计敏感结构2、封帽层3和衬底层4。51.所述被封装mems加速度计敏感结构2位于封帽层3和衬底层4之间,通过锚区5与封帽层3和衬底层4键合,实现圆片级真空封装。所述锚区5键合面形貌呈岛式分布。图2为本发明的一种mems加速度计低应力集成封装方法mems加速度计芯片2的锚区5结构示意图。在实施例中,锚区5位置的封帽层3与被封装mems加速度计芯片2通过硅‑二氧化硅直接键合在一起,被封装mems加速度计芯片2与衬底层4之间通过金‑硅共晶键合使两层结合在一起;衬底层4上布有电极图形,可实现被封装mems加速度计芯片2与外部电极焊盘的互联。本发明锚区通过岛式分布形貌设计,实现横向应力自抵消,降低传递到被封装mems加速度计芯片上的应力。52.所述加速度计敏感结构2、封帽层3和衬底层4均为硅材料,从而其热失配应力最小。53.所述mems加速度计芯片1通过第一粘结剂12固定在封装管壳8基底上;所述第一粘结剂12粘结位置位于被封装mems加速度计芯片内部锚区5在封装管壳8基底的投影位置。所述被封装mems加速度计芯片通过粘结剂在对应于锚区的位置固定在封装管壳底部,实现锚区纵向应力自抵消,提高被封装mems结构的环境稳定性。54.所述第一粘结剂12材料为软胶,如rtv100。55.所述第一粘结剂12通过点胶的方式使被封装mems加速度计芯片1呈圆柱状粘结在封装管壳基底上。56.所述asic芯片6通过第三粘结剂11粘结在应力隔离框架7平板上表面,第三粘结剂11选用asic专用粘结胶,且采用平铺的方式实现asic芯片6与应力隔离框架7上表面的粘结。所述第三粘结剂通过点胶的方式使其呈圆柱状附着在应力隔离框架7上表面;所述粘结剂的位置对应于被封装asic芯片6的四角。57.进一步地,所述被封装mems加速度计芯片1的电极与对应被封装asic芯片6电极互连;所述asic芯片6的电极与对应的封装管壳8上的焊盘进行金丝键合,实现电气连接;最后进行盖板熔封以实现对mems结构的封装。58.实施例2:59.上述mems加速度计的集成封装方法,该方法包括如下步骤:60.s1、对封装管壳8、应力隔离框架7、mems加速度计芯片1、asic芯片6进行清洗;61.所述mems加速度计芯片1包括mems加速度计敏感结构2、封帽层3和衬底层4;62.所述被封装mems加速度计芯片2位于封帽层3和衬底层4之间,通过锚区5与封帽层3和衬底层4键合,所述锚区5键合面形貌呈岛式分布。63.s2、采用第一粘结剂12通过点胶的方式将mems加速度计芯片1固定在封装管壳8基底上;所述第一粘结剂12粘结位置位于mems加速度计芯片内部锚区5在封装管壳8基底的投影位置;具体方法为:64.s2.1、备片:挤粘结剂于胶管中,粘结剂应均匀无凝结现象,离心后将胶管嵌入点胶机上,将装有mems加速度计芯片1的片盒装卡在贴片机上,并通过位置调节确认mems加速度计芯片1在封装管壳的位置正确无误;65.s2.2、点胶:根据器件类型选取工艺参数,点适量胶在对应于mems加速度计芯片1锚区5的粘接面上;如图3所示。66.s2.3、贴片:调节贴片机、吸取mems加速度计芯片1,用粘接面轻轻挤压粘结剂,并实现粘结剂与mems加速度计芯片1和封装管壳粘接面的良好接触;如图4所示。67.s2.4、固化:根据所选取的粘结剂类型,完成粘结剂的完全固化;68.s2.5、镜检,利用体视显微镜观察粘接层是否处于同一水平面,并均匀覆盖粘接面;69.s3、采用第二粘结剂10将应力隔离框架7粘结在封装管壳8上;如图5所示。这个步骤与步骤2.1~步骤2.5类似。70.所述应力隔离框架7为倒u型盖板,倒u型盖板与封装管壳8底部相粘结,跨在被封装mems加速度计芯片1上。所述应力隔离框架7通过第二粘结剂10与封装管壳8底部相粘结。71.s4、采用第三粘结剂11将asic芯片6在应力隔离框架7上表面的粘结;这个步骤与步骤2.1~步骤2.5类似。72.被封装asic芯片6粘结在应力隔离框架7上表面,实现与被封装mems加速度计芯片1的隔离式堆叠布置。具体地,所述被封装asic芯片6通过第三粘结剂11粘结在应力隔离框架7平板上表面,第三粘结剂11选用asic专用粘结胶,且采用平铺的方式实现asic芯片6与应力隔离框架7上表面的粘结。73.s5、将mems加速度计芯片1的电极焊盘与对应的asic芯片6电极焊盘互连;74.s6、将asic芯片6的电极焊盘与对应的封装管壳8上的焊盘进行金丝键合,实现mems器件的电气连接;75.参见图6,衬底层4上布有电极焊盘,并通过金丝打线工艺,实现mems加速度计芯片2与对应的asic芯片6电极焊盘的电极互连,同时,asic芯片6的电极焊盘与对应的封装管壳8上的焊盘进行金丝键合,实现mems器件的电气连接。76.s7、采用共晶熔合的方式实现封装管壳8和封装盖板9的集成封装。77.参见图7,实现封装管壳8和封装盖板9的集成封装,在实施例中,优选地,通过共晶熔合的方式来进行封装,真空共晶焊接方法能够实现高真空度,加上吸气剂的合理应用,能维持长期的真空稳定性。78.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122778.html

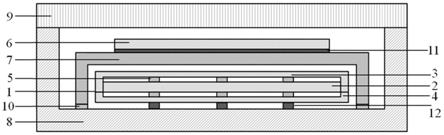

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。