一种铷原子钟漂移控制装置及方法

- 国知局

- 2024-07-30 09:33:17

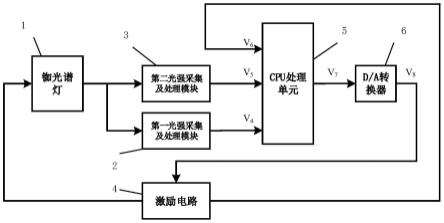

1.本发明涉及铷原子钟技术领域,具体涉及一种铷原子钟漂移控制装置,还涉及一种铷原子钟漂移控制方法。背景技术:2.铷原子钟作为一种能够提供高稳定度时间频率信号的设备,已被广泛应用于各种守时、授时、全球导航定位、网络同步、通讯等领域。铷光谱灯是铷频标核心部件之一。它的可靠性、稳定性和寿命是制约铷频标整机性能的“瓶颈”。因此如何改善铷原子钟漂移指标,提高守时性能是时统设备追求的关键点。3.铷原子钟漂移主要受物理系统(光谱灯和腔泡系统)影响,主要包括光谱灯自身光强幅值变化、腔泡系统引起的光强变化以及光频移影响。其中控制激励功率则是改变光频移的重要方法。目前国内外控制铷原子钟漂移主要通过采集并利用共振信号的直流信号强度变化,然后通过修改射频dds的频率控制字,反向抵消漂移的方式来控制漂移大小。但是由于漂移是一个多参量的集合效应,目前的方案考虑因素单一,因而漂移控制精度较低,还需进一步完善。技术实现要素:4.本发明的目的是在于针对现有技术存在的上述问题,提供一种铷原子钟漂移控制装置,还提供一种铷原子钟漂移控制方法。5.为了实现上述的目的,本发明采用以下技术措施:6.一种铷原子钟漂移控制装置,包括铷光谱灯,还包括第一光强采集及处理模块、第二光强采集及处理模块、激励电路、cpu处理单元、以及d/a转换器,7.第一光强采集及处理模块包括依次连接的第一光电池、第一i/v转换电路和第一a/d采样器,8.第二光强采集及处理模块包括依次连接的第二光电池、第二i/v转换电路和第二a/d采样器,第二光电池设置在微波腔中,微波腔中位于第二光电池的前端还设置有滤光泡和吸收泡,9.第一a/d采样器和第二a/d采样器分别与cpu处理单元连接,cpu处理单元通过d/a转换器与激励电路的控制端连接,激励电路的反馈端与cpu处理单元连接,激励电路的激励电感缠绕在铷光谱灯上。10.如上所述激励电路包括第三电阻、第四电阻、第五电阻、第六电阻、第一电容、第二电容、第三电容、二极管、第一电感、第二电感、mos管、第三a/d转换器、以及功率晶体管,11.电源vcc经第三电阻与mos管的漏极相连,mos管的源极连接第一电感一端,第一电感另一端再经过第三电容连接到电气地,第一电感作为激励电路的激励电感,mos管的源极还与功率晶体管的基极连接;电源vcc与第四电阻一端连接,第四电阻另一端与mos管的源极连接,mos管的栅极作为激励电路的控制端与d/a转换器连接;电源vcc与功率晶体管集电极相连,功率晶体管基极依次通过第五电阻和二极管接电气地,功率晶体管发射极与第二电感一端连接,第二电感另一端分别与第六电阻一端和第三i/v转换电路一端连接,第二电阻另一端接电气地,第三i/v转换电路另一端通过第三a/d采样器与cpu处理单元连接;第一电容并联在功率管基极和发射极之间;第二电容并联在功率管集电极和发射极之间;第六电阻两端的电压差输入到第三a/d转换器,第三a/d转换器的输出接口作为激励电路的反馈端与cpu处理单元连接。12.如上所述cpu处理单元输出到d/a转换器的电压v7基于以下公式计算:[0013][0014]其中,v4为第一a/d转换器生成的数字电压,v5为第二a/d转换器生成的数字电压、v6为第三a/d转换器生成的数字电压,α、β、γ均为设定值,a1、a2、b1、b2、c1、c2、c3、d1、以及d2均为调试常数。[0015]一种铷原子钟漂移控制方法,包括以下步骤:[0016]步骤1,利用第一光电池采集铷光谱灯直接照射的光强信号,铷光谱灯直接照射的光强信号依次经第一i/v转换电路和第一a/d转换器后生成数字电压v4;[0017]步骤2,利用第二光电池采集铷光谱灯经过滤光泡和吸收泡后的光强信号,铷光谱灯经过滤光泡和吸收泡后的光强信号依次经第二i/v转换电路以及第二a/d转换器后生成数字电压v5;[0018]步骤3,第六电阻两端的电压差经第三a/d转换器转换为数字电压v6;[0019]步骤4,cpu处理单元基于以下公式输出到d/a转换器的电压v7:[0020][0021]其中,v4为第一a/d转换器生成的数字电压,v5为第二a/d转换器生成的数字电压、v6为第三a/d转换器生成的数字电压,α、β、γ均为设定值,a1、a2、b1、b2、c1、c2、c3、d1、以及d2均为调试常数,[0022]步骤5,cpu处理单元输出到d/a转换器的电压v7经d/a转换器后生成的模拟电压v8接入mos管栅极,控制流过功率晶体管电流的大小,对铷原子钟漂移进行调节控制。[0023]本发明相对于现有技术,具有以下有益效果:[0024]本发明针对影响铷原子钟漂移系数的多个因素,即光谱灯自身光强幅值变化、腔泡系统(滤光泡、吸收泡等)引起的光强变化以及光频移进行综合处理,降低了铷原子钟的漂移率,极大提升了铷原子钟守时性能指标。附图说明[0025]图1为一种铷原子钟漂移控制装置的模块图。[0026]其中:1—铷光谱灯;2—第一光强采集及处理模块;3—第二光强采集及处理模块;4—激励电路;5—cpu处理单元;6—d/a转换器。[0027]图2为激励电路的电路结构图。具体实施方式[0028]为了便于本领域普通技术人员理解和应用本发明,下面结合实施例对本发明作进一步的详细描述,应当理解,此处所描述的实施实例仅用于说明和解释本发明,并不用于限定本发明。[0029]如图1所示,本发明提供了一种铷原子钟漂移控制装置,包括铷光谱灯1、第一光强采集及处理模块2、第二光强采集及处理模块3、激励电路4、cpu处理单元5、以及d/a转换器6。[0030]第一光强采集及处理模块2包括依次连接的第一光电池、第一i/v转换电路和第一a/d采样器,[0031]第二光强采集及处理模块2包括依次连接的第二光电池、第二i/v转换电路和第二a/d采样器。第二光电池设置在微波腔中,微波腔中位于第二光电池的前端还设置有滤光泡和吸收泡。[0032]铷光谱灯1发出的光经第一光强采集及处理模块2和采集和处理,铷光谱灯1发出的光还依次经微波腔中的滤光泡和吸收泡之后,由第二光强采集与处理模块3采集和处理。[0033]第一a/d采样器和第二a/d采样器分别与cpu处理单元5连接,cpu处理单元5通过d/a转换器6与激励电路4的控制端连接,激励电路4的反馈端与cpu处理单元5连接,激励电路4的激励电感缠绕在铷光谱灯1上。[0034]cpu处理单元5根据第一光强采集及处理模块2和第二光强采集及处理模块3的采样差值,以及激励电路4的反馈端输出的电压,通过d/a转换器6输出调控电压到激励电路4,激励电路4根据控制电压对激励电感的电流进行控制。[0035]第一电感l1为激励电感,缠绕在铷光谱灯上,用于激发铷光谱灯发光。第一光电池1将铷光谱灯光强转换为电流i1,经第一i/v转换电路后,生成模拟电压v1,再经第一a/d转换器后生成数字电压v4送入cpu处理单元;第二光电池2采集依次经过滤光泡和吸收泡后的光谱灯光强,生成电流i2,经过第二i/v转换电路后,生成模拟电压v2,再经第二a/d转换器后生成数字电压v5送入cpu处理单元。[0036]如图2所示,激励电路4包括第三电阻r3,第四电阻r4,第五电阻r5,第六电阻r6,第一电容c1,第二电容c2,第三电容c3,二极管d1,第一电感l1、第二电感l2、mos管n1、第三a/d转换器、以及功率晶体管q1。[0037]所述的激励电路中电源vcc经第三电阻r3与mos管n1的漏极相连,mos管n1的源极连接第一电感l1一端,第一电感l1另一端再经过第三电容c3连接到电气地,第一电感l1作为激励电路4的激励电感,mos管n1的源极还与功率晶体管q1的基极连接;电源vcc与第四电阻r4一端连接,第四电阻r4另一端与mos管n1的源极连接,mos管n1的栅极作为激励电路4的控制端与d/a转换器6连接;电源vcc与功率晶体管q1集电极相连,功率晶体管q1基极依次通过第五电阻r5和二极管d1接电气地,功率晶体管q1发射极与第二电感l2一端连接,第二电感l2另一端分别与第六电阻r6一端和第三i/v转换电路一端连接,第二电阻r6另一端接电气地,第三i/v转换电路另一端通过第三a/d采样器与cpu处理单元连接;第一电容c1并联在功率管q1基极和发射极之间;第二电容c2并联在功率管q1集电极和发射极之间;第六电阻r6为负反馈电阻,第六电阻r6电压变化表征激励功率变化,如图2所示,第六电阻r6两端的电压差输入到第三a/d转换器,第三a/d转换器的输出接口作为激励电路4的反馈端与cpu处理单元连接。[0038]接通电源,第一电感l1激励铷光谱灯工作。mos管n1的栅极接收来自d/a转换器的调控电压v8。在激励电路4正常运行工作条件下,当调控电压v8越大时,mos管n1的源极与漏极间流过的电流越大,使得第三电阻r3两端电压越大,功率晶体管q1的基极电压越小,进而功率晶体管q1的发射极与集电极之间的导通电流越小,从而使得激励电路4输出的激励电压v6越小。在激励电路4正常运行工作条件下,当调控电压v8越小时,mos管n1的源极与漏极间流过的电流越小,使得第三电阻r3两端电压越小,功率晶体管q1的基极电压越大,进而功率晶体管q1的发射极与集电极之间的导通电流越大,从而使得激励电路4输出的激励电压v6越大。[0039]cpu处理单元输出到d/a转换器6的电压v7基于以下公式计算:[0040][0041]其中,v7为cpu处理单元输出到d/a转换器的数字电压,v4为第一a/d转换器生成的数字电压,v5为第二a/d转换器生成的数字电压、v6为第三a/d转换器生成的数字电压,α、β、γ均为设定值,a1、a2、b1、b2、c1、c2、c3、d1、d2均为调试常数。对三路数字电压处理。处理完成后将生成数字电压v7,再经d/a转换器后接入mos管的栅极,从而控制流过功率晶体管q1电流的大小,进而改变激励功率,最终实现对铷原子钟漂移的控制调节,达到稳定修正漂移的目的。[0042]一种铷原子钟漂移控制方法,包括以下步骤:[0043]步骤1,利用第一光电池1探测铷光谱灯直接照射的光强信号,铷光谱灯直接照射的光强信号依次经第一i/v转换电路和第一a/d转换器后生成数字电压v4;[0044]步骤2,利用第二光电池2采集铷光谱灯经过滤光泡和吸收泡后的光强信号,铷光谱灯经过滤光泡和吸收泡后的光强信号依次经第二i/v转换电路以及第二a/d转换器后生成数字电压v5;[0045]步骤3,利用第六电阻r6电压变化表征激励功率变化,第六电阻r6两端的电压差经第三a/d转换器转换为数字电压v6;[0046]步骤4,将步骤1、步骤2和步骤3中采集的电压v4、v5、v6送入cpu处理单元,cpu处理单元输出到d/a转换器(6)的电压v7基于以下公式计算:[0047][0048]其中,v4为第一a/d转换器生成的数字电压,v5为第二a/d转换器生成的数字电压、v6为第三a/d转换器生成的数字电压,α、β、γ均为设定值,a1、a2、b1、b2、c1、c2、c3、d1、以及d2均为调试常数。[0049]步骤5,将步骤4中处理后的cpu处理单元输出到d/a转换器6的电压v7经d/a转换器后生成的模拟电压v8接入mos管1栅极,从而控制流过功率晶体管q1电流的大小,改变激励功率,最终实现对铷原子钟漂移的控制调节,达到稳定修正漂移的目的。[0050]需要指出的是,本发明中所描述的具体实施例仅是对本发明精神作举例说明。本发明所属技术领域的技术人员可以对所描述的具体实施例作各种各样的修改或补充或采用类似的方式替代,但并不会偏离本发明的精神或超越所附权利要求书所定义的范围。

本文地址:https://www.jishuxx.com/zhuanli/20240730/149925.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。