一种可以自动计算星期值的实时时钟单元电路的制作方法

- 国知局

- 2024-07-30 09:34:09

1.本发明属于微电子/数字电路技术领域,尤其是涉及一种可以自动计算星期值的实时时钟单元电路。背景技术:2.实时时钟(real-time clock, rtc)在消费类电子产品中应用非常广泛。各种实时时钟芯片或片上内置了实时时钟功能模块的微控制器mcu或片上系统soc芯片种类繁多,层出不穷。3.目前市售的实时时钟芯片或者片上内置了实时时钟功能模块的mcu或soc芯片,需要事先对相应的年、月、日、星期、时、分、秒等寄存器进行正确的初始化设置,之后实时时钟才能正常运行。年、月、日、时、分、秒寄存器的设置不需要复杂计算,比较容易实现。但是星期和具体的年、月、日是有关联关系的,是一一对应的。在设置星期值时,软件开发人员可能需要查询纸质日历或者具有存储日历功能的手机、电脑,或人工推算。人工推算时必须掌握一定的方法,而且计算麻烦,容易出错。4.有些型号的实时时钟芯片或者片上内置了实时时钟功能模块的mcu或soc芯片,并不提供星期寄存器。而一般提供日历和时间功能的电子产品均会提供星期信息。为了获取星期信息,软件开发人员需要根据芯片内部提供的年、月、日信息编写软件函数来计算星期值。5.设置正确的星期寄存器初值以及开发星期计算软件,额外增加了软件开发人员的工作量,降低了开发效率。值得一提的是,星期计算程序函数也会额外占用mcu/soc的程序存储空间,当程序空间容量较小时,软件开发人员还需要考虑如何尽可能地压缩程序代码以节省程序所占用的存储空间。6.另外,市售的实时时钟芯片或者片上内置了实时时钟功能模块的mcu或soc芯片,其星期寄存器的值并不和年月日有公式计算上的关联关系,仅仅是一个计数器而已。如果初值设定错误,则实时时钟运行之后将一直存在星期和日历不一致的错误现象,并且也没有错误检查标志。即使初值设定是正确的,实时时钟运行之后也可能因受到干扰等原因而出现错乱故障,导致星期和年月日不相对应的现象发生。7.如果实时时钟能够提供星期值,这将能够避免软件开发人员设置星期初值或编写星期计算函数的麻烦,提高开发效率;同时也能避免出现星期值和年月日值不匹配的问题。技术实现要素:8.本发明旨在解决上述技术问题,提供一种可以自动计算星期值的实时时钟单元电路。9.为了达到上述目的,本发明采用如下技术方案:一种可以自动计算星期值的实时时钟单元电路,包括秒时钟产生器、秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器、星期计算器;所述秒时钟产生器与所述秒计数器连接,所述秒时钟产生器提供1赫兹时钟信号clk_1hz,所述秒计数器根据所述秒时钟产生器提供的1赫兹时钟信号计秒,所述秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器依次连接,分别为下一个计数器提供进位信号,所述年计数器、月计数器、日计数器分别向所述星期计算器输入年值year、月值month、日值day;所述月计数器向所述日计数器输入月值month,所述年计数器包括闰年判断模块,闰年判断模块输入年值year,闰年判断模块根据输入的年值year判断是否为闰年,并输出闰年指示信号leap,如果为闰年,leap输出1,如果不是,leap输出0,所述年计数器向所述日计数器输入闰年指示信号leap;所述星期计算器包括码值转换模块、除4运算模块、月份修正译码模块、求和计算模块、对7求余模块,所述星期计算器实现2000~2099百年之内的星期值的计算,所述星期计算器对输入的年值year、月值month、日值day,并结合输入的闰年指示信号leap进行运算,所述星期计算器输出该天对应的星期值week;月份修正译码模块输入月值month和闰年判断模块输出的闰年指示信号leap,月份修正译码模块根据月份以及闰年标志,分别对不同的月份输出一个对应的修正译码值;所述码值转换模块用于将输入所述星期计算器的年值year、日值day的bcd码值转换为自然二进制码值;所述除4运算模块对经过所述码值转换模块转换的年值year进行除4运算,结果是一个整数,结果只取商值,丢弃余数;所述求和计算模块对经过所述码值转换模块转换的年值year、经过所述码值转换模块转换的日值day、所述月份修正译码模块输出的修正译码值、所述除4运算4模块输出的年份除4取整结果进行求和;所述对7求余模块对所述求和计算模块输出的值进行除以7求余处理,余数即为输出的该天对应的星期值week。10.作为一种优选的技术方案,所述可以自动计算星期值的实时时钟单元电路还包括闹钟发生器,所述闹钟发生器输入日计数值、星期计数值、小时计数值、分计数值、秒计数值,并根据闹钟输入闹钟日值、闹钟星期值、闹钟小时值、闹钟分钟值、闹钟秒值,所述闹钟发生器包括选择器一、选择器二、比较器一、比较器二、比较器三、比较器四、或门一、或门二、或门三、与非门一、或门四、与门一,选择器一输入闹钟日值和闹钟星期值,选择器二输入日计数值和星期计数值,向选择器一、选择器二输入0或1的wdsel控制位选择比较日或星期,比较器四输入选择器一、选择器二输出的闹钟日值、日计数值或者闹钟星期值、星期计数值,比较器三输入闹钟小时值、小时计数值,比较器二输入闹钟分钟值、分计数值,比较器一输入闹钟秒值、秒计数值,若闹钟报警时间和当前时间一致,比较器输出报警标志flag,所述闹钟发生器包括日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器,日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器分别提供一位屏蔽控制位msk4、msk3、msk2、msk1,或门一输入比较器一输出的报警标志flag1和屏蔽控制位msk1信号,或门二输入比较器二输出的报警标志flag2和屏蔽控制位msk2信号,或门三输入比较器三输出的报警标志flag3和屏蔽控制位msk3信号,或门四输入比较器四输出的报警标志flag4和屏蔽控制位msk4信号,与非门一输入屏蔽控制位msk1、msk2、msk3、msk4信号,屏蔽控制位msk4、msk3、msk2、msk1分别是日/星期、时、分、秒的报警屏蔽控制位,为1时对应字段被屏蔽,所述与门一输入或门一、或门二、或门三、或门四、与非门一的输出以及使能位rtcen信号、控制位taen信号,所述与门一输出闹钟报警标志taif信号。11.作为一种优选的技术方案,所述可以自动计算星期值的实时时钟单元电路还包括读写访问控制电路,所述读写访问控制电路包括寄存器读写访问总线、控制寄存器rtc_cr和状态寄存器rtc_sr,所述秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器、星期计算器分别包括秒寄存器、分寄存器、小时寄存器、日寄存器、月寄存器、年寄存器、星期寄存器,所述寄存器访问总线分别与秒寄存器、分寄存器、小时寄存器、日寄存器、月寄存器、年寄存器、星期寄存器、日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器、控制寄存器rtc_cr和状态寄存器rtc_sr连接,所述控制寄存器rtc_cr包括控制位taen和使能位rtcen,所述控制位taen和使能位rtcen与所述闹钟发生器连接,所述状态寄存器rtc_sr包括报警标志位taif,所述报警标志位taif与所述闹钟发生器连接。12.作为一种优选的技术方案,所述控制寄存器rtc_cr包括寄存器位a12_24,所述寄存器位a12_24与所述时报警寄存器连接,所述控制寄存器rtc_cr包括寄存器位n12_24,所述寄存器位n12_24与小时计数器连接。13.作为一种优选的技术方案,所述可以自动计算星期值的实时时钟单元电路还包括实时时钟中断电路,所述实时时钟中断电路包括选择器三、与门二、与门三、或门五、秒/半秒中断使能寄存器rtcie、秒/半秒中断标志寄存器rtcif、闹钟报警中断使能寄存器taie、闹钟报警中断标志寄存器taif,所述控制寄存器rtc_cr包括使能位rtcen以及用于产生rtcif标志位的选择控制信号的rtcints位,所述秒时钟产生器还提供半秒信号clk_2hz,所述状态寄存器rtc_sr包括rtcif标志位,选择器三输入clk_1hz和clk_2hz,选择控制信号rtcints连接选择器三的选择控制输入端,所述闹钟发生器输出的闹钟报警标志taif信号寄存至闹钟报警中断标志寄存器taif,所述状态寄存器rtc_sr的rtcif标志位连接秒/半秒中断标志寄存器rtcif,所述选择器三的输出端连接所述秒/半秒中断标志寄存器rtcif的输入端,所述秒/半秒中断标志寄存器rtcif的输出端、所述秒/半秒中断使能寄存器rtcie的输出端连接所述与门二的输入端,所述闹钟报警中断标志寄存器taif的输出端、所述闹钟报警中断使能寄存器taie的输出端连接所述与门三的输入端,所述与门二的输出端、所述与门三的输出端连接所述或门五的输入端,所述或门五的输出端输出rtc中断信号rtcint。14.作为一种优选的技术方案,所述秒时钟产生器包括片内高频rc时钟ihrc、片内低频rc时钟ilrc、外部晶振时钟xtosc、预分频器、选择器四、与门四、同步分频器,所述片内高频rc时钟ihrc连接预分频器后连接选择器四的输入端,所述片内低频rc时钟ilrc、外部晶振时钟xtosc连接选择器四的输入端,所述控制寄存器rtc_cr包括rtccks[1:0]寄存器位,rtccks[1:0]寄存器位连接选择器四、同步分频器的控制输入端,所述选择器四输出的rtc_clk信号、所述控制寄存器rtc_cr的使能位rtcen连接所述与门四的输入端,所述与门四输出的rtc_gclk信号连接所述同步分频器的时钟输入端,所述同步分频器输出clk_1hz、clk_2hz信号。[0015]作为一种优选的技术方案,所述可以自动计算星期值的实时时钟单元电路包括apb总线,所述秒时钟产生器、秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器、星期计算器均与apb总线连接,所述apb总线包括apb同步读取寄存器,所述apb同步读取寄存器,包括锁存控制器以及与所述锁存控制器连接的年锁存器、月锁存器、日锁存器、星期锁存器、小时锁存器、分锁存器、秒锁存器,所述锁存控制器的工作时钟为apb总线上的系统时钟sysclk,所述年锁存器、月锁存器、日锁存器、星期锁存器、小时锁存器、分锁存器、秒锁存器分别连接年计数器、月计数器、日计数器、星期计算器、小时计数器、分计数器、秒计数器。[0016]作为一种优选的技术方案,所述可以自动计算星期值的实时时钟单元电路包括i2c/spi总线或uart通信口,通过i2c/spi/uart通信口访问实时时钟单元电路的所有寄存器。[0017]采用上述技术方案后,本发明具有如下优点:本发明提供了一种实时时钟单元电路,星期值可自动计算;实时时钟工作前,不需要为星期进行初始化设置,免于人工计算星期值;不需要开发星期计算函数软件,从而可以节省一部分程序空间;星期值由纯硬件电路实时进行计算,计算速度比软件计算快;星期计算方法相对精简,硬件电路实现占用逻辑资源相对比较少;星期值跟随年月日值的变化而变化,能够避免星期值和年月日值不匹配的问题的发生;工作时钟源可以选择配置,增加应用上的灵活性、方便性;提供秒中断/半秒中断、闹钟报警中断,当电路应用于mcu/soc芯片,这些中断可被mcu/soc用于低功耗模式相关的管理。附图说明[0018]图1为一种可以自动计算星期值的实时时钟单元电路的逻辑电路图;图2为秒时钟产生器逻辑电路图;图3为星期计算器模块接口示意图;图4为星期计算器模块的逻辑电路图;图5为闰年判断模块的逻辑电路图;图6为码值转换模块的计算原理图;图7为码值转换模块的逻辑电路图;图8为一种可实施的月份修正译码逻辑电路图;图9为一种对7求余模块的结构图;图10为闹钟发生器的逻辑电路图;图11为实时时钟中断电路的逻辑电路图;图12为实时时钟单元电路挂接于apb总线的示意图;图13为apb同步读取寄存器的逻辑电路图;图14为锁存控制器电路图;图15为实时时钟单元电路挂接于i2c/spi总线或uart通信口的示意图;图16为i2c接口控制电路逻辑电路图;图17为spi通信接口控制电路逻辑电路图;图18为uart通信接口控制电路逻辑电路图;图19为星期计算器输入输出时序波形图。具体实施方式[0019]以下结合附图及具体实施例,对本发明作进一步的详细说明。[0020]如图1所示,一种可以自动计算星期值的实时时钟单元电路,包括秒时钟产生器、秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器、星期计算器、闹钟发生器和读写访问控制电路。如果不需要闹钟功能,可以将闹钟发生器逻辑电路删除。[0021]实时时钟单元电路中含有年、月、日、时、分、秒计数器,每个计数器各自对应一个寄存器。相应地,星期计算器对应一个星期寄存器。闹钟发生器对应日/星期、时、分、秒四个报警值寄存器。读写访问接口控制电路中对应安排有控制寄存器rtc_cr和状态寄存器rtc_sr。[0022]所有寄存器安排情况见表1寄存器集合,共计有13个字节。[0023]表1寄存器集合年、月、日、时、分、秒、星期寄存器值以及闹钟时间相关寄存器值,均采用bcd码表示。[0024]所述秒时钟产生器与所述秒计数器连接,所述秒时钟产生器提供1赫兹时钟信号clk_1hz,所述秒计数器根据所述秒时钟产生器提供的1赫兹时钟信号计秒,所述秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器依次连接,分别为下一个计数器提供进位信号,所述年计数器、月计数器、日计数器分别向所述星期计算器输入年值year、月值month、日值day。所述月计数器向所述日计数器输入月值month,所述年计数器包括闰年判断模块,闰年判断模块输入年值year,闰年判断模块根据输入的年值year判断是否为闰年,并输出闰年指示信号leap,如果为闰年,leap输出1,如果不是,leap输出0,所述年计数器向所述日计数器输入闰年指示信号leap。[0025]实时时钟单元电路可以进行年、月、日、星期、时、分、秒的时钟计时功能,可实现2000~2099年的万年历数据,并具有闰年修正功能、闹钟功能、星期自动计算功能。其中闹钟功能可选星期/日期、时、分、秒进行匹配,并分别提供屏蔽功能。[0026]读写访问接口控制电路为外部系统总线(如apb总线)或通信接口(如uart、spi、i2c通信口等)与单元电路内部的寄存器的交互架起了桥梁。外部系统总线或通信接口通过读写访问接口控制电路,可以访问实时时钟单元电路中所有的寄存器。除了星期寄存器是只读寄存器外,其余寄存器均为可读可写寄存器。通过写操作可以设置年、月、日、时、分、秒的初值、设置闹钟时间值、设置控制寄存器等。通过读操作可以获取当前年、月、日、星期、时、分、秒的日历时间信息以及状态寄存器信息等。[0027]所述读写访问控制电路包括寄存器读写访问总线、控制寄存器rtc_cr和状态寄存器rtc_sr。所述秒计数器、分计数器、小时计数器、日计数器、月计数器、年计数器、星期计算器分别包括秒寄存器、分寄存器、小时寄存器、日寄存器、月寄存器、年寄存器、星期寄存器,所述寄存器访问总线分别与秒寄存器、分寄存器、小时寄存器、日寄存器、月寄存器、年寄存器、星期寄存器、日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器、控制寄存器rtc_cr和状态寄存器rtc_sr连接,所述控制寄存器rtc_cr包括控制位taen和使能位rtcen,所述控制位taen和使能位rtcen与所述闹钟发生器连接,所述状态寄存器rtc_sr包括报警标志位taif,所述报警标志位taif与所述闹钟发生器连接。[0028]所述控制寄存器rtc_cr包括寄存器位a12_24,所述寄存器位a12_24与所述时报警寄存器连接,所述控制寄存器rtc_cr包括寄存器位n12_24,所述寄存器位n12_24与小时计数器连接。[0029]秒时钟产生器提供1赫兹时钟信号clk_1hz供秒计数器使用。同时还提供半秒信号clk_2hz。状态寄存器rtc_sr中设置有rtcif标志位,它的触发信号可以选择使用clk_1hz,也可以选择使用clk_2hz。相对应的选择控制信号是控制寄存器rtc_cr中的rtcints位。当被选择的触发信号到来后,可以触发rtcif标志位为1。通过读写访问接口控制电路向状态寄存器相应位写入规定数据可清除该中断标志位。该规定数据,可以事先规定使用数据0,即状态寄存器位是写0清零的;也可以事先规定使用数据1,即状态寄存器位是写1清零的。1赫兹时钟信号和半秒信号是否提供会受控于控制寄存器中的模块使能位rtcen。若模块不被使能,则秒时钟产生器等均不再工作,从而降低电路功耗。[0030]实时时钟的工作时钟源不限定于必须使用外部32768hz晶振时钟,也可以选择使用其它频率发生器,如高频rc振荡器时钟(比如频率为兆赫兹量级)、低频rc振荡器时钟(比如频率为千赫兹量级),以增加电路使用的灵活性。时钟选择取决于控制寄存器中的时钟源选择控制位(rtccks)。[0031]在mcu/soc中,该单元电路工作时钟源有三个可选:片内高频rc时钟ihrc(24mhz)、片内低频rc时钟ilrc(32khz)、外部晶振时钟xtosc(32768hz)。三个时钟源信号,被控制寄存器中的rtccks[1:0]寄存器位进行选择。[0032]如图2所示,所述秒时钟产生器包括片内高频rc时钟ihrc、片内低频rc时钟ilrc、外部晶振时钟xtosc、预分频器、选择器四、与门四、同步分频器,所述片内高频rc时钟ihrc连接预分频器后连接选择器四的输入端,所述片内低频rc时钟ilrc、外部晶振时钟xtosc连接选择器四的输入端,所述控制寄存器rtc_cr包括rtccks[1:0]寄存器位,rtccks[1:0]寄存器位连接选择器四、同步分频器的控制输入端,所述选择器四输出的rtc_clk信号、所述控制寄存器rtc_cr的使能位rtcen连接所述与门四的输入端,所述与门四输出的rtc_gclk信号连接所述同步分频器的时钟输入端,所述同步分频器输出clk_1hz、clk_2hz信号。[0033]对ihrc进行预分频(分频系数为750),将频率降低至32khz,和ilrc、xtosc频率量级相同。经过rtccks[1:0]选择后得到rtc_clk。通过rtcen对rtc_clk进行时钟门控,得到rtc_gclk,并提供给同步分频器。同步分频器根据rtccks[1:0]的值,决定对rtc_gclk进行分频的分频系数。当选择xtosc时,分频系数设定为16384,得到clk_2hz的时钟信号。当选择ihrc或ilrc时,分频系数设定为16000,得到clk_2hz时钟信号。clk_1hz信号是clk_2hz的二分频。[0034]秒计数器在秒时钟clk_1hz的驱动下,每来一个秒时钟脉冲秒计数就自动加1。当秒计数至59,再来一个秒时钟脉冲则秒计数将返回0,并向分计数器产生进位。秒计数是0~59循环的。[0035]分计数器的有效计数范围和秒计数器的相同,均为0~59。当分计数至59并且秒计数器再次向分计数器进位时,则分计数器归零,同时小时计数器加1。[0036]其余计数器对应的寄存器均会以相同的原理进行进位、计数,以此实现该模块的各种功能。[0037]小时计数器有两种制式可选,12小时制,或24小时制。制式选择控制位n12_24可随时动态切换,不影响实际时间值。24小时制下,小时计数值有效范围为00~23。12小时制下,仅将有效值设定为1~12是不够的,还需要增加一个标识位,用来表明是上午还是下午的时间。[0038]每个月份的日子数不尽相同,并且二月份的天数还有闰年和非闰年之分。所以日计数器模块需要闰年指示leap信号以及月份信号的配合。1、3、5、7、8、10、12月份中,每个月均有31天;4、6、9、11月份中,每个月均有30天;2月份,如果是闰年则有29天,不是闰年时只有28天。[0039]当日计数到达月底,并且当小时计数器再向日计数器进位时,则日计数返回1,并且会向月计数进位,月计数器将加1。因为一年只有12个月,所以月计数器是1~12循环计数的。[0040]年份2000~2099均固定属于21世纪,年份只保留后两位,年计数器有效范围00~99,共计一百年。因为年份的头两位固定为20,所以闰年判断的规则可以简化为:如果年份的后两位数值是4的倍数则是闰年,否则不是闰年。leap是闰年指示信号:leap为1时,表明这一年份是闰年;leap为0时,表明这一年份不是闰年。leap信号被用于日计数器模块和星期计算器模块。[0041]如图3所示,星期计算器根据年、月、日以及闰年指示信号leap信号,自动计算对应的星期值。星期计算器的结果有效值为0x0、0x1、0x2、0x3、0x4、0x5、0x6,依次分别表示周日、周一、周二、周三、周四、周五、周六。因为有多种历法存在,所以星期的计算也有多种方法。依据不同的算法可以进行不同的星期计算器电路的设计。使用加、减、乘、除以及求余逻辑就能够完成相应的算法。[0042]为了尽可能降低电路实现的资源代价,本实施例给出一种比较精简的、简便的星期计算公式,如下:week=([y/4]+y+mc+d)%7;其中,week代表星期值,y代表2000~2099的后两位年份数,mc代表月份的修正转码,d代表日,[y/4]代表对年份除以4后取整数值,%7表示对7进行求余数。[0043]月份修正转码mc的产生规则:当年份为闰年时,1~12月的修正转码值分别为5、1、2、5、0、3、5、1、4、6、2、4;当年份为非闰年时,1~12月的修正转码值分别为6、2、2、5、0、3、5、1、4、6、2、4。[0044]因为相对于已有的公知星期算法公式(如基姆拉尔森计算公式、蔡勒(zeller)公式),此公式所需运算次数少,计算量小,相应地,依此设计电路也能有效缩减门电路数量。星期计算器实际实现电路规模约为百余门。[0045]计算星期值需要的信号有年份year信号、闰年指示leap信号、月份month信号、日day信号。年份year信号,范围为00~99。月份month信号,范围为01~12。[0046]在年计数器模块中对年份进行闰年判断,根据年份值给出闰年指示leap信号。如果为闰年,leap输出1;如果不是,leap输出0。[0047]闰年判断规则:因为年份的头两位固定为20,所以闰年判断的规则可以简化为:如果年份的后两位数值是4的倍数则是闰年,否则不是闰年。[0048]数字电路中的数据在进行运算时是以二进制规则进行的。而年、月、日的码值是以bcd码表示的。对bcd码表示的数值按照二进制的规则运算可能导致错误的结果。所以需要对bcd码值进行码值转换:将年份或日的bcd码值转换为自然二进制码值。年份/日bcd码的十位乘以10再加上其bcd码的个位,所得之和在电路中存储为自然二进制数。为了节省实现资源,乘10运算可以替换为对bcd码的十位分别先进行左移1位、左移3位以实现乘2、乘8的功能,然后再将两者相加即可得到乘10的结果。[0049][y/4]对应于年份除以4并对结果进行取整的运算。为了节省实现资源,除法可以使用对被除数进行逻辑右移两位的方式实现。[0050]月份修正译码mc,根据月份以及闰年指示,分别对不同的月份输出一个对应的码值。利用组合逻辑译码输出即可。[0051][y/4]+y+mc+d求和计算,使用加法器即可实现。[0052]对7求余运算,是对求和计算值进行模7处理,结果也就是和值除以7后得到的余数。[0053]如图4所示,本实施例中,星期计算器包括码值转换模块、除4运算模块、月份修正译码模块、求和计算模块、对7求余模块,所述星期计算器实现2000~2099百年之内的星期值的计算,所述星期计算器对输入的年值year、月值month、日值day,并结合输入的闰年指示leap信号进行运算,所述星期计算器输出该天对应的星期值week。月份修正译码模块输入月值month和闰年判断模块输出的闰年指示信号leap,月份修正译码模块根据月份以及闰年标志,分别对不同的月份输出一个对应的修正译码值。所述码值转换模块用于将输入所述星期计算器的年值year、日值day的bcd码值转换为自然二进制码值。所述除4运算模块对经过所述码值转换模块转换的年值year进行除4运算,结果是一个整数,结果只取商值,丢弃余数。所述求和计算模块对经过所述码值转换模块转换的年值year、经过所述码值转换模块转换的日值day、所述月份修正译码模块输出的修正译码值、所述除4运算模块输出的年份除4取整结果进行求和。所述对7求余模块对所述求和计算模块输出的值进行除以7求余处理,余数即为输出的该天对应的星期值week。[0054]如图5所示,所述闰年判断模块为一闰年判定逻辑电路,所述闰年判断模块的输入端输入年值year,所述闰年判断模块输出一位指示信号:闰年指示信号leap,如果为闰年,leap输出1,如果不是,leap输出0。因为年份的头两位固定为20,所以闰年判断的规则可以简化为:如果年份的后两位数值是4的倍数则是闰年,否则不是闰年。闰年判断模块的输入的年值year取年份的后两位,并转换为8位bcd码,表示为year[7:0],通过逻辑电路对year[7:0]中的year[4]、year[1]、year[0]三位信号进行逻辑运算:year[4]&year[1]&!year[0]或者year[4]|year[1]|year[0],当逻辑表达式year[4]&year[1]&!year[0]的结果为真时,或者当逻辑表达式year[4]|year[1]|year[0]的结果为假时,该年份为闰年,否则不是闰年。[0055]如图6所示,所述码值转换模块为一bcd码-二进制码转换器,所述码值转换模块用于将年year/日day的bcd码值转换为自然二进制码值。所述码值转换模块对年year/日day的bcd码值的高4位乘以10再加上其bcd码的低4位,所得之和在电路中存储为自然二进制数。为了节省实现资源,本实施例中将乘10运算替换为对bcd码的高4位分别先进行左移1位和3位以分别实现乘2、乘8的功能,然后再将两者相加得到乘10的结果。[0056]如图7所示,所述码值转换模块包括加法器一和加法器二,年值year/日值day的bcd码值的高4位向左移一位得到的值和年值year/日值day的bcd码值的高4位向左移三位得到的值作为加法器一的输入,年值year/日值day的bcd码值的低4位和加法器一的输出值作为加法器二的输入,加法器二输出转换得到的自然二进制码值。操作数1:bcd码的十位code_in[7:4]左移3位,实现乘8的功能;操作数2:bcd码的十位code_in[7:4]左移1位,实现乘2的功能;操作数3:bcd码的个位code_in[3:0];三个操作数相加,得到转换后的码值输出值code_out[6:0]。该电路的核心是两个加法器。加法器可选用synopsys公司designwareip库中的dw01_add加法器模块,其输入a、b和输出sum的位宽可配置。这里将它们均配置为7位宽度。被转换的信号code_in[6:0]作为输入信号,转换后的信号code_out[6:0]为输出信号。电路连接关系:加法器addr1的进位输入端口ci接逻辑0,即接地;加法器addr1的输入端口a[6:3]接code_in[7:4],a[2:0]均接逻辑0,即接地;加法器addr1的输入端口b[4:1]接code_in[7:4],b[6]、b[5]、b[0]均接逻辑0,即接地;加法器addr2的进位输入端口ci接加法器addr1的进位输出端口co;加法器addr2的输入端口a[6:0]接加法器addr1的求和输出端sum;加法器addr2的进位输出端口co悬空不使用;加法器addr2的求和输出端sum即为码值转换模块的输出code_out[6:0]。[0057]所述除4运算模块对经过所述码值转换模块转换的年值year进行除4运算,结果是一个整数,结果只取商值,丢弃余数。为了节省实现资源,本实施例中所述除4运算模块除法使用对被除数进行逻辑右移两位的方式实现。使用逻辑右移的方式实现除法功能,是数字设计领域最基础的数字运算,属于公知技术。[0058]所述月份修正译码模块为一bcd码修正电路,所述月份修正译码模块包括两个输入端,其中一个输入端输入月值month,另一个输入端输入所述闰年判断模块输出的闰年指示信号leap值,所述月份修正译码模块根据月份以及闰年指示,分别对不同的月份输出一个对应的码值,当年份为闰年时,1~12月的修正译码值分别为5、1、2、5、0、3、5、1、4、6、2、4,当年份为非闰年时,1~12月的修正译码值分别为6、2、2、5、0、3、5、1、4、6、2、4。[0059]月份修正译码模块,输入信号有闰年指示信号leap以及月month值month[4:0],输出为mc[2:0]信号。mc的逻辑实现,可依据表2进行处理。[0060]表2月份修正译码真值表:leapmonth[4]month[3]month[2]month[1]month[0]mc[2]mc[1]mc[0]000001110000010010000011010000100101000101000000110011000111101001000001001001100010000110010001010010010100100001101100010001100011010100100101100101000100110011100111101101000001101001100110000110110001010110010100如图8所示,本实施例提供了一种可实施的月份修正译码逻辑电路图。其中,sel[5:0]作为选通控制信号,sel[5]接leap输入信号,sel[4:0]接month[4:0]输入信号。sel[5:0]的所有组合情况可划分为7组:选通控制组0~选通控制组6。被选择的信号有7组,用二进制表示分别为:000、001、010、011、100、101、110,它们是月份修正值的所有元素。选通控制组1的集合为{0x08、0x22、0x28};选通控制组2的集合为{0x02、0x03、0x11、0x23、0x31};选通控制组3的集合为{0x06、0x26};选通控制组4的集合为{0x09、0x12、0x29、0x32};选通控制组5的集合为{0x04、0x07、0x21、0x24、0x27};选通控制组6的集合为{0x01、0x10、0x30};选通控制组0的集合为{0x05、0x25、其它值};当由leap和month[4:0]所组成的选通信号sel[5:0]值落入某选通控制组,则对应的被选择输入信号作为相应月份的修正值输出到mc端口上。例如,leap=1,month[4:0]为0x11,则sel[5:0]为0x31,那么sel值落入选通控制组2,则对应的输入信号010被选择并输出到mc,即闰年11月份的月份修正值为2。[0061]所述求和计算模块对经过所述码值转换模块转换的年值year、经过所述码值转换模块转换的日值day、所述月份修正译码模块输出的修正译码值、所述除4运算模块输出的年份除4取整结果进行求和,得到sum[7:0]。求和计算模块使用加法器实现,求和计算模块可调用synopsys公司designware ip库中的dw01_add加法器ip模块。[0062]所述对7求余模块对所述求和计算模块输出的值进行除以7求余处理,余数即为输出的该天对应的星期值week。[0063]如图9所示,对7求余模块可调用synopsys公司designware ip库中的dw_div除法器ip模块,其输入a和b的位宽可以进行配置。这里配置为a为8位宽,b为3位宽。a连接求和计算模块的输出sum[7:0],b固定为常数7。则dw_div ip的remainder输出端口输出值为模7结果值。[0064]星期计算器的实现步骤是:1、首先输入设定年、月、日信号值以及闰年指示leap值,年、月、日均使用bcd码;2、硬件电路自动计算并给出星期值,结果也是bcd码。[0065]从年月日及leap信号值设定完毕到星期值的给出,所需用时长短,取决于采用的具体的电路工艺。完全使用组合逻辑即可实现该百年星期自动计算电路,如此,便可依据年月日的值实时计算对应的星期值。同时,也能避免年月日所对应的星期不一致的情况出现。根据图1和图4实现的星期自动计算电路,对2000年~2099年这一百年中的每一天都进行了星期计算,经逻辑仿真验证,每一天的星期值都是正确的。[0066]例如想知道2017年9月28日对应的星期值,则输入信号year、month、day分别设置为0x17、0x09、0x28,输入信号leap设置为0,经过星期自动计算电路的运算,得到的结果week为0x04,表示这天是星期四。[0067]例如想知道2036年4月15日对应的星期值,则输入信号year、month、day分别设置为0x36、0x04、0x15,输入信号leap设置为1,经过星期自动计算电路的运算,得到的结果week为0x02,表示这天是星期二。[0068]例如想知道2059年12月7日对应的星期值,则输入信号year、month、day分别设置为0x59、0x12、0x07,输入信号leap设置为0,经过星期自动计算电路的运算,得到的结果week为0x00,表示这天是星期天。[0069]完全使用组合逻辑即可实现星期计算电路,如此便可依据年、月、日值实时地计算对应的星期值。同时也能够避免年、月、日所对应的星期不一致的情况出现。[0070]闹钟发生器实现闹钟功能。设置控制寄存器中的控制位taen为1则开启闹钟功能。[0071]如图10所示,本实施例中,所述闹钟发生器输入日计数值、星期计数值、小时计数值、分计数值、秒计数值,并根据闹钟输入闹钟日值、闹钟星期值、闹钟小时值、闹钟分钟值、闹钟秒值,所述闹钟发生器包括选择器一、选择器二、比较器一、比较器二、比较器三、比较器四、或门一、或门二、或门三、与非门一、或门四、与门一,选择器一输入闹钟日值和闹钟星期值,选择器二输入日计数值和星期计数值,向选择器一、选择器二输入0或1的wdsel控制位选择比较日或星期,比较器四输入选择器一、选择器二输出的闹钟日值、日计数值或者闹钟星期值、星期计数值,比较器三输入闹钟小时值、小时计数值,比较器二输入闹钟分钟值、分计数值,比较器一输入闹钟秒值、秒计数值,若闹钟报警时间和当前时间一致,比较器输出报警标志flag,所述闹钟发生器包括日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器,日/星期报警寄存器、时报警寄存器、分报警寄存器、秒报警寄存器分别提供一位屏蔽控制位msk4、msk3、msk2、msk1,或门一输入比较器一输出的报警标志flag1和屏蔽控制位msk1信号,或门二输入比较器二输出的报警标志flag2和屏蔽控制位msk2信号,或门三输入比较器三输出的报警标志flag3和屏蔽控制位msk3信号,或门四输入比较器四输出的报警标志flag4和屏蔽控制位msk4信号,与非门一输入屏蔽控制位msk1、msk2、msk3、msk4信号,屏蔽控制位msk4、msk3、msk2、msk1分别是日/星期、时、分、秒的报警屏蔽控制位,为1时对应字段被屏蔽,所述与门一输入或门一、或门二、或门三、或门四、与非门一的输出以及使能位rtcen信号、控制位taen信号,所述与门一输出闹钟报警标志taif信号。[0072]通过读写访问接口控制电路,可以设定闹钟相关的寄存器:日/星期,时、分、秒的报警寄存器。通过闹钟寄存器中wdsel控制位可以选择比较日或星期。wdsel控制位若为1,对应使用日进行比较,若为0则使用星期进行比较。[0073]闹钟发生器的核心是数值比较电路。当闹钟报警时间和当前时间一致,状态寄存器rtc_sr中的报警标志位taif将会被置位。如果开启了闹钟中断报警使能taie,还会产生闹钟报警中断。[0074]控制寄存器rtc_cr中设置有一个寄存器位a12_24。若该位为0,表明闹钟设置的时间格式是12小时制;若该位为1,表明闹钟设置的时间格式是24小时制。若寄存器位a12_24为0,设置的小时闹钟报警寄存器值与12小时制下的小时寄存器进行比较;否则与24小时制下的小时寄存器进行比较,由此来解决当前时间小时制式和闹钟小时制之间的匹配问题。[0075]闹钟报警功能是可编程的,报警设定可由日/星期、时、分、秒中的任意日历字段来触发。闹钟报警功能可选日/星期、时、分、秒进行匹配,并分别提供屏蔽功能。当某字段被屏蔽(对应的msk控制位为1)后,其值是无关项,不再参与对应日历字段的比较。当所有屏蔽设置都开启时,将不再产生闹钟报警标志信号taif。[0076]小时寄存器hour安排有6位。当小时制选择12时,最高位代表是am(上午)/pm(下午)指示位,“0”表示上午am,“1”表示下午pm。12小时制和24小时制下的时间对照情况,参见表3。[0077]表3 24小时制和12小时制时间对照表24小时制hour寄存器值(十六进制)12小时制hour寄存器值(十六进制)0012(am12)0101(am01)0202(am02)0303(am03)0404(am04)0505(am05)0606(am06)0707(am07)0808(am08)0909(am09)1010(am10)1111(am11)1232(pm12)1321(pm01)1422(pm02)1523(pm03)1624(pm04)1725(pm05)1826(pm06)1927(pm07)2028(pm08)2129(pm09)2230(pm10)2331(pm11)闹钟报警功能可选日/星期、时、分、秒进行匹配,并分别提供屏蔽功能。每个报警寄存器中分别提供一位屏蔽控制位msk。msk高电平有效,即msk为1,则报警值是无关的,该日历字段不会触发报警。msk1、msk2、msk3、msk4这四个信号分别对秒、分、小时、日/星期四个日历字段提供屏蔽功能。当所有屏蔽设置都开启时,将不再产生闹钟报警标志信号taif。另外,产生闹钟报警标志信号的前提是控制寄存器中的模块使能rtcen开启,并且闹钟功能使能位taen也要开启。[0078]如图11所示,所述可以自动计算星期值的实时时钟单元电路还包括实时时钟中断电路,所述实时时钟中断电路包括选择器三、与门二、与门三、或门五、秒/半秒中断使能寄存器rtcie、秒/半秒中断标志寄存器rtcif、闹钟报警中断使能寄存器taie、闹钟报警中断标志寄存器taif,所述控制寄存器rtc_cr包括使能位rtcen以及用于产生rtcif标志位的选择控制信号的rtcints位,所述秒时钟产生器还提供半秒信号clk_2hz,所述状态寄存器rtc_sr包括rtcif标志位,选择器三输入clk_1hz和clk_2hz,选择控制信号rtcints连接选择器三的选择控制输入端,所述闹钟发生器输出的闹钟报警标志taif信号寄存至闹钟报警中断标志寄存器taif,所述状态寄存器rtc_sr的rtcif标志位连接秒/半秒中断标志寄存器rtcif,所述选择器三的输出端连接所述秒/半秒中断标志寄存器rtcif的输入端,所述秒/半秒中断标志寄存器rtcif的输出端、所述秒/半秒中断使能寄存器rtcie的输出端连接所述与门二的输入端,所述闹钟报警中断标志寄存器taif的输出端、所述闹钟报警中断使能寄存器taie的输出端连接所述与门三的输入端,所述与门二的输出端、所述与门三的输出端连接所述或门五的输入端,所述或门五的输出端输出rtc中断信号rtcint。[0079]实时时钟单元电路提供秒中断、半秒中断,根据应用需要可以进行二选一配置。同时也提供可编程闹钟报警中断功能,报警设定可由日/星期、时、分、秒中的任意日历字段来触发。这些中断可以被mcu/soc用于管理低功耗模式。比如每秒唤醒一次,或闹钟报警时间到了唤醒一次。如果每秒唤醒一次认为时间太久,可以设定选用半秒中断,以加快响应速度。[0080]秒/半秒中断和闹钟报警中断共用一个rtcint中断通道。[0081]如图12所示,在一种实施方式中,实时时钟单元电路挂接在apb总线上,为mcu或soc片上的实时时钟功能模块的场景。rtcint中断提供给nvic中断控制器,当发生中断时,可以唤醒cpu,达到低功耗管理控制的目的。[0082]apb总线上的系统时钟sysclk和单元电路的工作时钟rtc_clk可能是来自不同的时钟信号源。当通过apb接口,若不加同步化处理,而直接读取年、月、日、星期、时、分、秒值时,数据采样可能出现亚稳态。为了避免出现读取错误数据的现象发生,读取动作加入同步电路处理,同步电路包括apb同步读取寄存器。[0083]如图13所示,所述apb同步读取寄存器包括锁存控制器以及与所述锁存控制器连接的年锁存器、月锁存器、日锁存器、星期锁存器、小时锁存器、分锁存器、秒锁存器,所述锁存控制器的工作时钟为apb总线上的系统时钟sysclk,所述年锁存器、月锁存器、日锁存器、星期锁存器、小时锁存器、分锁存器、秒锁存器分别连接年计数器、月计数器、日计数器、星期计算器、小时计数器、分计数器、秒计数器。同步电路的工作时钟为apb总线上的系统时钟sysclk。[0084]锁存控制器实质上是一个正脉冲检测电路。读取寄存器值的同步触发信号为半秒信号的上升沿检出脉冲。[0085]如图14所示,锁存控制器电路中,前两个dff负责对输入的信号(使用半秒信号clk_2hz)做同步化处理,同步到apb的系统时钟域。然后再结合一个dff和一个二输入与门,构成输入信号的正跳变检测脉冲,宽度为一个系统时钟周期。[0086]对于寄存器的写入动作,为了尽量减少逻辑资源的占用,可以采用异步写入数据的方式。通过apb接口,向年、月、日、时、分、秒寄存器写入初值时,采用异步写入方式。在初始化寄存器数据时,先禁止模块工作使能位rtcen,此时设置日期时间寄存器初值时,因为单元电路尚无工作时钟,故不会发生亚稳态而造成写入失败现象的发生。当其它寄存器数值设定完毕后,再打开rtcen使能位,单元电路即开始正常工作。[0087]如图15所示,在另一种实施方式中,实时时钟单元电路挂接在i2c/spi总线或uart通信口上,此时对应于实时时钟专用芯片的场景。[0088]当只提供外部晶振xtosc(32768hz)时钟时,可将时钟源选择相关逻辑固定选择xtosc,或者删除时钟源选择逻辑。通过i2c/spi/uart通信口访问实时时钟的所有寄存器。通过读写访问接口控制逻辑电路进行读写操作,通信协议上可以规定每次可访问一个寄存器,也可以一次性连续访问多个寄存器。[0089]其中的i2c、spi、uart通信接口控制电路,其逻辑框图分别如图16、17、18所示。其职责是负责对通信帧进行解析,对寄存器集合中的寄存器进行相应的读写操作,完成进行接收数据和发送数据动作,实现双向通信功能。通过这些通信接口,外部系统总线或通信主机可以访问单元电路中的所有寄存器。[0090]本实时时钟单元电路的实现步骤是:1、外部主机经由系统总线或通信接口,和读写访问接口控制逻辑电路进行交互,首先对单元电路中的年、月、日、时、分、秒寄存器以及小时进制选择控制位n12_24写入正确的初始值。[0091]2、如果需要秒中断或半秒中断功能,通过读写访问接口控制逻辑电路,设定中断源选择控制位rtcints、打开秒/半秒中断使能控制位rtcie。[0092]3、如果需要设定闹钟,通过读写访问接口控制逻辑电路,设定闹钟报警时间,开启闹钟使能控制位taen。如果需要提供闹钟报警中断,则需要开启闹钟报警中断使能控制位taie。日历字段(日/星期、时、分、秒)均有相应的屏蔽控制msk位,可根据需要决定是否进行屏蔽某日历字段。[0093]4、通过读写访问接口控制逻辑电路,设定控制寄存器,选择实时时钟电路模块的工作时钟源,开启模块工作使能控制位rtcen。[0094]5、通过读写访问接口控制逻辑电路进行寄存器读取操作,获取年、月、日、星期、时、分、秒寄存器值。[0095]6、通过读写访问接口控制逻辑电路进行寄存器读取操作,读取状态寄存器中rtcif、taif中断标志位的值,可以获知是否发生秒/半秒中断或闹钟报警中断。如果开启了秒/半秒中断使能或闹钟报警中断使能,那么中断信号rtcint到来后可以触发mcu或soc转入对中断的处理,比如读取日历时间值或者处理其它需要定时处理的中断任务。rtcif、taif中断标志位可通过读写访问接口控制逻辑电路进行写操作将其清除(对于两中断标志位的清除动作,可以事先规定为写1清零,或者也可以事先规定为写0清零。)。[0096]7、可反复执行步骤5或6;8、欲关闭实时时钟电路,通过读写访问接口控制逻辑电路,对控制寄存器执行写操作,将模块工作使能位rtcen设置为0。此时,闹钟功能也是被关闭的,无论taen是否开启使能。[0097]实时时钟单元的焦点是星期计算器。对2000年~2099年这一百年中的每一天都进行了星期计算,经逻辑仿真验证,每一天的星期值都是正确的。星期计算器的输入信号year、month、day、leap,输出信号为week。抽取若干样本,输入和输出之间的时序波形图如图19所示。波形图中代表的含义:17年(平年)9月28日,星期四;36年(闰年)4月15日,周二;59年(平年)12月7日,周日;92年(闰年)3月31日,周一。[0098]除上述优选实施例外,本发明还有其他的实施方式,本领域技术人员可以根据本发明作出各种改变和变形,只要不脱离本发明的精神,均应属于本发明所附权利要求所定义的范围。

本文地址:https://www.jishuxx.com/zhuanli/20240730/149989.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

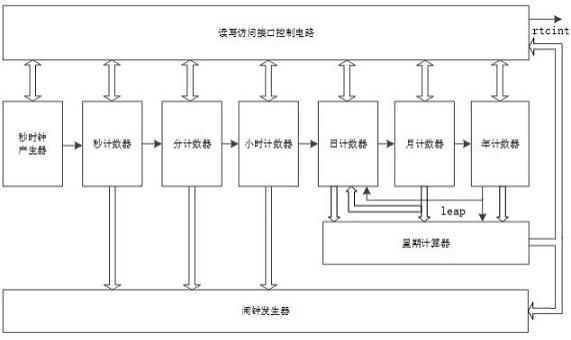

返回列表