脉冲的采样方法、采样系统、装置及计算机可读存储介质与流程

- 国知局

- 2024-07-30 09:37:01

1.本技术涉及光子探测领域,特别是涉及一种脉冲的采样方法、采样系统、装置及计算机可读存储介质。背景技术:2.正电子发射断层成像(pet)是一种高端核医学成像装备,广泛用于癌症诊疗、脑科学研究、心脏病学研究、重离子放疗监测等领域,其中大量使用伽马射线探测器作为系统前端。伽马射线探测器对伽马光子能量信息、时间信息、空间信息的分辨能力直接决定了系统的成像质量,而由于pet对时间性能的要求,目前得到应用的pet伽马射线探测器基本以闪烁晶体(典型的有lyso、bgo、yso等)+光电器件为基本结构。伽马射线首先与闪烁晶体相互作用将能量转换为可见光光子,可见光光子经过输运后射出闪烁晶体成为光电器件的入射光。光电器件将入射光转换为光电流,再经过后端的电子学和软件算法提取出射线的时间、能量、空间位置等信息。3.近年来,随着数字信号处理技术和方法的发展,将脉冲直接数字化,利用软件算法替代传统模拟电路提取粒子能量沉积信息的方式极具发展潜力。多电压阈值采样(multi-voltage threshold)方法通过tdc(时间数字转换)获得输入波形越过设定阈值的时间信息,从而反演出波形信息。通常需要多个通道(如4通道)的阈值比较以及后续的时间测量,tdc通常利用fpga内部的进位链来实现,需要消耗一定的fpga内部的逻辑资源来实现。通常的,单个通道的波形对应4个通道的比较器(lvdscomparator),需要消耗fpga芯片8个输入管脚以及8个通道的tdc测量模块,而一个fpga通常需要处理几十上百个通道的信号,例如,针对一个最常见的12*6的探测器阵列,总共有72路信号输入,则需要的输入管脚数量为576个,单个tdc模块逻辑资源消耗约2~3k。4.一般的,单个fpga芯片无法满足管脚或是逻辑资源的要求。一种解决方法是选用多个fpga芯片例如2个fpga芯片。但是双fpga芯片的资源使用率达到80%以上。并且由于资源的限制,tdc模块的测量精度也收到了制约。另外过高的资源使用率,使得板卡发热量较大,工作温度过高,tdc测量精度收到影响,同时也加大了系统散热设计难度。而使用更多的fpga芯片则增加了成本。技术实现要素:5.本技术实施例所要解决的技术问题在于,如何降低脉冲时间采样过程中的资源消耗,提升采样性能。6.为了解决上述问题,本技术公开一种脉冲的采样方法、采样系统、装置及计算机可读存储介质。所述方法包括:获取待处理脉冲,以及一个或以上阈值电压;各通道同时比较所述待处理脉冲与所述一个或以上阈值电压,确定所述待处理脉冲越过所述阈值电压时,分别与所述一个或以上阈值电压对应的一个或以上状态变化信号;对所述一个或以上状态变化信号执行延迟处理,获取对应的一个或以上延迟状态变化信号;依次对所述一个或以上延迟状态变化信号进行时间采样,获取对应的一个或以上脉冲电压-时间对。7.在一个可行的实现方式中,所述状态变化信号包括指示所述待处理脉冲首次越过所述阈值电压的上升沿以及二次越过所述阈值电压的下降沿;其中,所述对所述一个或以上状态变化信号执行延迟处理,获取对应的一个或以上延迟状态变化信号包括:分别获取对应于所述一个或以上状态变化信号的一个或以上预设时间差;对于每一个状态变化信号,基于所述预设时间差,调整所述上升沿的第一位置至第二位置和所述下降沿的第三位置至第四位置;指定调整后的状态变化信号为所述延迟状态变化信号;其中,所述一个或以上延迟状态变化信号的所述上升沿的的第二位置不相同,所述下降沿的第四位置不相同。8.在一个可行的实现方式中,所述依次对所述一个或以上延迟状态变化信号进行时间采样包括:基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样;基于第二顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样。9.在一个可行的实现方式中,所述第一顺序为根据所述一个或以上阈值电压的电压值按从小到大排序确定的排列顺序;所述基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样包括:对所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样;确定所述第一时间采样是否成功;若是,按照所述第一顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第一顺序中排序末位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻完成所述第一时间采样;若否,重新执行所述第一时间采样。10.在一个可行的实现方式中,所述第二顺序为根据所述一个或以上阈值电压的电压值按从大到小排序确定的排列顺序;所述基于第二处理顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样包括:对所述第二顺序中排序首位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应时刻执行第二时间采样;确定所述第二时间采样是否成功;若是,按照所述第二顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第二顺序中排序末尾的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应时刻完成所述第一时间采样;若否,重新执行所述第二时间采样。11.在一个可行的实现方式中,所述采样方法还包括:获取基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样的采样反馈;确定所述采样反馈是否指示所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样是否成功;若是,基于第二顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应时刻执行第二时间采样。12.在一个可行的实现方式中,所述脉冲电压-时间对包括针对所述延迟状态变化信号进行时间采样获取的延迟状态变化时间以及所述延迟状态变化信号对应的阈值电压。13.在一个可行的实现方式中,所述采样方法还包括:针对每一个状态变化信号,14.基于所述预设时间差调整所述延迟状态变化时间至目标状态变化时间;指定所述目标状态变化时间以及所述状态变化信号对应的阈值电压构成脉冲电压-目标时间对。15.本技术另一方面公开一种脉冲的采样系统。所述采样系统包括获取模块、比较模块、延迟模块、采样模块。所述获取模块用于获取待处理脉冲,以及一个或以上阈值电压。所述比较模块用于同时比较各通道中所述待处理脉冲与所述一个或以上阈值电压,确定所述待处理脉冲越过所述阈值电压时,分别与所述一个或以上阈值电压对应的一个或以上状态变化信号。所述延迟模块用于对所述一个或以上状态变化信号执行延迟处理,获取对应的一个或以上延迟状态变化信号。所述采样模块用于依次对所述一个或以上延迟状态变化信号进行时间采样,获取对应的一个或以上脉冲电压-时间对。16.本技术另一方面提供一种脉冲的采样装置。所述采样装置包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述计算机程序被所述处理器执行时实现如上所述的采样方法的步骤。17.本技术另一方面提供一种计算机可读存储介质。所述存储介质上存储计算机程序,所述计算机程序被处理器执行时实现如上所述的采样方法的步骤。18.本技术所披露的脉冲的采样方法、采样系统、装置及计算机可读存储介质,可以节省处理资源,降低系统功耗,同时提升采样精度。附图说明19.本技术将以示例性实施例的方式进一步说明,这些示例性实施例将通过附图进行详细描述。这些实施例并非限制性的,在这些实施例中,相同的编号表示相同的结构,其中:20.图1是根据本技术的一些实施例所示的脉冲采样的示例性流程图;21.图2是根据本技术的一些实施例所示的确定延迟状态信号的示例性流程图;22.图3是根据本技术的一些实施例所示的延迟状态变化信号的时间采样的示例性流程图;23.图4是根据本技术的一些实施例所示的延迟状态变化信号的时间采样的另一种示例性流程图;24.图5是根据本技术的一些实施例所示的阈值电压与待处理脉冲的示例性关系示意图;25.图6是根据本技术的一些实施例所示的状态变化信号的示例性示意图;26.图7是根据本技术的一些实施例所示的延迟状态变化信号的示例性示意图;27.图8是根据本技术的一些实施例所示的用于脉冲采样的数据处理系统的示例性模块图;28.图9是根据本技术的一些实施例所示的用于脉冲采样的数据处理系统的示例性功能框图。具体实施方式29.为使本技术的上述目的、特征和优点能够更加明显易懂,下面结合附图对本技术的具体实施方式做详细的说明。在下面的描述中阐述了很多具体细节以便于充分理解本技术。但是本技术能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本技术内涵的情况下做类似改进,因此本技术不受下面公开的具体实施例的限制。30.需要说明的是,当元件被称为“固定于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中的元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。31.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。本文所使用的术语“及/或”或“和/或”包括一个或多个相关的所列项目的任意的和所有的组合。32.以下参考附图对本技术的一些优选实施例进行说明。应当注意的是,以下描述是为了说明的目的,并不旨在限制本技术的保护范围。33.图1是根据本技术一些实施例所示的脉冲采样的示例性流程图。在一些实施例中,流程10可以由数据处理系统80执行。例如,流程10可以以程序或指令的形式存储在存储装置(如数据处理系统80的自带存储单元或外接存储设备)中,所述程序或指令在被执行时,可以实现流程10。如图1所示,流程10可以包括以下操作。34.步骤11,获取待处理脉冲,以及一个或以上阈值电压。该步骤可以由获取模块81执行。35.在一些实施例中,所述待处理脉冲可以是由pet的光探测器(例如,光电倍增管pmt、硅光电倍增管sipm、雪崩光电二极管apd等)所输出的有效脉冲。获取模块81可以通过与该光探测器进行通信,以获取所述待处理脉冲。36.在一些实施例中,所述一个或以上阈值电压可以用于与所述待处理脉冲进行比较。比较结果可以用于时间采样,确定所述待处理脉冲越过所述一个或以上阈值电压的时间点。这些时间点可以用于后续处理(例如,图像重建)过程中的波形恢复。这样可以恢复波形的面积,进而得到波形能量值。在一些实施例中,所述一个或以上阈值电压的电压值均在所述待处理脉冲的幅值之内。例如,假定所述待处理脉冲的幅值范围在3mv-120mv,则所述一个或以上阈值电压的电压值均在以上范围之内。例如,四个阈值电压分别为20mv、40mv、60mv以及80mv。37.参考图5,图5是根据本技术一些实施例所示的阈值电压与脉冲的示例性关系示意图。如图5所示,51表示脉冲,其可以是本技术中所提到的待处理脉冲。图中脉冲的波形显示了具有的特点,即上升时段非常短,通常只有几个纳秒的时间,就可以上升至最高点。而下降时段较长,一般会有100纳秒左右。521、522、523以及524表示四个不同的阈值电压。可以看出,四个阈值电压的大小全部都处于脉冲的幅值之内。38.在一些实施例中,所述一个或以上阈值电压可以由数字模拟转换器(digital-to-time converter,dac)设置。在设置完毕后,dac可以将所述阈值电压传输至获取模块81。39.步骤12,各通道同步比较所述待处理脉冲与所述一个或以上阈值电压,确定所述待处理脉冲越过所述阈值电压时,分别与所述一个或以上阈值电压对应的一个或以上状态变化信号。该步骤可以由比较模块82执行。40.在一些实施例中,比较模块82可以由包括低压差分信号(low-voltage differential signaling,lvds)比较器的电路实现。作为示例,由光探测器产生的脉冲可以输入到lvds管脚p端(也可以被称为正端),阈值电压可以输入到lvds管脚n端(也可以被称为负端),从而完成脉冲波形与阈值电压的比较。41.在一些实施例中,比较模块82可以包括有一个或以上lvds比较器。每一个lvds比较器可以用于所述待处理闪烁买脉冲与一个阈值电压的比较。如此,可以实现同步并行比较所述待处理脉冲与所述一个或以上阈值电压。42.可以知道的是,对于一个阈值电压,脉冲可以两次越过阈值电压。一次是在脉冲的上升阶段,脉冲可以越过阈值电压并高于阈值电压。一次是在脉冲的下降阶段,脉冲可以越过阈值电压并低于阈值电压。返回参考图5,在上升阶段,脉冲51会首先越过并高于阈值电压521,随后继续往上,越过并高于阈值电压522。接下来会越过并高于阈值电压523以及阈值电压524。在下降阶段,脉冲51会首先越过并低于阈值电压524。随后继续向下,越过并低于阈值电压523。接下来会越过并低于阈值电压522以及阈值电压521。整个过程脉冲电压51相对于以上四个阈值电压可以发生8次状态变化。43.在一些实施例中,比较模块82在比较所述待处理脉冲与所述阈值电压后,输出一状态变化信号。所述状态变化信号可以指示所述待处理脉冲相对于所述阈值电压的状态变化(例如,从低于阈值电压到越过并高于阈值电压或从高于阈值电压到越过并低于阈值电压)。本技术后续部分所涉及时间采样,可以是指对该状态跳变对应的时刻进行时间测量。参考图6,图6是根据本技术一些实施例所示的状态变化信号的示例性示意图。状态变换信号611、612、613以及614分别对应阈值电压521、522、523以及524。每一个状态变换信号包括一个上升沿和一个下降沿。例如,上升沿①、②、③以及④,下降沿⑤、⑥、⑦以及⑧。上升沿表示待处理脉冲从下往上越过并高于阈值电压,下降沿表示待处理脉冲从上往下越过并低于阈值电压。上升沿和下降沿所在位置对应的时刻则可以是脉冲越过阈值电压的时刻。44.步骤13,对所述一个或以上状态变化信号执行延迟处理,获取对应的一个或以上延迟状态变化信号。该步骤可以由延迟模块83执行。45.继续返回参考图6,从图6中可以看出,由于脉冲的特点,每个阈值电压对应的状态变化信号的上升沿非常接近,使得每个上升沿所在位置对应的时刻也非常接近。这不利于后续的数据处理过程,例如,基于脉冲波形的时间采样结果进行图像重建的过程。因此,本技术所披露的方法,可以对所述一个或以上状态变化信号执行延迟处理,使得各阈值电压对应的状态变化信号的上升沿的位置错开。作为一个示例,延迟模块83可以获取对应于每个状态变化信号的时间差,然后将该时间差叠加到状态变化信号之上,使其上升沿和下降沿的位置同时往后推迟,从而达到错开各状态变化信号的上升沿的目的。关于获取延迟状态变化信号的具体描述可以参考本技术图2部分,在此不再赘述。46.步骤14,依次对所述一个或以上延迟状态变化信号进行时间采样,获取对应的一个或以上脉冲电压-时间对。该步骤可以由采样模块84执行。47.在一些实施例中,所述时间采样可以是针对延迟状态变化信号的上升沿以及下降沿所在位置对应的时刻进行时间数字化采样。在本技术中,术语“时间采样”、“时间数字化采样”以及“时间测量”可以互换使用,用以表示确定上升沿以及下降沿所在位置对应的时刻这一操作。采样模块84可以按照一定的采样顺序,分别对以上延迟状态变化信号的上升沿和下降沿对应的时刻进行采样。在一些实施例中,采样模块84可以由包括信号通路控制器(signalroutecontrol,src)以及时间数字转换器(time-to-digital converter,tdc)的电路实现。采样模块84可以利用tdc对输入的延迟状态变化信号的上升沿或下降沿所在位置对应的时刻进行采样,利用src对输入进tdc的延迟状态变化信号进行选择控制。在一些实施例中,采样模块84基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样,并基于第二顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样。关于延迟状态变化信号的时间采样的具体描述可以参考本技术图3-图4部分。48.在一些实施例中,所述脉冲电压-时间对可以包括针对所述延迟状态变化信号进行时间采样获取的延迟状态变化时间以及所述延迟状态变化信号对应的阈值电压。例如,对于某一阈值电压v,其与待处理脉冲的比较可以得到状态变化信号。tdc对经过延迟处理得到的状态变化信号进行时间测量可以获取两个时刻,包括上升沿的位置对应的时刻t1以及下降沿的位置对应的时刻t2。t1和t2可以被称为延迟状态变化时间,所述脉冲电压-时间对可以包括v-t1以及v-t2。49.在一些实施例中,数据处理系统80(例如,后处理模块,图8中未示出)可以对所述脉冲电压-时间对进行后处理,获取脉冲电压-目标时间对。继续参考上述示例,可以知道的是,t1与t2对应的延迟状态变化信号的上升沿和下降沿的位置是经过的预设时间差的位置长度后移的。因此,所述后处理模块可以基于所述预设时间差调整所述延迟状态变化时间至目标状态变化时间。所述目标状态变化时间可以是利用所述延迟状态变化时间减去所述预设时间差,用于指示阈值电压对应的状态变换信号的上升沿和下降沿的位置对应的时刻。作为示例,假定所述预设时间差为δt可以被称为延迟状态变化时间为,t1和t2,则所述目标状态时间可以是,(t1-δt)和(t2-δt)。所述后处理模块还可以指定所述目标状态变化时间以及所述状态变化信号对应的阈值电压构成脉冲电压-目标时间对。例如,所述脉冲电压-目标时间对可以包括v-(t1-δt)以及v-(t2-δt)。50.在一些实施例中,所述脉冲电压-目标时间对可以被传输至其他部件进行进一步的处理。例如,数据处理系统80可以通过有线或无线的通信方式,将所述采样结果传输至pet设备相关的图像处理部件,用于后续的pet图像重建。51.应当注意的是,上述有关图1中的各个步骤的描述仅仅是为了示例和说明,而不限定本说明书的适用范围。对于本领域技术人员来说,在本说明书的指导下可以对图1中的各个步骤进行各种修正和改变。然而,这些修正和改变仍在本说明书的范围之内。52.本技术所披露的脉冲采样方法,可以实现时间采样模块的复用,极大的节省计算资源,有效降低了能耗。同时节省的资源可以提升时间采样的精度,从而提供系统性能。53.图2是根据本技术的一些实施例所示的确定延迟状态信号的示例性流程图。在一些实施例中,流程20可以由数据处理系统80执行。例如,流程20可以以程序或指令的形式存储在存储装置(如数据处理系统80的自带存储单元或外接存储设备)中,所述程序或指令在被执行时,可以实现流程20。在一些实施例中,流程20可以由延迟模块82执行。如图2所示,流程20可以包括以下操作。54.步骤21,分别获取对应于所述一个或以上状态变化信号的一个或以上预设时间差。55.在一些实施例中,所述状态变化信号包括指示所述待处理脉冲首次越过所述阈值电压的上升沿以及二次越过所述阈值电压的下降沿。也就是所述待处理脉冲从下往上越过并高于所述阈值电压,以及从上往下越过并低于所述阈值电压。这些状态变化可以由上升沿以及下降沿表征。上升沿所在位置对应的时刻可以是所述待处理脉冲首次越过所述阈值电压的时刻,下降沿所在位置对应的时刻可以是所述待处理脉冲二次越过所述阈值电压的时刻。56.由前述说明可知,各状态变化信号的上升沿非常接近,需要进行错开。所述预设时间差的大小可以说明各状态变化信号的延迟程度。结合图5以及图6进行示例说明:若需要一个基准信号,则可以不延迟脉冲第一次越过的阈值电压对应的状态变化信号,也就是阈值电压511对应的状态变换信号611。此时,状态变化信号611对应的预设时间差可以是0。其他的预设时间差可以采用例如简单等比例增长的形式确定。例如,状态变换信号612对应的预设时间差可以是δt,状态变换信号613对应的预设时间差可以是2δt,状态变换信号613对应的预设时间差可以是3δt。57.步骤22,对于每一个状态变化信号,基于所述预设时间差,调整所述上升沿的第一位置至第二位置和所述下降沿的第三位置至第四位置。58.在一些实施例中,所述预设时间差可以对应一段位移长度,延迟模块83可以将所述状态变化信号的上升沿和下降沿的位置往后推移该位移长度,以完成延迟操作。参考图6,假定状态变化信号611对应的预设时间差是0,状态变换信号610-2对应的预设时间差是δt,状态变换信号613对应的预设时间差是2δt,状态变换信号613对应的预设时间差是3δt。延迟模块83可以将各状态变化信号的上升沿(包括上升沿①、②、③以及④)以及下降沿(包括下降沿⑤、⑥、⑦以及⑧)所在的位置分别往后推移预设时间差对应的位移长度。状态变化信号611的上升沿和下降沿的位置不发生变化,状态变化信号612的上升沿和下降沿的位置分别往后推移δt对应的位移长度,状态变化信号613的上升沿和下降沿的位置分别往后推移2δt对应的位移长度,状态变化信号614的上升沿和下降沿的位置分别往后推移3δt对应的位移长度。完成后,各状态变化信号的上升沿以及下降沿将各自错开。59.步骤23,指定调整后的状态变化信号为所述延迟状态变化信号。60.参考图6和图7,图7是根据本技术一些实施例所示的延迟状态变化信号的示例性示意图。状态变化信号611的上升沿①的第一位置以及下降沿⑧的第三位置经过延迟处理后并未发生变化,所获取的结果为延迟状态变化信号711。延迟状态变化信号711的上升沿①’的第二位置和下降沿⑧’的第四位置与状态变化信号611的上升沿①第二位置以及下降沿⑧的第四位置相同。状态变化信号612的上升沿②的第一位置以及下降沿⑦的第三位置后移了δt对应的位移长度,所获取的结果为延迟状态变化信号712。延迟状态变化信号712的上升沿②’的第二位置以及下降沿⑦’的第四位置相较于状态变化信号612的上升沿②以及下降沿⑦后移了δt对应的位移长度。状态变化信号613的上升沿③第一位置以及下降沿⑥的第三位置后移了2δt,所获取的结果为延迟状态变化信号713。延迟状态变化信号713的上升沿③’的第三位置以及下降沿⑥’的第四位置相较于状态变化信号613的上升沿③以及下降沿⑥后移了2δt对应的位移长度。状态变化信号614的上升沿④的第一位置以及下降沿⑤的第三位置后移了3δt,所获取的结果为延迟状态变化信号714。延迟状态变化信号714的上升沿④’的第二位置以及下降沿⑤’的第四位置相较于状态变化信号614的上升沿④以及下降沿⑤后移了3δt对应的位移长度。61.在一些实施例中,在经过延迟处理后,各延迟状态变化信号的上升沿和下降沿不接近。也就是说,所述一个或以上延迟状态变化信号的所述上升沿的第二位置不相同,所述下降沿的第四位置不相同。如此,各上升沿的位置对应的时刻不接近,各下降沿的位置对应的时刻也不接近。62.应当注意的是,上述有关图2中的各个步骤的描述仅仅是为了示例和说明,而不限定本说明书的适用范围。对于本领域技术人员来说,在本说明书的指导下可以对图1中的各个步骤进行各种修正和改变。然而,这些修正和改变仍在本说明书的范围之内。63.图3是根据本技术的一些实施例所示的延迟状态变化信号的时间采样的示例性流程图。在一些实施例中,流程30可以由数据处理系统80执行。例如,流程30可以以程序或指令的形式存储在存储装置(如数据处理系统80的自带存储单元或外接存储设备)中,所述程序或指令在被执行时,可以实现流程30。在一些实施例中,流程30可以由采样模块84执行。如图3所示,流程30可以包括以下操作。64.步骤31,对所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样。65.在一些实施例中,所述第一顺序可以是根据所述一个或以上阈值电压的电压值按从小到大排序确定的排列顺序。采样模块84可以首先对排序首位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样。参考图5和图7,四个阈值电压中,按从小到大排列后排序首位的是阈值电压611,与其对应的是延迟状态变化信号711。各延迟状态变化信号从延迟模块83输出后,将输入至采样模块84的src。src可以选择性地将延迟状态变换信号输出至tdc以进行时间采样。在步骤31中,src将首先输出延迟状态变化信号711至tdc。tdc可以对延迟状态变化信号711的上升沿①’的第二位置对应的时刻进行时间采样。66.步骤32,确定所述第一时间采样是否成功。67.在一些实施例中,采样模块84的tdc在对所述延迟状态变化信号进行时间采样时,可以同时输出一反馈。所述反馈可以包括数字、字母、符号等中的一个或以上组合。例如,所述反馈可以是1或0。1表示脉冲越过并高于阈值电压,0表示脉冲越过并低于阈值电压。如此,在针对延迟状态变化信号的上升沿的第二位置对应的时刻的时间采样时,若输出的反馈是1,则表示采样成功。反之,若输出的反馈是0,则表示采样失败。当所述第一时间采样成功时,流程30可以行进至步骤33。否则,流程30将返回执行步骤31,重新执行对所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样。68.步骤33,按照所述第一顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第一顺序中排序末位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻完成所述第一时间采样。69.在一些实施例中,当所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的时间采样成功后,采样模块84可以对排序次位的阈值电压对应的延迟状态信号进行第一时间采样。继续参考图5和图7,四个阈值电压中,按从小到大排列后排序次位的是阈值电压612,与其对应的是延迟状态变化信号712。采样模块84在完成对阈值电压611对应的延迟状态变化信号711的上升沿的第二位置对应的时刻的第一时间采样后,src可以延迟状态变换信号712输出至tdc以进行时间采样。tdc可以对延迟状态变化信号712的上升沿②’的位置对应的时刻进行第一时间采样。当针对延迟状态变换信号712的采样成功后,例如,tdc输出1的反馈后,src可以排名第三位的阈值电压613对应的延迟状态变换信号713输出至tdc以进行第一时间采样。随后是排名末位的阈值电压614对应的延迟状态变换信号714。当完成延迟状态变换信号714的上升沿④’对应的时刻的第一时间采样后,流程30可以结束。70.应当注意的是,上述有关图3中的各个步骤的描述仅仅是为了示例和说明,而不限定本说明书的适用范围。对于本领域技术人员来说,在本说明书的指导下可以对图1中的各个步骤进行各种修正和改变。然而,这些修正和改变仍在本说明书的范围之内。71.图4是根据本技术的一些实施例所示的延迟状态变化信号的时间采样的另一示例性流程图。在一些实施例中,流程40可以由数据处理系统80执行。例如,流程40可以以程序或指令的形式存储在存储装置(如数据处理系统80的自带存储单元或外接存储设备)中,所述程序或指令在被执行时,可以实现流程40。在一些实施例中,流程40可以由采样模块84执行。如图4所示,流程40可以包括以下操作。72.步骤41,对所述第二顺序中排序首位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样。73.在一些实施例中,所述第二顺序可以是根据所述一个或以上阈值电压的电压值按从大到小排序确定的排列顺序。采样模块84可以首先对排序首位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样。参考图5和图7,四个阈值电压中,按从大到小排列后排序首位的是阈值电压614,与其对应的是延迟状态变化信号714。各延迟状态变化信号从延迟模块83输出后,将输入至采样模块84的src。src可以选择性地将延迟状态变换信号输出至tdc以进行时间采样。在步骤41中,src将首先输出延迟状态变化信号714至tdc。tdc可以对延迟状态变化信号714的下降沿⑤’对应的时刻进行时间采样。74.步骤42,确定所述第二时间采样是否成功。75.在一些实施例中,采样模块84的tdc在对所述延迟状态变化信号进行时间采样时,可以同时输出一反馈。所述反馈可以包括数字、字母、符号等中的一个或以上组合。例如,所述反馈可以是1或0。1表示脉冲越过并高于阈值电压,0表示脉冲越过并低于阈值电压。如此,在针对延迟状态变化信号的下降沿的第四位置对应的时刻的时间采样时,若输出的反馈是0,则表示采样成功。反之,若输出的反馈是1,则表示采样失败。当所述第二时间采样成功时,流程40可以行进至步骤43。否则,流程40将返回执行步骤41,重新执行对所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应的时刻第二时间采样。76.步骤43,按照所述第二顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第二顺序中排序末位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应的时刻完成所述第二时间采样。77.在一些实施例中,当所述第二顺序中排序首位的阈值电压对应的延迟状态变化信号的时间采样成功后,采样模块84可以对排序次位的阈值电压对应的延迟状态信号进行第二时间采样。继续参考图5和图7,四个阈值电压中,按从大道小排列后排序次位的是阈值电压613,与其对应的是延迟状态变化信号713。采样模块84在完成对阈值电压614对应的延迟状态变化信号714的下降沿的第四位置对应的时刻第二时间采样后,src可以延迟状态变换信号713输出至tdc以进行时间采样。tdc可以对延迟状态变化信号713的下降沿⑥’的位置对应的时刻进行第二时间采样。当针对延迟状态变换信号713的下降沿的第四位置对应的时刻的采样成功后,例如,tdc输出0的反馈后,src可以排名第三位的阈值电压612对应的延迟状态变换信号712输出至tdc以进行第二时间采样。随后是排名末位的阈值电压611对应的延迟状态变换信号711。当完成延迟状态变换信号711的下降沿⑧’的位置对应的时刻的第二时间采样后,流程40可以结束。78.在一些实施例中,流程30和流程40可先后进行。采样模块84可以获取取基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样的采样反馈。所述采样反馈可以是针对第一顺序中排序末位的阈值电压对应的延迟状态变化信号的时间采样的反馈。例如,该采样反馈可以同样是1或0。采样模块84可以确定所述采样反馈是否指示所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样是否成功。例如,若所述采样反馈是1,则说明所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样成功。否则,则说明所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样失败。若所述采样反馈指示所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样成功,采样模块84可以开始基于第二顺序依次对所述一个或以上延迟状态变化信号的第四状态变化时刻执行第二时间采样。也就是说,采样模块84可以在执行完流程30且确定所有的第一时间采样成功后,再执行流程40。79.应当注意的是,上述有关图4中的各个步骤的描述仅仅是为了示例和说明,而不限定本说明书的适用范围。对于本领域技术人员来说,在本说明书的指导下可以对图1中的各个步骤进行各种修正和改变。然而,这些修正和改变仍在本说明书的范围之内。80.图8是根据本说明书一些实施例所示的数据处理系统的示例性模块图。该数据处理系统可以实现高性能的脉冲的采样。如图8所示,数据处理系统80可以包括获取模块81、比较模块82、延迟模块83以及采样模块84。81.获取模块81可以用于获取待处理脉冲,以及一个或以上阈值电压。所述待处理脉冲可以是由pet的光探测器(例如,光电倍增管pmt、硅光电倍增管sipm、雪崩光电二极管apd等)所输出的有效脉冲。所述一个或以上阈值电压可以用于与所述待处理脉冲进行比较。82.比较模块82可以用于同步并行比较所述待处理脉冲与所述一个或以上阈值电压,确定所述待处理脉冲越过所述阈值电压时,分别与所述一个或以上阈值电压对应的一个或以上状态变化信号。比较模块82可以由包括低压差分信号(low-voltage differential signaling,lvds)比较器的电路实现。比较模块82可以包括有一个或以上lvds比较器。每一个lvds比较器可以用于所述待处理闪烁买脉冲与一个阈值电压的比较。如此,可以实现同步并行比较所述待处理脉冲与所述一个或以上阈值电压。比较模块82在比较所述待处理脉冲与所述阈值电压后,输出一状态变化信号。所述状态变化信号可以指示所述待处理脉冲相对于所述阈值电压的状态变化。所述状态变化信号包括指示所述待处理脉冲首次越过所述阈值电压的上升沿以及二次越过所述阈值电压的下降沿。83.延迟模块83可以对所述一个或以上状态变化信号执行延迟处理,获取对应的一个或以上延迟状态变化信号。延迟模块83可以获取对应于每个状态变化信号的时间差,然后将该时间差叠加到状态变化信号之上,使其上升沿和下降沿的位置同时往后推迟,从而达到错开各状态变化信号的上升沿的目的。在一些实施例中,延迟模块83可以分别获取对应于所述一个或以上状态变化信号的一个或以上预设时间差。对于每一个状态变化信号,延迟模块83可以基于所述预设时间差,调整所述上升沿的第一位置至第二位置和所述下降沿的第三位置至第四位置,并指定调整后的状态变化信号为所述延迟状态变化信号。所述一个或以上延迟状态变化信号的所述上升沿的的第二位置不相同,所述下降沿的第四位置不相同。84.采样模块84可以依次对所述一个或以上延迟状态变化信号进行时间采样,获取对应的一个或以上脉冲电压-时间对。采样模块84可以由包括信号通路控制器(signalroutecontrol,src)以及时间数字转换器(time-to-digital converter,tdc)的电路实现。采样模块84可以利用tdc对输入的延迟状态变化信号的上升沿或下降沿所在位置对应的时刻进行采样,利用src对输入进tdc的延迟状态变化信号进行选择控制。在一些实施例中,采样模块84可以采样模块84基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样,并基于第二顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应的时刻执行第二时间采样。所述第一顺序为根据所述一个或以上阈值电压的电压值按从小到大排序确定的排列顺序。采样模块84可以对所述第一顺序中排序首位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样。若第一时间采样成功,采样模块84可以按照所述第一顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第一顺序中排序末位的阈值电压对应的延迟状态变化信号的上升沿的第二位置对应的时刻完成所述第一时间采样。若不成功,则重新执行所述第一时间采样。述第二顺序为根据所述一个或以上阈值电压的电压值按从大到小排序确定的排列顺序。采样模块84可以对所述第二顺序中排序首位的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应时刻执行第二时间采样。若第二时间采样成功,采样模块84可以按照所述第二顺序对其余阈值电压对应的延迟状态变化信号执行上述操作,直至所述第二顺序中排序末尾的阈值电压对应的延迟状态变化信号的下降沿的第四位置对应时刻完成所述第二时间采样。若不成功,则重新执行所述第二时间采样。在一些实施例中,采样模块84可以首先获取基于第一顺序依次对所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻执行第一时间采样的采样反馈。若确定所述采样反馈是否指示所述一个或以上延迟状态变化信号的上升沿的第二位置对应的时刻的第一时间采样成功,则继续基于第二顺序依次对所述一个或以上延迟状态变化信号的下降沿的第四位置对应时刻执行第二时间采样。85.在一些实施例中,数据处理系统80还可以包括后处理模块。对于每一个状态变化信号,所述后处理模块可以基于所述预设时间差调整所述延迟状态变化时间至目标状态变化时间,并指定所述目标状态变化时间以及所述状态变化信号对应的阈值电压构成脉冲电压-目标时间对。86.关于上述模块的其他描述,可以参考本技术其他部分,例如,图1-图7。87.应当理解,图7所示的系统及其模块可以利用各种方式来实现。例如,在一些实施例中,系统及其模块可以通过硬件、软件或者软件和硬件的结合来实现。其中,硬件部分可以利用专用逻辑来实现;软件部分则可以存储在存储器中,由适当的指令执行系统,例如微处理器或者专用设计硬件来执行。本领域技术人员可以理解上述的方法和系统可以使用计算机可执行指令和/或包含在处理器控制代码中来实现,例如在诸如磁盘、cd或dvd-rom的载体介质、诸如只读存储器(固件)的可编程的存储器或者诸如光学或电子信号载体的数据载体上提供了这样的代码。本说明书的系统及其模块不仅可以有诸如超大规模集成电路或门阵列、诸如逻辑芯片、晶体管等的半导体、或者诸如现场可编程门阵列、可编程逻辑设备等的可编程硬件设备的硬件电路实现,也可以用例如由各种类型的处理器所执行的软件实现,还可以由上述硬件电路和软件的结合(例如,固件)来实现。88.需要注意的是,以上对于模块的描述,仅为描述方便,并不能把本说明书限制在所举实施例范围之内。可以理解,对于本领域的技术人员来说,在了解该系统的原理后,可能在不背离这一原理的情况下,对各个模块进行任意组合,或者构成子系统与其他模块连接。例如,各个模块可以共用一个存储模块,各个模块也可以分别具有各自的存储模块。诸如此类的变形,均在本说明书的保护范围之内。89.图9是根据本说明书一些实施例所示的数据处理系统的示例性功能框图。该数据处理系统可以基于现场可编程逻辑门阵列(field programmable gate array,fpga)芯片实现。如图9所示,待处理脉冲分别输入四个并联的比较器1-比较器4,比较器1-比较器4可以分别设定不同的阈值电压。比较器可以是lvds比较器。待处理脉冲分别输入到4个lvds比较器1-比较器4中,同时四个不同的阈值电压也输入至以上lvds比较器中。比较器1-比较器4可以分别实现阈值电压与待处理脉冲的比较。在本技术中,每个比较器可以输出一比较结果。该比较结果可以是状态变化信号。比较器所输出的比较结果可以输入至延迟模块中。延迟模块包括四个并联的延迟单元1-延迟单元4。各延迟单元可以对从比较器1-比较器4输入的状态变换信号进行延迟。在本技术中,每一个延迟单元可以输出一延迟状态变化信号。所有的延迟状态变化信号将被输入至信号通道控制器。信号通道控制器可以选择性的控制输入时间数字转换器的延迟状态变化信号。时间数字转换器可以对输入的延迟状态变化信号进行时间测量。90.本文已对基本概念做了描述,显然,对于本领域技术人员来说,上述详细披露仅仅作为示例,而并不构成对本说明书的限定。虽然此处并没有明确说明,本领域技术人员可能会对本说明书进行各种修改、改进和修正。该类修改、改进和修正在本说明书中被建议,所以该类修改、改进、修正仍属于本说明书示范实施例的精神和范围。91.同时,本说明书使用了特定词语来描述本说明书的实施例。如“一个实施例”、“一实施例”、和/或“一些实施例”意指与本说明书至少一个实施例相关的某一特征、结构或特点。因此,应强调并注意的是,本说明书中在不同位置两次或多次提及的“一实施例”或“一个实施例”或“一个替代性实施例”并不一定是指同一实施例。此外,本说明书的一个或多个实施例中的某些特征、结构或特点可以进行适当的组合。92.此外,本领域技术人员可以理解,本说明书的各方面可以通过若干具有可专利性的种类或情况进行说明和描述,包括任何新的和有用的工序、机器、产品或物质的组合,或对他们的任何新的和有用的改进。相应地,本说明书的各个方面可以完全由硬件执行、可以完全由软件(包括固件、常驻软件、微码等)执行、也可以由硬件和软件组合执行。以上硬件或软件均可被称为“数据块”、“模块”、“引擎”、“单元”、“组件”或“系统”。此外,本说明书的各方面可能表现为位于一个或多个计算机可读介质中的计算机产品,该产品包括计算机可读程序编码。93.计算机存储介质可能包含一个内含有计算机程序编码的传播数据信号,例如在基带上或作为载波的一部分。该传播信号可能有多种表现形式,包括电磁形式、光形式等,或合适的组合形式。计算机存储介质可以是除计算机可读存储介质之外的任何计算机可读介质,该介质可以通过连接至一个指令执行系统、装置或设备以实现通讯、传播或传输供使用的程序。位于计算机存储介质上的程序编码可以通过任何合适的介质进行传播,包括无线电、电缆、光纤电缆、rf、或类似介质,或任何上述介质的组合。94.本说明书各部分操作所需的计算机程序编码可以用任意一种或多种程序语言编写,包括面向对象编程语言如java、scala、smalltalk、eiffel、jade、emerald、c++、c#、vb.net、python等,常规程序化编程语言如c语言、visual basic、fortran 2003、perl、cobol 2002、php、abap,动态编程语言如python、ruby和groovy,或其他编程语言等。该程序编码可以完全在用户计算机上运行、或作为独立的软件包在用户计算机上运行、或部分在用户计算机上运行部分在远程计算机运行、或完全在远程计算机或服务器上运行。在后种情况下,远程计算机可以通过任何网络形式与用户计算机连接,比如局域网(lan)或广域网(wan),或连接至外部计算机(例如通过因特网),或在云计算环境中,或作为服务使用如软件即服务(saas)。95.此外,除非权利要求中明确说明,本说明书所述处理元素和序列的顺序、数字字母的使用、或其他名称的使用,并非用于限定本说明书流程和方法的顺序。尽管上述披露中通过各种示例讨论了一些目前认为有用的发明实施例,但应当理解的是,该类细节仅起到说明的目的,附加的权利要求并不仅限于披露的实施例,相反,权利要求旨在覆盖所有符合本说明书实施例实质和范围的修正和等价组合。例如,虽然以上所描述的系统组件可以通过硬件设备实现,但是也可以只通过软件的解决方案得以实现,如在现有的服务器或移动设备上安装所描述的系统。96.同理,应当注意的是,为了简化本说明书披露的表述,从而帮助对一个或多个发明实施例的理解,前文对本说明书实施例的描述中,有时会将多种特征归并至一个实施例、附图或对其的描述中。但是,这种披露方法并不意味着本说明书对象所需要的特征比权利要求中提及的特征多。实际上,实施例的特征要少于上述披露的单个实施例的全部特征。97.一些实施例中使用了描述成分、属性数量的数字,应当理解的是,此类用于实施例描述的数字,在一些示例中使用了修饰词“大约”、“近似”或“大体上”来修饰。除非另外说明,“大约”、“近似”或“大体上”表明所述数字允许有±20%的变化。相应地,在一些实施例中,说明书和权利要求中使用的数值参数均为近似值,该近似值根据个别实施例所需特点可以发生改变。在一些实施例中,数值参数应考虑规定的有效数位并采用一般位数保留的方法。尽管本说明书一些实施例中用于确认其范围广度的数值域和参数为近似值,在具体实施例中,此类数值的设定在可行范围内尽可能精确。98.针对本说明书引用的每个专利、专利申请、专利申请公开物和其他材料,如文章、书籍、说明书、出版物、文档等,特此将其全部内容并入本说明书作为参考。与本说明书内容不一致或产生冲突的申请历史文件除外,对本说明书权利要求最广范围有限制的文件(当前或之后附加于本说明书中的)也除外。需要说明的是,如果本说明书附属材料中的描述、定义、和/或术语的使用与本说明书所述内容有不一致或冲突的地方,以本说明书的描述、定义和/或术语的使用为准。99.最后,应当理解的是,本说明书中所述实施例仅用以说明本说明书实施例的原则。其他的变形也可能属于本说明书的范围。因此,作为示例而非限制,本说明书实施例的替代配置可视为与本说明书的教导一致。相应地,本说明书的实施例不仅限于本说明书明确介绍和描述的实施例。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150213.html

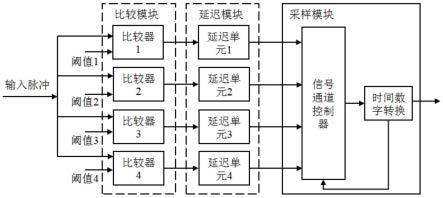

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。