基于片上存储的共享型阵列时间数字转换器

- 国知局

- 2024-07-30 09:41:21

1.本发明涉及一种基于片上存储的共享型阵列时间数字转换器,尤其应用于随阵列规模扩大,数据量激增的电路系统当中,属于时间数字转换器电路设计的技术领域。背景技术:2.时间数字转换器(time-to-digital converter,tdc)凭借低复杂度、宽动态范围、强鲁棒性等特点,广泛应用在三维智能感知、自主导航、工业检测、激光雷达、医用探测等现代热门领域,而多样化的应用场景则针对tdc的数据传输速度、功耗、面积等方面提出了更高要求。3.传统架构中的tdc内置于像素单元中,当触发海量有效光子事件时,一方面大部分像素单元都处于工作状态,消耗较大功耗,另一方面是大规模的数据吞吐量,需要增加相应的电路处理单元,高速传输与低功耗低面积消耗间的矛盾,限制了阵列tdc的大规模拓展。由于静态随机存取存储器(static random-access memory,sram)具有高速、低功耗的特性,且只要保持通电,储存的数据就可以恒常保持。所以本设计基于sram的优势,考虑进一步减小面积与功耗,提出基于片上存储的共享型阵列时间-数字转换器,以获取高速数据传输能力;其中,片上存储仅通过六个晶体管实现数据锁存。4.基于片上存储的共享型阵列tdc,在应对大规模数据传输时能拥有较好的性能,同时一定程度地降低功耗与面积,对阵列tdc大像素规模的进一步扩展具有重要意义。技术实现要素:5.技术问题:为了克服海量有效光子事件对阵列tdc大像素规模、性能与功耗的限制,本发明提供了一种基于片上存储的共享型阵列时间数字转换器,相比传统的阵列tdc结构,在保证帧频一致性的前提下,极大的降低了数据读出时间,以及整体面积消耗与平均功耗。6.技术方案:为实现上述目的,本发明提供了一种基于片上存储的共享型阵列时间-数字转换器,该阵列时间数字转换器包括内置sram单元与读写通路的宏像素电路、时序控制电路、同步信号电路、并转串数据接口电路;其中:7.时序控制电路产生的数据传输开始标志与结束标志接同步信号电路,时序控制电路产生的数据传输窗口信号接并转串数据接口电路,宏像素电路的像素阵列系统的输出端接并转串数据接口电路;全局信号包括使能信号en、复位信号reset、tdc高频时钟信号hck1、hck2通过对称h-tree型分布网络接入整个像素阵列系统的各个宏像素之中。8.所述宏像素电路,由静态随机存取存储器sram、存储器写入读出通路、4*4像素单元、两段式tdc共同构成像素阵列中的一个宏像素;每个像素单元包括淬灭电路和有限状态机;存储器写入通路包括仲裁电路、地址编码电路、数据锁存电路和延迟复位电路;存储器读出通路包括累加器、模12计数器;并串数据接口电路包括12位移位寄存器和多路选择器。9.所述的宏像素电路,在片上存储数据写入阶段,当使能信号en有效期间内检测到触发信号时,由两段式tdc完成时间间隔量化并锁存,有限状态机光子记录回波次数,并通过存储器写入通路判断保留最先到达的光子信号,写时钟到达后数据写入sram。10.所述的宏像素电路,在片上存储数据读出阶段,所述的时序控制电路通过在不同时间段对数据端口的控制,遍历sram中各存储单元的地址,并按地址顺序读出量化数据;同步信号电路产生与输出数据相对应的标志信号,保证数据读出的准确性,最后由移位寄存器完成数据的并串转换,并通过多路选择器对输出端口进行分时复用,将tdc量化数据按照顺序串行读出。11.所述的宏像素电路中,每个像素的有限状态机在检测到第一次光子事件后,在检测到dtof信号后将地址总线a《0》地址置1,确保所述a《0》地址变化不影响当前数据写入地址;所述的dtof信号,由存储器写入通路中的延迟复位电路,判断处理仲裁电路中保留的光子事件后产生;所述有限状态机通过q1信号表征当前检测到的回波次数,存储器写入通路的仲裁电路保留先到达的光子事件信息,判断小于5ns的两次光子事件为光子事件冲突,并舍弃后到达的光子事件。12.所述的存储器写入通路的仲裁电路,检测每个像素所述的req信号,由仲裁电路的decision maker模块两两比较,最终仲裁出最先到达的光子时间信号并输入至延迟复位电路,产生dtof和dtof_delay信号,同时所述存储器写入通路中的地址编码电路产生对应像素的地址,当两段式tdc锁存的数据检测到dtof_delay信号时,数据将统一接入到sram中。13.所述宏像素电路中,存储器读出通路通过一个5位同步计数器实现地址累加功能,遍历sram中各存储单元地址,在时序控制电路的协调下,12位移位寄存器和多路选择器分时复用,完成数据的并行读取和串行输出。14.所述宏像素电路中,存储器读出具体为:所述的时序控制电路由数据读出时钟lck驱动的计数器加上定时控制逻辑组成,通过在不同的时间段使能不同的控制信号,使得数据按照预先设定好的顺序统一有序读出;每当计数器计数到定时逻辑对应的一个计数值时,定时逻辑就会产生相应的窄脉冲信号驱动和复位对应的d触发器,形成相应的时间窗口区间,用来对应数据读出和处理,最终结果表现为所述lck信号分成八段使能处理,得到lck_and_tpi信号,依次对八个存储器进行控制;存储器读出电路中,当模12计数器产生的读信号clka拉高时,存储器中的数据更新至所述并转串数据接口电路中的多路选择器,模12计数器产生的另一个周期电平sel,用于控制所述并转串数据接口电路中的多路选择器,在检测到lck_and_tpi后,将存储器中的数据输送至并转串数据接口电路中的12位移位寄存器,传输结束后,所述12位移位寄存器进入移位模式,在时钟的驱动下将并行数据转化为串行数据输出。15.所述的同步信号电路主要提供对串行输出数据进行识别的标志信号,该电路主要产生与输出数据相对应的字信号word以及位信号bit三个同步信号,结合数据输出data_out,便于后续数据处理;位信号bit与字信号word的对应关系取决于要读出的数据的位数。16.所述的并转串数据接口电路接收到时序控制电路产生的数据传输窗口信号tpi后,通过和时钟lck信号进行与操作产生数据传输时钟信号lck_and_tpi,该信号在对应设定的数据传输窗口tpi脉宽高电平内有效,此时对应路径上的数据正常传输;而在数据传输窗口tpi脉宽高电平外低频时钟被屏蔽,数据传输被禁止;并转串数据接口电路在对应的lck_and_tpi信号的控制下完成数据的串行输出。17.有益效果:本发明提供的一种基于片上存储的共享型阵列时间数字转换器,与现有技术相比,具有如下技术效果:18.1.本发明应用于大规模数据存储与传输的tdc阵列电路当中,针对sram完成量化数据的存储与读取操作,在时序控制电路的协调下,并转串数据接口电路分时复用,按特定周期顺序串行输出数据。相对于传统方案中,tdc数据传输速率受功耗限制,且量化数据锁存在二十四个晶体管组成的寄存器内;本发明所述方案中,结合了sram高速数据传输能力、低功耗的特性,同时片上存储仅通过六个晶体管实现量化数据的锁存,因此与传统方案相比,在保证帧频、数据吞吐量一致性的前提下,本发明所述方案能极大的降低了数据读出时间,以及数据读出功耗。19.2.本发明应用于大规模数据存储与传输的tdc阵列电路当中,sram的写入与读出通路保证了数据传输的建立时间与保持时间,且sram只要保持通电,储存的数据就可以恒常保持,因此在一定程度增加了数据存储时间的长度,减少数据漏电丢失、建立保持时间不足的概率,提高数据处理的可靠性与准确性。同时基于片上存储的阵列tdc辅以共享结构,在面临多光子事件时,能自主仲裁并输出发生光子事件像素的地址,减少所使用的tdc数量,进一步降低数据读出功耗与面积消耗。附图说明20.图1为本发明提供的一种基于片上存储的共享型阵列时间-数字转换器的结构示意图;其中有:读出同步信号产生电路sync、时序控制电路timing control、同步信号电路、宏像素电路、并串数据接口电路;21.图2为宏像素中写入通路结构与时序图;22.图3为宏像素中读出通路结构图;23.图4为时序控制电路timing control结构图;24.图5为同步信号电路sync结构图;25.图6为并转串数据接口电路结构图;26.图7是读出通路的模12计数器电路结构图;27.图8是本发明的基于片上存储的共享型阵列时间-数字转换器的工作时序。具体实施方式28.下面结合附图对本发明作更进一步的说明。29.如图1所示,为本发明提供的一种基于片上存储的共享型阵列时间-数字转换器的结构示意图,整体电路包括内置sram单元与读写通路的宏像素电路、时序控制电路、同步信号电路、并转串数据接口电路;其中:30.时序控制电路产生的数据传输开始标志与结束标志接同步信号电路,时序控制电路产生的数据传输窗口信号接并转串数据接口电路,宏像素电路的像素阵列系统的输出端接并转串数据接口电路;全局信号包括使能信号en、复位信号reset、tdc高频时钟信号hck1、hck2通过对称h-tree型分布网络接入整个像素阵列系统的各个宏像素之中。所述宏像素电路,由静态随机存取存储器sram、存储器写入读出通路、4*4像素单元、两段式tdc共同构成像素阵列中的一个宏像素;每个像素单元包括淬灭电路和有限状态机;存储器写入通路包括仲裁电路、地址编码电路、数据锁存电路和延迟复位电路;存储器读出通路包括累加器、模12计数器;并串数据接口电路包括12位移位寄存器和多路选择器。31.其中:32行×32列像素阵列包括8个8行×16列像素阵列块,每个8行×16列像素阵列块由4个宏像素和并串转换电路组成,并串转换电路由12位移位寄存器和多路选择器构成。200mhz的lck信号由timing control产生,作为sync的输入产生不同的同步信号电路,重新交由timing control处理为32行×32列像素阵列的控制信号,同时全局信号包括使能信号en、复位信号reset、800mhz的tdc时钟由对称h-tree型分布网络接入整个阵列的各个像素之中。8行×16列像素阵列块中不同的单像素在检测到光子事件后,经由宏像素中的写入通路仲裁处理对应像素的地址,同时产生写入时钟,控制两段式tdc的量化数据写入静态随机存取存储器sram当中;当数据输出阶段时,宏像素中的读出通路在读时钟的控制下将数据从sram读取出来,由总线传输至并串转换电路,完成数据的顺序输出。32.本发明的基于片上存储的共享型阵列时间-数字转换器为:片上存储数据写入阶段,所述的宏像素电路中,在使能信号en有效期间内检测到触发信号时,由两段式tdc完成时间间隔量化并锁存数据,有限状态机记录光子回波次数,通过存储器写入通路判断保留最先到达的光子事件并将量化结果写入sram。在片上存储数据读出阶段,所述的时序控制电路通过在不同时间段对数据端口的控制,对sram中各存储单元的地址进行遍历,并按地址顺序读出量化数据;同步信号电路产生与输出数据相对应的标志信号,保证数据读出的准确性,最后通过所述的并转串数据接口电路,将tdc量化数据按照顺序串行读出。33.图2所示为宏像素中写入通路结构与时序图,单像素检测到光子事件后,decision maker模块对每两个reqi信号比较并锁存结果,仲裁出最先到达的光子信号,直至全部的reqi信号比较结束,输出qout信号作为写入时钟。为了保证仲裁结果的准确性,需要在每次仲裁完成之后对decision maker复位操作,同时产生dtof_delay信号,用于将图1中tdc锁存的数据统一接入到sram当中。34.图3宏像素中的读出通路的具体功能为:sel信号作为5位同步计数器的时钟,产生sram中存储单元的地址,按周期从地址中输出数据到12位移位寄存器当中,lck_and_tpi信号控制寄存器将数据输出传输至多路选择器,sel信号控制寄存器从sram中接受数据。具体工作过程为:clka信号有效时,将完成一次片上存储数据的更新与读取,当sel信号拉高时,lck_and_tpi信号通过多路选择器从存储器中读取一次数据,传输至12位移位寄存器,传输结束后,12位移位寄存器进入移位模式,在时钟的驱动下将并行数据转化为串行数据读出;所述的lck_and_tpi是图1中时序控制电路timing control所产生的,在由读出同步信号产生电路sync处理后重新输入时序控制电路timing control,对lck信号进行分段使能处理,分别得到lck_and_tp0~lck_and_tp7,依次对八个存储器进行控制。35.图4所示的时序控制电路timing control通过在不同的时间段使能不同的控制信号,使得数据按照预先设定好的顺序统一有序读出。时序控制电路由数据读出时钟lck驱动的计数器加上定时控制逻辑组成,采用二进制异步加法器对数据读出时钟lck周期进行计数,再利用定时逻辑产生相应的数据传输窗口tpi(i=0,1,2..n)对阵列进行行选控制,随后将tpi信号进一步处理,来驱动各像素子阵列中地址数据和tdc量化数据在对应tpi信号高电平脉宽内按照既定顺序读出。以8×8系统阵列为例,采用4路并行读出方式,将8×8阵列分为4个8×2的子阵列,每个子阵列共16个像素共用一个数据输出i/o口进行数据传输。而在每个8×2子阵列中,每行数据通过行选控制和并转串输出接口电路,将2行并行数据串行输出,并且此种读出方式总是会先读出靠近输出引脚的像素的数据。具体工作流程如下:每当计数器计数到定时逻辑对应的一个计数值时,定时逻辑就会产生相应的窄脉冲信号驱动和复位相应的d触发器,形成的时间窗口区间即为tp0~tp1、tp1~tp2…tp6~tp7。该计数值限制了系统的工作时间,系统在0~tp0区间内需完成电路复位、触发信号检测、计数等操作。时间窗口区间tp0~tp1和tp1~tp2分别为读出第一行地址信息和第一行tdc量化数据的时间窗口,tp1~tp2窗口区间完成一行像素中检测到触发信号的像素点数据传输操作。tp2~tp3和tp3~tp4的窗口区间分别和tp0~tp1、tp1~tp2相同,用来读出第二行像素的对应数据,其余窗口区间功能类似。frame信号用于标志帧内数据读出阶段,cenb信号标志写使能有效,cena信号标志读使能有效。36.图5为同步信号电路sync结构图,主要提供对串行输出数据进行识别的标志信号。该模块产生与输出数据相对应的字信号(word)以及位信号(bit)三个同步信号,结合数据输出(data_out),便于后续数据处理。其中,tp1与lck信号由时序控制模块提供,输出的bit信号由lck信号同步产生,bit与word的对应关系取决于要读出的数据的位数,通过双模计数器对输出的地址数据与tdc量化数据分别进行标记。37.图6为并转串数据接口模块,由移位寄存器和多路选择器组合,实现数据读出与串行输出的分时复用。其工作流程为:移位寄存器将sel信号拉高后,在lck_and_tpi驱动下从存储器中读取一次数据,随后sel信号转换为低电平,寄存器进入移位模式,将并行数据转化为串行数据读出。38.图7是读出通路的模12计数器电路结构图。模12计数器产生图3所需的clka和sel信号,其中clka信号用于从存储器中读取和更新数据,选择counter_6信号作为clka信号,用于更新从存储器中读出的数据,并配合sel信号将该数据写入移位寄存器当中;sel信号还用于对存储器地址进行累加,选用counter_12产生sel信号,则每当counter_12到来时,地址数据加一,每当counter_6到来时,进行数据读出。39.本发明的基于片上存储的共享型阵列时间-数字转换器,整体电路的工作时序如图8所展示,reset复位之后,在使能信号使能信号en的门控时间内,当触发了多光子事件reqi,由存储器写入通路仲裁多光子事件的间隔是否满足写入时间间隔的操作,进而保留满足要求的光子时间,并产生写时钟dtof,且地址信息被写入address bus中,量化数据databus被写入存储器中相应的存储单元中;完成量化后,写使能跳变为高电平,读时钟clka按固定周期工作,完成一次数据的读取操作和一次地址数据的更新操作,将数据通过图6的并转串数据接口模块串行输出数据。40.本发明的基于片上存储的共享型阵列时间-数字转换器与传统方案相比:(1)片上存储消耗的功耗低,且每个存储单元仅用六个晶体管实现数据锁存,同时共享结构减少了tdc数量,进一步降低了功耗与面积的消耗。(2)片上存储的数据传输速度较快,在同样数据吞吐量的前提下,有效降低了读出时间。(3)片上存储的写入与读出通路能够满足数据的建立时间与保持时间,在面对大规模数据传输时,能够降低数据写入或读出错误的概率。41.以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150507.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

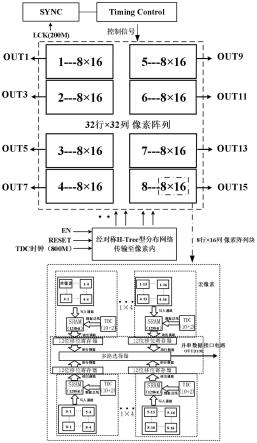

返回列表