一种数模混合的高精度建立保持时间测量电路及其实现方法与流程

- 国知局

- 2024-07-30 09:41:23

1.本发明涉及电路设计技术领域,特别是涉及一种数模混合的高精度建立保持时间测量电路及其实现方法。背景技术:2.在集成电路设计领域,setup/hold time特性对同步电路而言是一项非常重要的参数。在数字电路设计的过程中往往需要包含存储器,组合逻辑电路以及一些时序逻辑,为了保证各个部分在一起工作的时候能够稳定地配合实现设计好的功能,需要在设计的时候保证每一个模块的运行都符合建立时间与保持时间的要求。setup/hold time的性能在很大程度上限定了电路工作的最高频率。但是由于其数值非常之小,测试机的测量精度或者是测量路径上的一些差异就很容易导致测量结果的错误,所以很难测量。3.目前国内外有很多团队在对建立和保持时间特性进行研究,其测量电路的设计主要有两种方式:4.全模拟设计:是根据数据输入和时钟信号之间的时间关系进行判断;5.全数字设计:一般使用延迟锁定环(dll)生成设置时钟和保持时钟用来测试建立时间。6.上述两种方式的优缺点比较如下:7.模式优点缺点全模拟设计测量精度高工艺平台的可移植性较差全数字设计可移植性好测试精度相对较差8.时间测量电路的关键问题在于:最小测量单元很难做小并且保持均匀和稳定;存在系统误差会影响测量电路的准确性;校准电路的时钟周期需要稳定和准确。9.保证测量结果的准确性,需要通过设计专门的测试电路。10.当前也有人利用全数字的方法设计了的建立/保持时间(setup/hold time)测量电路,其提出了一种基于单元的电路方案去测量特定存储模块的建立/保持时间以及访问时间,对于建立/保持时间测量,其将问题建立了成一个逐次逼近的过程去逐渐接近最小建立时间和确保数据正确所需的最短保留时间并保证锁存驱动sram的输入信号;对于每个输出数据位,他们首先将其转换为脉冲宽度,然后将其用时间数字转换方式收缩脉冲时间将其转换为数字代码。该方法基于单元结构的时间-脉冲宽度转换器测量建立/保持时间(setup/hold time)测量电路,具有很高的分辨率,并用简单的结构使得传统的tdc记录了最坏情况下访问整个内建自测bist(built-in self test)的访问时间,此外,他们还提出了测量电路的校准方案,为了测量建立/保持时间,该方案还合并了一个基于环形振荡的结构。11.现有技术由于采用逐次逼近,测试速度比较慢。12.随着国内集成电路产业的兴起和高阶制程的不断发展,对电路的性能要求也不断提高,在这样的背景下,研究电路的建立/保持时间(setup/hold time)特性不论是对集成电路设计还是制造而言都具有一定的指导意义。技术实现要素:13.为克服上述现有技术存在的不足,本发明之目的在于提供一种数模混合的高精度建立保持时间测量电路及其实现方法,通过使用mos的栅极电容负载作为最小测量单元的延时,使用频率高且抖动小的pll锁相频率输出作为校准时钟源,实现了一种数模混合的高精度建立保持时间测量电路,校准范围覆盖整个测量电路。14.为达上述及其它目的,本发明提出一种数模混合的高精度建立和保持时间测量电路,包括:15.pll校准周期产生模块,用于产生校准时的标准时间延迟以便后续进行准确测试;16.模式选择电路,用于在校准控制信号cal的控制下选择校准状态和测试状态时延时模块的基准参考输入信号,以于校准时选择pll校准周期产生模块产生的上升沿作为延时模块的基准参考输入,而于测试时选择外部时钟clk作为延时模块的基准参考输入;17.延时模块,用于在粗调控制信号csel[5:0]与精调控制信号fsel[3:0]的控制下在测试和校准时产生具有特定延迟的第一动态信号outa和第二动态信号outb,并于测试时经多重校准环节模块传输至sram模块作为sram模块的数据输入和时钟clk输入,而于校准时经多重校准环节模块传输至输出端口进行输出和记录系统误差;[0018]多重校准环节模块,用于在校准时在信道选择信号sel_ch[3:0]和路径选择信号path的控制下使pll校准周期产生模块产生的第一至第二校准信号output1~output2经过延时模块延时后在sram模块的输入端口前通过校准d触发器进行检测输出,从而将系统误差更加精确地排除,而于测试时在信道选择信号sel_ch[3:0]和路径选择信号path的控制下将延时模块产生的第一动态信号outa、第二动态信号outb以及地址addr[3:0]、输入数据di[3:0]、写入控制信号we、读出控制信号me和外部时钟clk传输至sram模块的输入端口以完成指定操作,并记录数据变化以获得完成指定操作时某信号的建立/保持时间;以及[0019]sram模块。[0020]优选地,所述pll校准周期产生模块通过利用锁相环产生一个稳定的频率信号,然后通过d触发器组成的电路取到两个时间差为一个pll周期的上升沿用于后续较准使用。[0021]优选地,所述pll校准周期产生模块包括锁相环、除法器和第一至第三d触发器,锁相环复位信号reset_pll连接至所述锁相环的锁相环复位端,复位信号reset连接至第一至第三d触发器的复位端,第一分频数m_pll[1:0]、第二分频数n_pll和锁相环参考频率clk_pll连接至所述锁相环的相应输入端,所述锁相环的一路输出经分频器分频后作为锁相频率输出pll_out连接至外部仪器,锁相环的另一路输出连接至d触发器dff1~3的第一数据输入端,第一d触发器的第二数据输入端接高电平,第一d触发器的输出连接至第二d触发器的第二数据输入端,第二d触发器的输出即第一校准信号output1连接至第三d触发器的第二数据输入端,第三d触发器的输出即第二校准信号output2,第一校准信号output1和第二校准信号output2连接至所述模式选择电路的第一和第二数据输入端。[0022]优选地,外部时钟clk连接至所述模式选择电路的第三数据输入端,校准控制信号cal连接至所述模式选择电路的控制输入端,所述模式选择电路的输出端连接至所述延时模块的基准参考输入端。[0023]优选地,粗调控制信号csel[5:0]与精调控制信号fsel[3:0]分别连接至所述延时模块的粗调控制输入端和精调控制输入端,所述延时模块输出的具有特定延迟的第一动态信号outa和第二动态信号outb连接至所述多重校准环节模块第一选择模块的数据输入端,路径选择信号path连接至所述第一选择模块的控制输入端。[0024]优选地,所述多重校准环节模块包括第一选择模块、第二选择模块和第四至第八校准d触发器,路径选择信号path连接至第一选择模块的控制输入端,第一选择模块的第一输出和第二输出连接至第二选择模块的第一和第二数据输入端,地址addr[3:0]、输入数据di[3:0]、写入控制信号we、读出控制信号me和外部时钟clk连接至第二选择模块的第三和第七数据输入端,信道选择信号sel_ch[3:0]连接至第二选择模块的控制输入端,第二选择模块的第一至第五输出端分别连接至sram模块的数据输入和时钟clk输入端,经第二选择模块选择后,所述第一选择模块的第一输出和第二输出之一连接所述sram模块的时钟clk输入端clk1,而另一则连接sram模块的addr/di/we/me之一;第一动态信号outa和第二动态信号outb连接至第四校准d触发器的数据输入端,时钟clk输入端clk1连接至第五至第八校准d触发器的第一数据输入端,信号addr1[3:0]、di1[3:0]、we1、me1分别连接至第五至第八校准d触发器的第二数据输入端,第四至第八校准d触发器的输出q_cap[2:0]连接至外部仪器。[0025]优选地,所述延时模块包括多个延时单元、多个缓冲器和多个多路选择器,粗调控制信号csel[5:0]经译码后连接至多路选择器的控制端,多个延时单元依次级联,所述模式选择电路的一路输出作为第一延时单元的输入,上一延时单元的输出作为下一延时单元的输入,每个延时单元的输出还连接缓冲器的输入端,多个缓冲器的输出两两组合作为第一级多路选择器的输入,第一级多路选择器的输出再两两组合作为下一级多路选择器的输入端,…,直至得到一路输出信号即第一动态信号outa,所述模式选择电路的另一路经处理后作为第二动态信号outb。[0026]优选地,每个延时单元包含精调电路,所述精调电路包括两个反相器、多个选择开关和多个mos电容,精调控制信号fsel[3:0]经译码后连接至选择开关的控制端即栅极,两个反相器级联连接,选择开关一端即mos开关管的源极接反相器的输出端和另一反相器的输入端,选择开关另一端即mos开关管的漏极接mos电容的一端即栅极,mos电容的另一端即源极和漏极接地。[0027]为达到上述目的,本发明还提供一种数模混合的高精度建立保持时间测量电路的实现方法,包括如下步骤:[0028]步骤s1,在校准过程中,将pll校准周期产生模块以精准的参考频率clk_pll为基准,采用锁相环pll的锁相频率输出作为精准的时钟源,设置第一分频数m_pll和第二分频数n_pll使其工作在特定频率下,待锁相环pll电路工作稳定后通过d触发器组合取到其中的两个相邻周期的上升沿作为第一校准信号和第二校准信号作为整个测试电路系统校准的时差基准;[0029]步骤s2,通过设置粗调控制信号csel和精调控制信号fsel将延时模块调整到特定的档位后,在不同的输出位置点通过多重较准环节的校准d触发器输出端口即可检验到变化的信号响应,记录此时的档位和时钟即参考频率clk_pll的频率值;[0030]步骤s3,调整第一分频数m_pll和第二分频数n_pll的设置产生两组不同的pll频率,组成的二元一次方程组即可获得延时模块的单位延迟时间。[0031]优选地,所述方法还包括:[0032]在测试过程中,关闭pll校准周期产生模块的信号输出端口,选择外部时钟clk作为延时模块的基准参考时钟;[0033]外部时钟clk在经过延时模块前被模式选择电路分成相同的两路信号,通过设置粗调控制信号csel和精调控制信号fsel设定延时模块的档位即可将一路参考时钟产生一个特定的时延以与另一路参考时钟产生特定的时间差;[0034]将两个具有特定时间差的参考时钟通过所述多重较准环节的第一选择模块和第二选择模块输入到sram模块的输入端,其一连接addr/di/we/me其中一个,另一信号则连接sram模块的时钟clk信号输入端口,当其中两个端口由这两路输入时,其他端口的输入信号通过外部设置正常输入;[0035]调整所述延时模块的延时时间,通过观察sram模块的输出端口q的输出信号是否发生变化即可获得其建立和保持时间。[0036]与现有技术相比,本发明一种数模混合的高精度建立保持时间测量电路及其实现方法,通过使用mos的栅极电容负载作为最小测量单元的延时,使用频率高且抖动小的pll锁相频率输出作为校准时钟源,实现了一种数模混合的高精度建立保持时间测量电路,校准范围覆盖整个测量电路,本发明经流片验证芯片各项功能正常,能够进行校准和测量。附图说明[0037]图1为本发明一种数模混合的高精度建立和保持时间测量电路的电路结构图;[0038]图2为本发明具体实施例中pll校准周期产生模块(pcpm)10的结构示意图;[0039]图3为本发明具体实施例中延时模块的粗调电路的电路结构图;[0040]图4为本发明具体实施例中精调电路的电路结构图;[0041]图5为本发明一种数模混合的高精度建立保持时间测量电路的实现方法的步骤流程图。具体实施方式[0042]以下通过特定的具体实例并结合附图说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其它优点与功效。本发明亦可通过其它不同的具体实例加以施行或应用,本说明书中的各项细节亦可基于不同观点与应用,在不背离本发明的精神下进行各种修饰与变更。[0043]图1为本发明一种数模混合的高精度建立和保持时间测量电路的电路结构图。如图1所示,本发明一种数模混合的高精度建立和保持时间测量电路,包括pll校准周期产生模块(pcpm)10、模式选择电路(mode)20、延时模块(delay module)30、多重校准环节模块40和sram模块50。[0044]其中,pll校准周期产生模块(pcpm)10,用于产生校准时的标准时间延迟以便于后续进行准确测试,其原理主要是使用pll产生一个稳定的频率信号,然后通过d触发器组成的电路取到两个时间差为一个pll周期的上升沿即output1和output2的上升沿用于后续较准使用;模式选择电路(mode)20,用于在校准控制信号cal的控制下选择校准状态和测试状态时延时模块(delay module)30的基准参考输入信号,以于校准时选择pll校准周期产生模块(pcpm)10产生的上升沿作为延时模块(delay module)30的基准参考输入,而于测试时选择外部时钟clk作为延时模块(delay module)30的基准参考输入;延时模块(delay module)30为整个测试电路中最为核心的模块,其设计也最为精确,用于粗调控制信号csel[5:0]与精调控制信号fsel[3:0]的控制下在测试和校准时产生具有特定延迟的第一动态信号outa和第二动态信号outb,并于测试时经多重校准环节模块40传输至sram模块50作为sram模块50的数据输入和时钟clk输入,而于校准时经多重校准环节模块40传输至输出端口进行输出和记录系统误差,其精度直接决定了整个测试电路设计的绝大部分精度;多重校准环节模块40由第一选择模块mcm1、第二选择模块mcm2和多个校准d触发器dff4~8组成,其需要pll校准周期产生模块(pcpm)10与延时模块(delay module)30结合并与sram模块50配合在一起才能发挥作用,用于在校准时在信道选择信号sel_ch[3:0]和路径选择信号path的控制下使pll校准周期产生模块(pcpm)10产生的第一至第二校准信号output1~output2经过延时模块(delay module)30延时后在sram模块50的输入端口前通过校准d触发器dff4~8进行检测输出,从而将系统误差更加精确地排除,而于测试时在信道选择信号sel_ch[3:0]和路径选择信号path的控制下将延时模块(delay module)30产生的第一动态信号outa、第二动态信号outb以及地址addr[3:0]、输入数据di[3:0]、写入控制信号we、读出控制信号me和外部时钟clk传输至sram模块50的输入端口以完成指定操作,并记录数据变化以获得完成指定操作时某信号的建立/保持时间(setup/hold time);sram模块50为待测设备,使用已有的电路设计,用于执行指定操作,在测试时,通过设置各控制信号将已校准好的其他模块的输出信号输出到sram模块50的相应端口,在sram模块50的输出端口观测信号变化情况即可以判断输入的信号是否满足最小建立时间和保持时间的要求。[0045]锁相环复位信号reset_pll连接至pll校准周期产生模块(pcpm)10的锁相环复位端和校准d触发器dff4的复位端,复位信号reset连接至pll校准周期产生模块(pcpm)10的复位端,第一分频数m_pll[1:0]、第二分频数n_pll和锁相环参考频率clk_pll连接至pll校准周期产生模块(pcpm)10的相应输入端,pll校准周期产生模块(pcpm)10的锁相频率输出端pll_out连接外部仪器,pll校准周期产生模块(pcpm)10输出的第一校准信号output1和第二校准信号output2连接至模式选择电路(mode)20的第一和第二数据输入端;[0046]外部时钟clk连接至模式选择电路(mode)20的第三数据输入端,校准控制信号cal连接至模式选择电路(mode)20的控制输入端,模式选择电路(mode)20的输出端连接至延时模块(delay module)30的基准参考输入端;[0047]粗调控制信号csel[5:0]与精调控制信号fsel[3:0]分别连接至延时模块(delay module)30的粗调控制输入端和精调控制输入端,延时模块(delay module)30输出的具有特定延迟的第一动态信号outa和第二动态信号outb连接至第一选择模块mcm1的数据输入端,路径选择信号path连接至第一选择模块mcm1的控制输入端,第一选择模块mcm1的第一输出outa1和第二输出outb1连接至第二选择模块mcm2的第一和第二数据输入端;[0048]地址addr[3:0]、输入数据di[3:0]、写入控制信号we、读出控制信号me和外部时钟clk连接至第二选择模块mcm2的第三和第七数据输入端,信道选择信号sel_ch[3:0]连接至第二选择模块mcm2的控制输入端,第二选择模块mcm2的第一至第五输出端分别连接至sram模块50的数据输入和时钟clk输入端,特别地,经第二选择模块mcm2选择后,第一输出outa1和第二输出outb1之一连接sram模块50的时钟clk输入端clk1,而另一则连接sram模块50的addr/di/we/me之一即addr1[3:0]、di1[3:0]、we1、me1之一;[0049]第一动态信号outa和第二动态信号outb还连接至校准d触发器dff4的数据输入端,时钟clk输入端clk1还连接至校准d触发器dff5~8的第一数据输入端,addr1[3:0]、di1[3:0]、we1、me1分别连接至校准d触发器dff5~8的第二数据输入端,校准d触发器dff4~8的输出q_cap[2:0]连接至外部仪器,不失一般性,addr1[3:0]、di1[3:0]选取某一位进行测试即可;[0050]测试控制信号test1连接至sram模块50的控制端,sram模块50的输出q[3:0]连接至外部仪器。[0051]图2为本发明具体实施例中pll校准周期产生模块(pcpm)10的结构示意图。在本发明具体实施例中,pll校准周期产生模块(pcpm)10由锁相环pll、除法器和多个d触发器dff1~3组成,锁相环复位信号reset_pll连接至锁相环pll的锁相环复位端,复位信号reset连接至d触发器dff1~3的复位端,第一分频数m_pll[1:0]、第二分频数n_pll和锁相环参考频率clk_pll连接至锁相环pll的相应输入端,锁相环pll的一路输出经64分频器(64devider)分频后作为锁相频率输出pll_out连接至外部仪器,锁相环pll的另一路输出连接至d触发器dff1~3的第一数据输入端,d触发器dff1的第二数据输入端接高电平“1”,d触发器dff1的输出连接至d触发器dff2的第二数据输入端,d触发器dff2的输出即第一校准信号output1连接至d触发器dff3的第二数据输入端,d触发器dff3的输出即第二校准信号output2,第一校准信号output1和第二校准信号output2连接至模式选择电路(mode)20的第一和第二数据输入端;[0052]图3为本发明具体实施例中延时模块的电路结构图。如图3所示,延时模块为包括粗调电路,该粗调电路由多个延时单元dl1~dlnc、多个缓冲器buf1~bufnc和多个多路选择器mu1~munm组成,粗调控制信号csel[5:0]经译码后连接至多路选择器mu1~munm的控制端,多个延时单元依次级联,模式选择电路(mode)20的一路输出作为第一延时单元的输入,上一延时单元的输出作为下一延时单元的输入,每个延时单元的输出还连接缓冲器的输入端,多个缓冲器的输出两两组合作为第一级多路选择器的输入,第一级多路选择器的输出再两两组合作为下一级多路选择器的输入端,……,直至得到一路输出信号即第一动态信号outa,模式选择电路(mode)20的另一路经处理(可以仅缓冲输出或某一固定延时后输出)后作为第二动态信号outb;[0053]在本发明具体实施例中,每个延时单元的精调电路结构相同,如图4所示精调电路由两个反相器invc1-invc2、多个选择开关pcf和多个mos电容ccf组成,c为1至nc,nc为延时单元个数,f为1至nf,nf为精调电容个数,精调控制信号fsel[3:0]经译码后连接至选择开关pcf的控制端即栅极,两个反相器级联连接,选择开关一端即mos开关管的源极接第一反相器的输出端和第二反相器的输入端,选择开关另一端即mos开关管的漏极接mos电容的一端即栅极,mos电容的另一端即源极和漏极接地。[0054]在整个系统中各个模块互相配合完成自身系统的校准功能和实现精确测量的目的。[0055]在整个电路的工作过程中(校准状态),pll校准周期产生模块(pcpm)10以精准的参考频率clk_pll为基准,采用锁相环pll的锁相频率输出作为精准的时钟源,设置第一分频数m_pll和第二分频数n_pll使其工作在特定频率下,待锁相环pll电路工作稳定后通过d触发器dff1~3组合取到其中的两个相邻周期的上升沿作为第一校准信号output1和第二校准信号output2作为整个测试电路系统校准的时差基准。通过设置粗调控制信号csel和精调控制信号fsel将延时模块(delay module)30调整到特定的档位后,在不同的输出位置点通过多重较准环节40的校准d触发器dff4~8输出端口即可检验到变化的信号响应,记录此时的档位和时钟即参考频率clk_pll的频率值。调整第一分频数m_pll和第二分频数n_pll的设置产生两组不同的pll频率,组成的二元一次方程组即可获得延时模块的单位延迟时间。[0056]在实际进行测试的时候(测试状态),关闭pll校准周期产生模块(pcpm)10的信号输出端口,选择外部时钟clk作为延时模块(delay module)30的基准参考时钟。外部时钟clk在经过延时模块(delay module)30前被模式选择电路(mode)20分成相同的两路信号,通过设置粗调控制信号csel和精调控制信号fsel设定延时模块(delay module)30的档位即可将一路参考时钟产生一个特定的时延以与另一路参考时钟产生特定的时间差,然后将两个具有特定时间差的参考时钟通过第一选择模块mcm1和第二选择模块mcm2输入到sram模块50的输入端,其一连接addr/di/we/me其中一个,另一信号则连接sram模块50的时钟clk信号输入端口,当其中两个端口由这两路输入时,其他端口的输入信号通过外部设置正常输入。调整延时模块(delay module)30的延时时间,通过观察sram模块50的输出端口q的输出信号是否发生变化即可获得其建立和保持时间。[0057]本发明经流片验证芯片各项功能正常,并能够进行校准和测量;pcpm模块嵌入的pll频率测量准确,校准过程实测的精调和粗调档位与仿真值接近;延时模块专门设计的精调结构单元测量精度达到5ps,超过了原10ps的设计目标;本发明的测量电路可以对100ps左右的sram建立时间进行准确测量,并且与仿真值接近。[0058]图5为本发明一种数模混合的高精度建立保持时间测量电路的实现方法的步骤流程图。如图5所示,本发明一种数模混合的高精度建立保持时间测量电路的实现方法,包括如下步骤:[0059]步骤s1,在整个电路的工作过程中(校准状态),将pll校准周期产生模块(pcpm)以精准的参考频率clk_pll为基准,采用锁相环pll的锁相频率输出作为精准的时钟源,设置第一分频数m_pll和第二分频数n_pll使其工作在特定频率下,待锁相环pll电路工作稳定后通过d触发器dff1~3组合取到其中的两个相邻周期的上升沿作为第一校准信号output1和第二校准信号output2作为整个测试电路系统校准的时差基准。[0060]步骤s2,通过设置粗调控制信号csel和精调控制信号fsel将延时模块(delay module)30调整到特定的档位后,在不同的输出位置点通过多重较准环节的校准d触发器dff4~8输出端口即可检验到变化的信号响应,记录此时的档位和时钟即参考频率clk_pll的频率值。[0061]步骤s3,调整第一分频数m_pll和第二分频数n_pll的设置产生两组不同的pll频率,组成的二元一次方程组即可获得延时模块的单位延迟时间。[0062]优选地,本发明一种数模混合的高精度建立保持时间测量电路的实现方法。还包括:[0063]在实际进行测试的时候(测试状态),关闭pll校准周期产生模块(pcpm)的信号输出端口,选择外部时钟clk作为延时模块(delay module)的基准参考时钟;[0064]外部时钟clk在经过延时模块(delay module)前被模式选择电路(mode)分成相同的两路信号,通过设置粗调控制信号csel和精调控制信号fsel设定延时模块(delay module)的档位即可将一路参考时钟产生一个特定的时延以与另一路参考时钟产生特定的时间差;[0065]将两个具有特定时间差的参考时钟通过第一选择模块mcm1和第二选择模块mcm2输入到sram模块的输入端,其一连接addr/di/we/me其中一个,另一信号则连接sram模块的时钟clk信号输入端口,当其中两个端口由这两路输入时,其他端口的输入信号通过外部设置正常输入;[0066]调整延时模块(delay module)的延时时间,通过观察sram模块的输出端口q的输出信号是否发生变化即可获得其建立和保持时间。[0067]上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修饰与改变。因此,本发明的权利保护范围,应如权利要求书所列。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150509.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

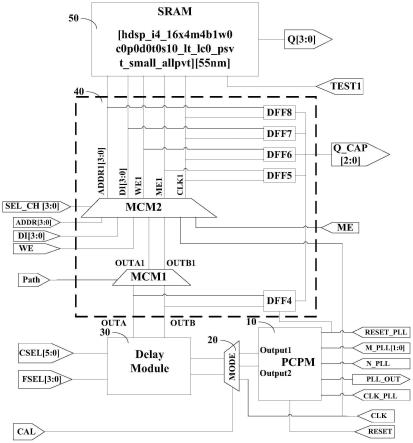

返回列表