分段式时间数字转换器、控制方法、介质、设备及终端

- 国知局

- 2024-07-30 10:13:35

本发明属于时间间隔测量,尤其涉及一种分段式时间数字转换器、控制方法、介质、设备及终端。

背景技术:

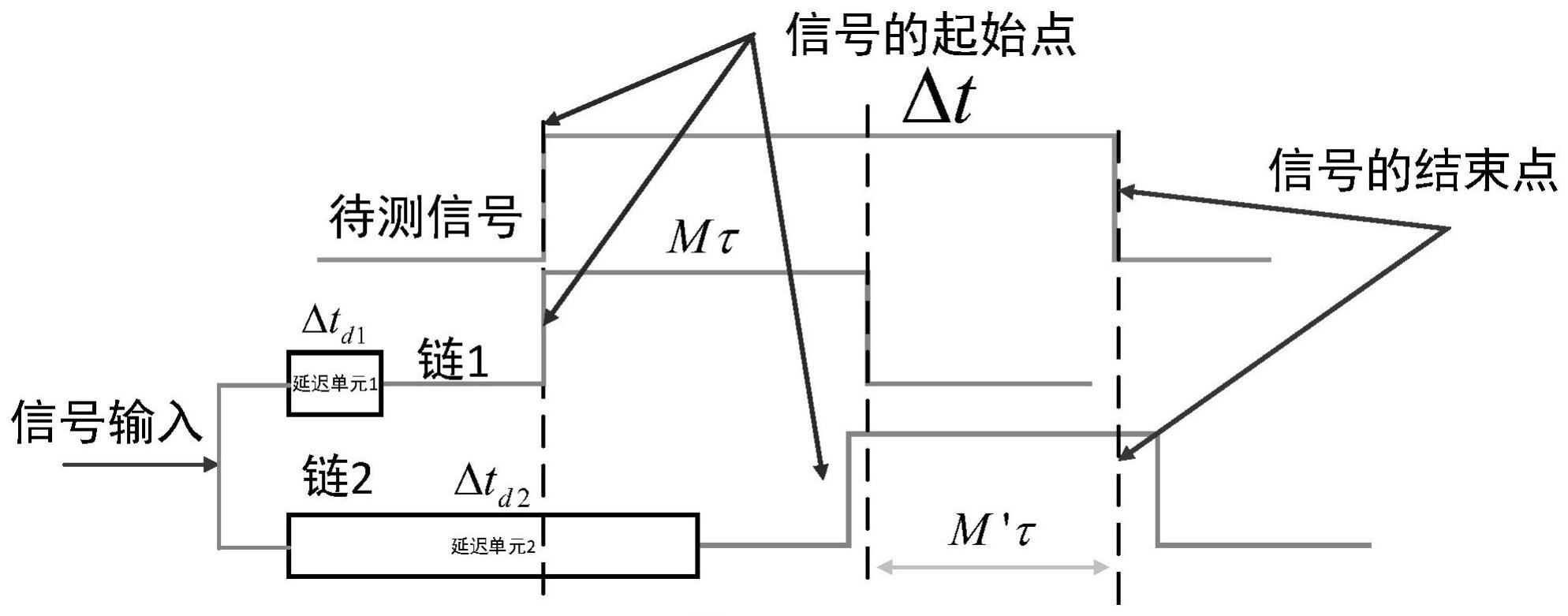

1、目前,时间数字转换器(time to digital converter,tdc)是一种高精度(皮秒级)的时间间隔测量单元,广泛应用于众多工业应用领域,包括核物理、汽车车辆、医学成像等。简单的tdc可以利用高频时钟信号,通过计算经历的时钟数量来粗略的刻画时间间隔,然而这种方法的分辨率受到时钟频率的限制,通常在纳秒级。

2、现有的tdc方案可分为模拟方案和数字方案。模拟方案,包括时间拉伸或时间-幅度转换。这些模拟方案一方面在实现中需要使用模拟量,而模拟量易受信号波动的影响;另一方面,这些方案的单次测量时间往往远高于待测时间间隔,即较长的转换率,这就导致死时间过长,无法进行高频次的测量。因此,尽管它们可以实现可观的积分非线性(integrated non-linearity,inl)性能,甚至亚皮秒的时间分辨率,但它们并不太常见。相反,数字方案更加流行,因为它们可以更快地部署和迭代(在fpga上),具有更加紧凑的硬件结构,灵活性好,更能忍受噪声干扰。因此,数字tdc解决方案更受欢迎。

3、第一个数字解决方案是插值方法,也称为nutt方法。插值方法利用多个延迟单元(在fpga中通常为进位模块)对系统时钟进行内插。在该方法中,一系列延迟单元级串联在一起,形成一个长链(也称为抽头延迟线,tapped delay line,tdl),它们的测量结果往往称为“细”时间。在nutt方法中,先用系统时钟对待测时间间隔进行粗略的测量,将待测时间分为整数个时钟分量和小数个时钟分量。整数时钟分量利用计数法可以得到,而小数个时钟分量则利用tdl链中延迟单元被触发的数量来得到。在该方法中,可以事先通过码密度测量得到tdl链中每个延迟单元所能造成的延迟时间,而这些单元的触发数量通过测量可以得到,因此“细”时间的值便可以得到,再配合由系统时钟得到的“粗”时间的值,即能得到最终的时间间隔。

4、该方法的前提是每个延迟单元具有相同的延迟,这一延迟也决定了测量的时间分辨率。然而,这些延迟单元的特性容易受到器件固有缺陷、功率和温度动态变化等的影响,导致了严重的非线性问题。同时,每个单元的固有延迟是由其制造工艺决定的,不能够被修改。因此,一旦确定了硬件平台,就已经确定了tdc的时间分辨率。为了解决这些问题,已经提出了游标方法、多链平均拓扑、waveunion架构和bin-to-bin校准等方法。

5、尽管这些方法能够提升tdc某些方面的性能,但它们往往会引入其它问题。例如,游标方法可以极大地缓解设备本身存在的非线性缺陷,提高时间分辨率,甚至超过延迟单元固有的时间延迟,但游标法需要更多的逻辑资源和更长的转换率。多链平均拓扑不会提高死时间,但相比游标方法,会占用更多的资源。waveunion方法虽然节约资源,但是需要复杂的环形振荡器设计,其性能取决于延迟单元之间的不均匀性。然而,随着半导体制造工艺的提升,这种不均匀性时下已经不严重了。bin-to-bin校准方法只能缓解延迟单元的非线性问题,而且其扩展性较差,当改变通道位置或者更换硬件平台时,都需要进行重新处理。

6、使用应用专用集成电路(application-specific integrated circuit,asic)的tdc设计可以显著地解决上述问题。虽然这些面向asic的解决方案通常能实现令人满意的性能,但它们一方面要求较高的制造成本和较长的设计周期,因此技术迭代慢,发展速度受到了极大的限制;另一方面,它们不能重复使用,导致灵活性较差。因此,只有经验和资源丰富的团体才有实力选择基于asic的解决方案。这种现象在某种程度上可能会抑制创新的步伐,因此许多tdc的设计往往首先使用fpga进行验证,再采用asci进行批量流片。

7、传统的tdc往往将延迟单元以一条直线的方式串在一起。如以fpga为平台实现的tdc为例,基于fpga的tdc是通过fpga的进位单位作为延时单位串成一串。为了保证tdc链上的资源能够完整的对系统时钟进行“内插”,要求整条延迟链产生的固有延迟大于计数器的时钟周期,这一必要条件往往称为时钟条件。而整个延迟链产生的延迟由每一个延时单元的固有延迟以及总的延迟单元的数量决定,因此在计数器时钟固定的情况下,当延时单元的精度很高时,就需要保证延迟单元的数量很多,也就会导致传统的单链tdc在fpga上串得很长,这也就会带来以下技术问题:

8、(1)线性度差。理想的tdc要求每一个延时单元之间的传递延时都要相同,以保证高的线性度。然而,实际中只有在同一个资源块内的延迟单元能保证良好的一致性;在不同的资源块间的延迟单元由于布线资源的差异性较大,导致了严重的非线性问题。

9、(2)误差大。当tdc链长过长,会导致“气泡”的问题,即当一个信号经过一条链时,理论上其经历过的所有延迟单元都会被触发,即输出应该全为“1”(或相反“0”),然而当链长较长时,全为“1”的触发段中可能会存在许多“0”,这将严重干扰tdc的测量结果。

10、(3)鲁棒性差。延迟单元的固有延迟时间受温度的影响变化较大,当温度变化较大时,不仅会影响链中延迟单元的线性度,且会使其固有延迟整体发生偏移,给测量带来误差。

11、通过上述分析,现有技术存在的问题及缺陷为:

12、(1)现有的tdc模拟方案在实现中需要使用模拟量,而模拟量易受信号波动的影响;同时,现有的tdc模拟方案的单次测量时间往往远高于待测时间间隔,即较长的转换率,这将导致死时间过长,无法进行高频次的测量。

13、(2)现有的游标法需要更多的逻辑资源和更长的转换率,多链平均拓扑会占用更多的资源;waveunion方法需要复杂的环形振荡器设计,性能取决于延迟单元之间的不均匀性;bin-to-bin校准方法只能缓解延迟单元的非线性问题,且扩展性较差,当改变通道位置或者更换硬件平台时需要进行重新处理。

14、(3)现有的tdc数字方案中,延迟单元的特性容易受到器件固有缺陷、功率和温度动态变化等的影响,导致了严重的非线性问题;同时,每个延迟单元的固有延迟是由其制造工艺决定的,不能够被修改。

15、(4)现有面向asic的解决方案要求较高的制造成本和较长的设计周期,技术迭代慢,发展速度受到极大限制;不能重复使用,导致灵活性较差,抑制创新步伐;而传统的tdc存在线性度差、误差大以及鲁棒性差的问题。

技术实现思路

1、针对现有技术存在的问题,本发明提供了一种分段式时间数字转换器、控制方法、介质、设备及终端。

2、本发明是这样实现的,一种分段式时间数字转换器的控制方法,分段式时间数字转换器的控制方法包括:改变延迟链的结构,利用多条短的并形链对tdl tdc中待测信号的“细”时间进行测量;通过对各条短链前引入不同固定的延迟处理,以使各条短链本质上对待测信号的不同区间进行并形测量的目的。

3、进一步,链长个数依据时钟条件以及每条链的测量区间确定。

4、进一步,分段式时间数字转换器的控制方法还包括:

5、利用多条并形短链对待测信号进行“细”时间测量中,链1与待测信号相接,链1与链2前面均连接延迟单元,用于产生固定的延迟时间,其中链2前延迟单元配置的延迟时间δtd2长于链1中延迟单元造成的延迟时间δtd1,δtd2>δtd1。

6、进一步,链前面的延迟单元与链中的延迟单元是两个不同的逻辑资源;

7、其中,链前的延迟单元是软件配置的单个或多个延迟单元,在xilinx fpga中是idelay资源;而链中的延迟单元则采用carry4/8资源。

8、进一步,链1的测量范围mτ与两条链前延迟单元产生的延迟时间满足条件mτ>δtd2-δtd1,其中m为延迟单元的个数,τ为每个延迟单元固定的延迟时间。链2的测量范围与链1相同,链1和链2的合计测量时间为2mτ,满足时钟条件2mτ>t。

9、进一步,当时间间隔为δt的信号输入时,若δt<mτ,则任何一条链均能完成对待测量信号的测量,则仅对链上被触发的延迟单元的个数进行计数,当数量为n时,则待测信号为δt=nτ;若待测时间间隔t>δt>=mτ,则利用两条链配合完成测量过程,其中t为系统时钟。由第一条链测量mτ部分,而另一条链的测量结果为m'τ,则最终的测量结果为(m+m')τ-(mτ-(δtd2-δtd1))=m'τ+(δtd2-δtd1);当δt>t时,分为两个部分进行测量,一部分为系统时钟的整数部分,另一部分为系统时钟的小数部分;整数部分通过计数功能实现,而小数部分则利用多个并形短链进行测量。

10、本发明的另一目的在于提供一种应用所述的分段式时间数字转换器的控制方法的分段式时间数字转换器,分段式时间数字转换器包括多条短链以及短链前连接的延迟单元,延迟单元用于产生固定的延迟时间;利用多条短链对tdl tdc中待测信号的“细”时间进行测量;通过对各条短链前引入不同固定的延迟处理,以使各条短链本质上对待测信号的不同区间进行并形测量的目的。

11、本发明的另一目的在于提供一种计算机设备,计算机设备包括存储器和处理器,存储器存储有计算机程序,计算机程序被处理器执行时,使得处理器执行所述的分段式时间数字转换器的控制方法的步骤。

12、本发明的另一目的在于提供一种计算机可读存储介质,存储有计算机程序,计算机程序被处理器执行时,使得处理器执行所述的分段式时间数字转换器的控制方法的步骤。

13、本发明的另一目的在于提供一种信息数据处理终端,信息数据处理终端用于实现所述的分段式时间数字转换器。

14、结合上述的技术方案和解决的技术问题,本发明所要保护的技术方案所具备的优点及积极效果为:

15、第一,针对上述现有技术存在的技术问题以及解决该问题的难度,紧密结合本发明的所要保护的技术方案以及研发过程中结果和数据等,详细、深刻地分析本发明技术方案如何解决的技术问题,解决问题之后带来的一些具备创造性的技术效果。具体描述如下:

16、1.线性度好。本发明提出的分段式时间数字转换器的控制方法将整条长链通过“折叠”的方式,巧妙地将所有的延迟单元都放在一个逻辑块中,这就完全避免了由于跨多个资源块所引入的线长不一致而导致的非线性问题。

17、2.结构简单,资源利用率高。本发明的分段式时间数字转换器结构简单,只需要固定的延迟单元和多条放在一个逻辑资源块的短链构成,其中固定的延迟单元由于链长较短,布局上可以更紧凑,其所浪费的布局空间更少。相反,长链资源本身就稀少,当将长链布局在有限的空间中时,未被利用的部分可能无法再次布下一条长链。这与计算机系统中的内存分配相似,长链等价于大块地址连续的空闲区,而短链则等价于分布于不同空间的小片段内存。大块地址连续内存是众所周知的稀缺资源,它是非常有限的,而小片的空闲内存则较多,若能利用这些小片内存组成大块的空闲内存,资源利用率必定会更高。

18、3.鲁棒性好,对器件和通道的变化不敏感,可在线更正温度引入的漂移。器件在制造过程中,空间位置相近的资源,其相似度更好,即一致性较好,当器件改变或通道改变时,这一性质仍然成立。那么,本发明基于空间位置相近的资源建立的tdc,其每个延迟单元的时间延迟的一致性也较好,当器件或通道发生变化时,这些延迟单元的一致性并不会被破坏,因而本发明提出的tdc的鲁棒性更好。另外,本发明中需要可配置延迟时间的逻辑资源,如在xilinx fpga中的idelay,它们往往对温度变化不敏感,利用这些不敏感的资源,配合多条短链,可以构成差分测量单元;再配合已知时间的脉冲信号(在fpga中可以通过pll非常容易提供),可以测量得到在不同温度条件下,延迟单元被触发的个数,这样就能求出不同温度条件下,单个延迟单元的固有延迟时间,进而对温度产生的影响进行补偿。

19、第二,把技术方案看做一个整体或者从产品的角度,本发明所要保护的技术方案具备的技术效果和优点,具体描述如下:

20、(1)技术效果:通过tdc在码密度测试中的实验效果可知,本发明提出的分段式时间数字转换器结构,其inl与dnl要明显优于传统的结构;且inl与dnl均低于0.5lsb,但传统方案高达1.5lsb;inl与dnl越小,则线性度越好,性能越优。

21、(2)技术优点:tdc作为一种时间测量工具,需要保证测量的准确性,而影响其准确性的因素主要包括自身的分辨率以及线性度,本发明具有的高线性度能够有效提高tdc测量的准确性。

22、第三,作为本发明的权利要求的创造性辅助证据,还体现在以下几个重要方面:

23、(1)本发明的技术方案填补了国内外业内技术空白:传统的时间数字转换器线性度差、鲁棒性差、结构复杂、资源利用率低。为了解决线性度以及时间分辨率的问题,要么需要引入更多的资源,使得资源利用率低,结构的复杂度也提升;要么需要花费大量的工作进行校准,使得鲁棒性极差。尽管性能上有提升,这些额外的代价往往使人忘而却步,尤其是在多通道的场景下,很难推广。而本发明提供的分段式时间数字转换器则填补了现有技术的空白。

24、(2)本发明的技术方案解决了人们一直渴望解决、但始终未能获得成功的技术难题:现在有方法一直想解决tdc中的非线性问题,然而为了解决非线性问题却又引入了过多的时间成本或者资源成本,而本发明所提出的tdc结构,能够在不消耗更多资源的条件下,无需校准(即不需要额外的时间成本与计算成本),即可完美地解决非线性问题。

本文地址:https://www.jishuxx.com/zhuanli/20240730/151945.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。