一种基于FPGA与TDC芯片的高精度时差测量系统的制作方法

- 国知局

- 2024-07-30 10:14:19

本发明涉及时差测量系统,具体涉及一种基于fpga与tdc芯片的高精度时差测量系统。

背景技术:

1、fpga具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用,其包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块ram,布线资源,内嵌专用硬核,底层内嵌功能单元。

2、tdc是internet explorer提供的内置数据源控件,提供访问有定界符文本文件的能力,拥有datasrc、fielddelim、textquqlifier、rowdelim、sort、filter和useheader等属性及reset方法,并可通过tdc对象的id.recordset.{properties|method},访问相应的recordset集的属性和方法。

3、公开(公告)号:cn104656056a,公开(公告)日:2015-05-27,公开了一种时差测量系统的改进,提供一种灵活性强、速度快且可实现提取通过不同路径的同一信号时间差的一种时差测量系统。本发明包括主控制器、以太网接口、输入模块、串并转换接口、调试模块、电源、时差测算模块、输出模块、测算模块、定位模块,其特征在于:输入模块通过串并联接口与主控制器相连,主控制器还与调试模块、电源、以太网接口和时差测算模块相连;时差测算模块还与输出模块、测算模块和定位模块相连。

4、公开(公告)号:cn103869156b,公开(公告)日:2016-04-20,公开了一种双混频时差测量方法及测量系统。本发明通过选取一个不间断的公共源信号,由两个计数器分别实时获取该公共源信号的时间计数值,在参考信号和被测信号的上升沿分别到来时,分别获取当前两个计数器的时间计数值,使参考信号和被测信号的上升沿个数对齐,并使与对齐个数相对应的两个时间计数值相减,即可得出准确的时差值,根据该准确的时差值可计算出其他的频差、相差和阿伦方差等。本发明这种采用公共源信号的方式,可解决传统异或门方式在沿重叠或两个沿时差小于硬件响应时间时不能进行准确测量的问题,即解决了双混频时差测量过程中常存在的周期模糊现象。总之,采用本发明可以实现低成本、快速、准确、实时、无限制地进行测量。

5、在包括上述两个专利的现有技术中,其主要应用于测量领域,用于对检测过程中,数据的发送和接收的周期进行计时。其检测过程中容易受到电路板运行过程中电流引起电磁干扰,从而大大增加了时间的误差值,降低检测计时的精准度。

技术实现思路

1、本发明的目的是提供一种基于fpga与tdc芯片的高精度时差测量系统,

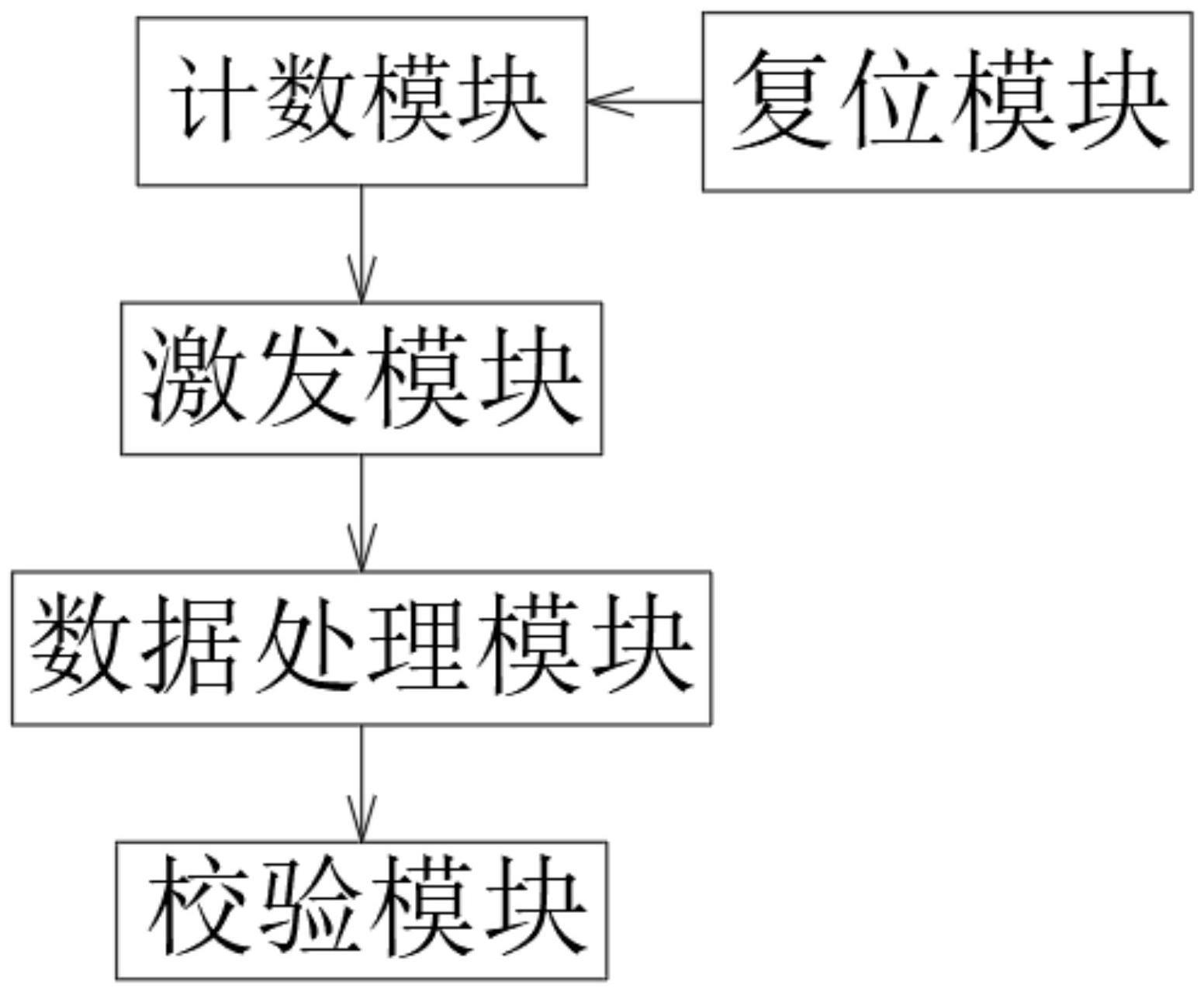

2、为了实现上述目的,本发明提供如下技术方案:一种基于fpga与tdc芯片的高精度时差测量系统,包括:

3、计数模块,基于tdc芯片接收超声波的电信号并检测超声波的传输时间形成反馈信息,至fpga逻辑控制芯片进行处理;

4、激发模块,在发送所述电信号的时,会同时发出至少一第一低频电信号和第二低频电信号,且基于两个低频电信号生成相同周期、相同延时的第一高频电信号和第二高频电信号;

5、数据处理模块,用于获取第一高频电信号和第二高频电信号的相位差,并将该相位差数据转化数字信号;

6、校验模块,所述fpga逻辑控制芯片接收所述数字信号并与所述反馈信息进行对比,以获得最小化误差的时差。

7、作为优选的,还包括复位模块,用于对所述fpga逻辑控制芯片以及tdc芯片计算运行数据进行清理,且最近一次接收的所述数字信号保留以与新传入的所述反馈信息进行校准。

8、作为优选的,所述第一低频电信号发射的电路包括电光转换器、含延时t光纤延迟线的波分复用光链路、光电转换器、输出下支路加入了δτ延时的电功率分配器和微波异或门。

9、作为优选的,所述第二低频电信号发射的电路包括电光转换器、含延时t+t2光纤延迟线的波分复用光链路、光电转换器、输出下支路加入δτ延时的电功率分配器和微波异或门。

10、作为优选的,所述数据处理模块基于所述反馈信息和相位差以获得第一低频电信号和第二低频电信号、第一高频电信号和第二高频电信号的时间差,其公式如下:

11、

12、其中:counter*tc为整数倍计数时钟周期的时差,为不足一计数时钟周期的时差,p为相位差,tc为tdc芯片数据清理的周期。

13、作为优选的,所述fpga逻辑控制芯片分别接收第一低频电信号和第二低频电信号、第一高频电信号和第二高频电信号的中间时间差形成计算间隔时间,1s作为一个长度单位,计算个数counter。

14、作为优选的,所述高频电信号的电路包括环形振荡器、分频器和带通滤波器,而环形振荡器的门电路的延时值为δτ。

15、在上述技术方案中,本发明提供的一种基于fpga与tdc芯片的高精度时差测量系统,具备以下有益效果:利用fpga芯片和tdc芯片相结合对电路中的高频电信号进行处理,以保证接收低频电信号的状态,保证了从发起到接收这段时间内计时的快速响应,使得获取的数据更加精确。

技术特征:1.一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,包括:

2.根据权利要求1所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,还包括复位模块,用于对所述fpga逻辑控制芯片以及tdc芯片计算运行数据进行清理,且最近一次接收的所述数字信号保留以与新传入的所述反馈信息进行校准。

3.根据权利要求1所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,所述第一低频电信号发射的电路包括电光转换器、含延时t光纤延迟线的波分复用光链路、光电转换器、输出下支路加入了δτ延时的电功率分配器和微波异或门。

4.根据权利要求1所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,所述第二低频电信号发射的电路包括电光转换器、含延时t+t2光纤延迟线的波分复用光链路、光电转换器、输出下支路加入δτ延时的电功率分配器和微波异或门。

5.根据权利要求1所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,所述数据处理模块基于所述反馈信息和相位差以获得第一低频电信号和第二低频电信号、第一高频电信号和第二高频电信号的时间差,其公式如下:

6.根据权利要求5所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,所述fpga逻辑控制芯片分别接收第一低频电信号和第二低频电信号、第一高频电信号和第二高频电信号的中间时间差形成计算间隔时间,1s作为一个长度单位,计算个数counter。

7.根据权利要求1所述的一种基于fpga与tdc芯片的高精度时差测量系统,其特征在于,所述高频电信号的电路包括环形振荡器、分频器和带通滤波器,而环形振荡器的门电路的延时值为δτ。

8.一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现权利要求1至7任一项所述基于fpga与tdc芯片的高精度时差测量系统的步骤。

9.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该计算机程序被处理器执行时实现权利要求1至7任一项所述基于fpga与tdc芯片的高精度时差测量系统的步骤。

技术总结本发明公开了一种基于FPGA与TDC芯片的高精度时差测量系统,包括:计数模块,基于TDC芯片接收超声波的电信号并检测超声波的传输时间形成反馈信息,至FPGA逻辑控制芯片进行处理;激发模块,在发送电信号的时,会同时发出至少一第一低频电信号和第二低频电信号,且基于两个低频电信号生成相同周期、相同延时的第一高频电信号和第二高频电信号;数据处理模块,用于获取第一高频电信号和第二高频电信号的相位差,并将该相位差数据转化数字信号;校验模块,FPGA逻辑控制芯片接收数字信号并与反馈信息进行对比。本发明提供的基于FPGA与TDC芯片的高精度时差测量系统,保证了从发起到接收这段时间内计时的快速响应,使得获取的数据更加精确。技术研发人员:李志强,于永受保护的技术使用者:南京天际易达通信技术有限公司技术研发日:技术公布日:2024/1/14本文地址:https://www.jishuxx.com/zhuanli/20240730/151981.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表