二进制随机时间到数字转换器及方法与流程

- 国知局

- 2024-07-30 10:21:36

本公开概括而言涉及用于将时间转换到数字值的方法和装置,更具体而言涉及用于将两个信号之间的时间差确定为数字值的方法和装置。

背景技术:

1、时间到数字转换器(time-to-digital converter,tdc)被用在大多数数字锁相环体系结构中来量化两个信号之间的相位距离,这两个信号是高频本地振荡器信号(通常由压控振荡器(voltage controlled oscillator,vco)产生)和较低频的参考时钟信号(几乎总是来自基于晶体的振荡器的信号)。转换器中的量化误差向该过程中引入与量化误差成正比的噪声。最小化量化误差对于获得较低的带内相位噪声是重要的。关于此的一个良好的经验法则是量化分辨率应当低于参考(ref)时钟信号的近载波相位噪声电平。另一方面,量化器(或tdc)应当具有充分大的动态范围,该动态范围在最低要求vco输出频率下应当延长到大于一个周期(当然是在任何过程和任何环境变动上)。

2、在业界由于其相对简单性而被采用的一种简单方案是对闪速tdc(flash-tdc)的使用,其利用数目上等于量化电平的数目的若干个采样元件。对于具有大动态范围和精细分辨率(这是遵守未来无线无线电标准所要求的)的系统,要求一大套组的采样元件。从器件占据的大芯片面积到器件的高峰值功率消耗剖面不等的大量设计问题经常根源于对大套组的使用。这种大采样套组器件由于其功率消耗而产生电流尖峰。电流尖峰尤其难以容适和掩蔽,例如难以限制尖峰在供电电压中引入重大变化。正是由于该原因,tdc采样操作的特征在整个集成电路各处都被以烦扰发送链和接收链两者的杂散信号的形式明显感受到。

3、在文献中已经给出了增大采样套组的大小以获得增大的动态范围的两种替换方案。第一种方案实现了元件再利用的想法,将tdc的线性延迟线变成环——因此其名称是环状tdc((r)ing-tdc)。环状tdc就定时方案和解码机制而言设计起来是尤其麻烦的,再加上其具有更高的1/f噪声内容,但环状tdc确实允许了就采样套组大小而言的相当大的节省。第二种方案引入了相位预测的想法,就此而言,vco信号的边缘通过预测被局部化并且被与参考信号的经适当延迟的复本并置。然而此方案对于预测质量是敏感的并且要求麻烦的校准从而抵消掉每个tdc固有的集成非线性。

技术实现思路

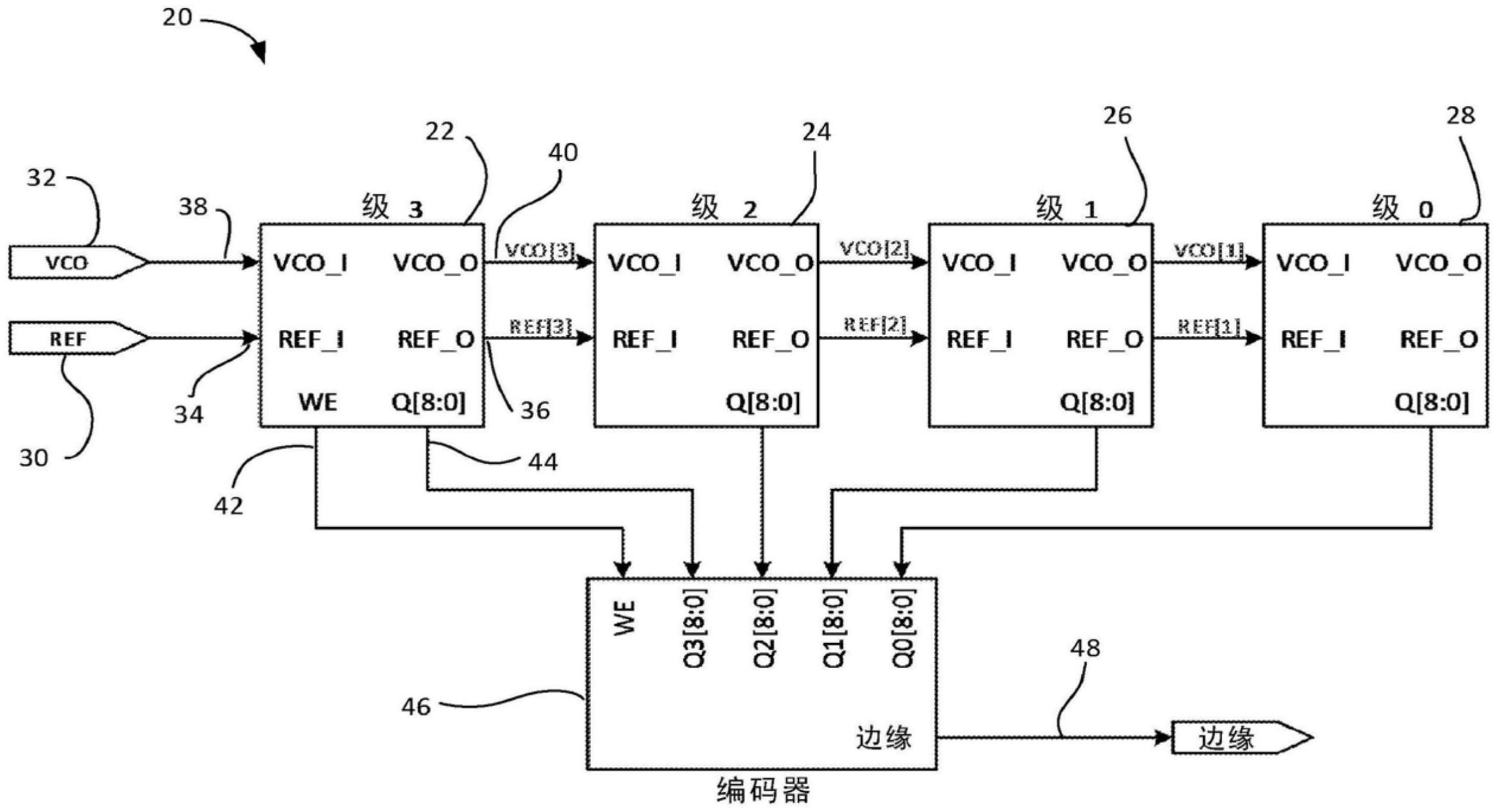

技术特征:1.一种时间到数字转换器tdc,包括多个采样级,每个采样级包括:

2.根据权利要求1所述的tdc,其中每个采样级包括:

3.根据权利要求2所述的tdc,其中所述多个采样元件包括多个d触发器。

4.根据权利要求2所述的tdc,其中当所述采样元件的输出不等同时,后续采样级被禁用。

5.根据权利要求2所述的tdc,还包括耦合在所述参考输入与所述第一参考复用器输入之间、耦合在所述参考输入与所述第二参考复用器输入之间、耦合在所述样本输入与所述第一样本复用器输入之间以及耦合在所述样本输入与所述第二样本复用器输入之间的相应第三延迟元件,所述相应第三延迟元件施加至少与所述多个采样元件的稳定时间一样长的延迟。

6.根据权利要求1所述的tdc,其中相应样本级中的相应第一延迟元件和第二延迟元件施加连续减小的信号延迟。

7.根据权利要求6所述的tdc,其中由第一样本级中的第一延迟元件和第二延迟元件施加的延迟是由第二样本级中的第一延迟元件和第二延迟元件施加的延迟的两倍。

8.根据权利要求1所述的tdc,还包括耦合到所述tdc的所述样本输入的错误边缘检测电路装置,所述错误边缘检测电路装置被配置为:基于在所述样本输入的信号中检测到的边缘类型与预定边缘类型之间的比较,生成错误边缘信号。

9.一种时间到数字转换器tdc,包括:

10.根据权利要求9所述的tdc,其中每个采样级包括:

11.根据权利要求10所述的tdc,其中相应样本级中的相应第一延迟元件和第二延迟元件施加连续减小的信号延迟。

12.根据权利要求11所述的tdc,其中由第一样本级中的第一延迟元件和第二延迟元件施加的延迟是由第二样本级中的第一延迟元件和第二延迟元件施加的延迟的两倍。

13.根据权利要求9所述的tdc,其中每个采样级包括多个采样元件,每个采样元件生成采样元件输出比特,其中与采样级中的每个采样元件的输出相对应的一组比特被输入到所述编码器。

14.根据权利要求13所述的tdc,其中所述多个采样元件包括多个d触发器。

15.根据权利要求13所述的tdc,其中当所述采样元件的输出不等同时,后续采样级被禁用。

16.一种时间到数字转换器tdc,包括:

17.根据权利要求16所述的tdc,其中所述多个采样元件包括多个d触发器。

18.根据权利要求16所述的tdc,还包括耦合在所述参考输入与所述第一参考复用器输入之间、耦合在所述参考输入与所述第二参考复用器输入之间、耦合在所述样本输入与所述第一样本复用器输入之间以及耦合在所述样本输入与所述第二样本复用器输入之间的相应第三延迟元件,相应延迟元件施加至少与所述多个采样元件的稳定时间一样长的延迟。

19.根据权利要求16所述的tdc,其中相应样本级中的相应第一延迟元件和第二延迟元件施加连续减小的信号延迟。

20.根据权利要求4所述的tdc,其中由第一样本级中的第一延迟元件和第二延迟元件施加的延迟是由第二样本级中的第一延迟元件和第二延迟元件施加的延迟的两倍。

21.根据权利要求16所述的tdc,还包括耦合到所述tdc的样本输入的错误边缘检测电路装置,所述错误边缘检测电路装置被配置为:基于在所述样本输入的信号中检测到的边缘类型与预定边缘类型之间的比较,生成错误边缘信号。

22.根据权利要求16所述的tdc,其中当所述采样元件的输出不等同时,后续采样级被禁用。

技术总结一种用于确定两个信号中的信号边缘之间的差异的方法和装置包括多级转换器,其中每一级确定两个信号中的哪个信号具有更早的信号边缘,输出与该确定相对应的值,并随后向更早的信号施加等于由前一级施加的延迟的一半的延迟。这些级考查到所寻求的信号边缘的越来越小的间隔。每一级包括多个逻辑元件。如果级中的所有逻辑元件都输出相同信号,则边缘位置是清楚的。如果级中的一些逻辑元件的选票由于不同元件的设立时间的差异而不同于该级中的其他逻辑元件,则已在该级的感测带内找到边缘位置。技术研发人员:罗腾·巴宁,阿萨夫·本-巴萨特,叶夫根尼·休梅克,奥菲尔·德刚尼受保护的技术使用者:苹果公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240730/152414.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表