一种误码纠正型时间-数字转换器

- 国知局

- 2024-07-30 10:30:44

本发明属于数字集成电路设计领域,特别涉及一种误码纠正型时间-数字转换器。

背景技术:

1、激光探测与测距(light detection and ranging,lidar)系统简称激光雷达。它是一种新型的主动探测式传感器,通过测定传感器与目标物体之间的传播距离,分析目标物体表面的反射能量大小、反射波谱的幅度、频率和相位等信息,从而呈现出目标物体精确的三维空间信息,近些年已然在军事、航天、民用等领域得到了广泛应用。时间-数字转换器(time-to-digital converter,tdc)作为激光雷达芯片中用来实现测距功能的主要模块,其分辨率(精度)在很大程度上决定了测距的精度,目前在飞行时间测量、数据转换器以及锁相环等领域具有广泛的应用。

2、为了提高时间-数字转换器的时间分辨率,前人提出了子门延迟分辨型时间-数字转换器以突破单个门延迟的极限,在分辨率上取得了较大改善,目前的实现方法主要可分为两大类:一类是基于时间放大(time amplifier,ta)原理,另一类就是基于游标(vernier)原理的电路架构。

3、为了满足各类场景下激光雷达的系统级应用,一般要求时间-数字转换器(time-to-di gital converter,tdc)具有高动态范围、高时间分辨率、高集成度及低功耗等特性,为了满足这些需求,单一模式的时间-数字转换器难以同时兼顾相互制约的分辨率和量程指标要求,因此分步式/分段式时间-数字转换器架构应运而生。如果系统架构为多段式,一般存在着多个计数器相配合,在整个量化过程中实现高、中段量化的功能。

4、由于时间-数字转换器电路中广泛使用了触发器、逻辑门等基本元件,考虑到实际信号传播过程中的延迟、触发器的建立-保持时间约束、时钟偏斜等问题,经常会由于传播路径延迟以及非理想时钟问题,造成计数器的误码以及多段式时间-数字转换器不同量化阶段之间的衔接误码,这些误码问题会严重影响到时间-数字转换器的线性度,造成错误的时间量化并影响了测距系统性能。

5、在过去,对于该问题通常可以根据码值的特征采用后端的校准进行误码消除;或者对于不同量化阶段量程和分辨率的相关性,采用一些较为简单的误码消除方案(例如采用两组计数器分别对同一个时钟进行上、下边沿计数,最后通过细量化阶段的相位译码信息决定输出某一组计数器数据),但是对于多端式架构,相邻量化阶段之间的量化关系已经不再清晰,因此需要新的误码检测纠正方案来避免衔接误码的情况出现。

技术实现思路

1、本发明针对多段式时间-数字转换器(time-to-digital converter,tdc)在不同量化通道切换时,由于触发器亚稳态、路径不匹配导致的信号传输延迟等电路非理想因素,导致的时间-数字转换器量化输出衔接误码问题,本发明通过前端电路校准技术,在极小电路功耗、面积等代价下解决了多段式量化系统的误码问题。

2、本发明的技术方案如下:

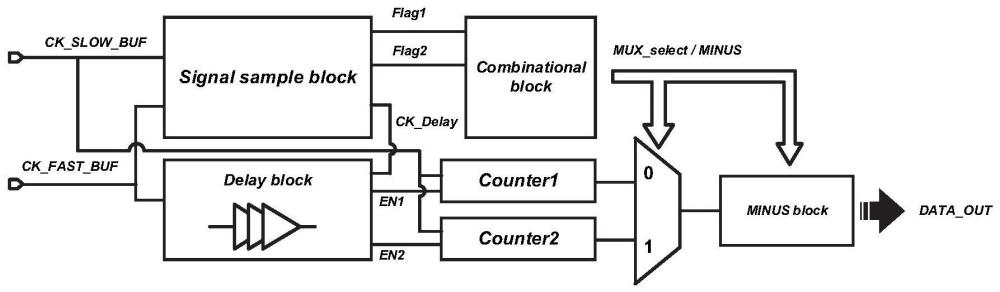

3、本发明误码纠正电路包括以下几个部分:信号采样模块;组合逻辑模块;信号延迟模块;计数器组模块;数据选择模块;数据减法模块。

4、误码纠正电路的关键信号和模块间逻辑关系如下:

5、信号采样模块输入外部输入的两个时钟(ck_slow_buf/ck_fast_buf),以及信号延迟模块产生的ck_delay,该模块输出两个数字逻辑标志信号(flag1,flag2),并将其输入至级联的组合逻辑模块。

6、组合逻辑模块接收信号采样模块的标志位输入,并分别输出标志位信号(mux_sele ct和minus)到数据选择模块和数据减法模块。

7、信号延迟模块输入了外部时钟ck_fast_buf,它产生的ck_delay输入到信号采样模块,同时产生的两个使能信号(en1,en2)输入到计数器组模块;

8、计数器组模块的输入时钟信号是ck_slow_buf,还输入了两个计数器使能信号(en1,en2),两路输出数据输入到数据选择模块。

9、数据选择模块的输入端是计数器组模块的两组数据输出,它还有一个使能输入端口是组合逻辑模块的输出mux_select。

10、数据减法模块的输入是数据选择模块的输出,还有一个来自组合逻辑模块的信号mi nus输入到数据减法模块。

11、最终整个误码纠正模块的输出是数据减法模块的输出。

12、本发明提出了一种误码修正机制,通过特定的组合逻辑和延迟双采样的电路设计,解决了多段式时间-数字转换器段间的衔接误码问题,通过本发明可以提高时间-数字转换器的系统的线性度,且本发明的主要优势有:

13、(1)解决了系统的衔接误码问题,提高了系统线性度。

14、(2)通过前端电路设计实现,不需要后端校准。

15、(3)功耗低,整体模块占用面积小。

技术特征:1.一种误码纠正型时间-数字转换器,其特征在于包括以下几个部分:信号采样模块,组合逻辑模块,信号延迟模块,计数器组模块,数据选择模块,数据减法模块,信号采样模块与组合逻辑模块、信号延迟模块相连接;信号延迟模块的输出和计数器组模块相连接;组合逻辑模块的输出和数据选择模块、数据减法模块相连接;计数器组模块的输出与数据选择模块相连接;数据选择模块的输出和数据减法模块相连接。

2.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,信号采样模块输入外部输入的两个时钟(ck_slow_buf/ck_fast_buf),以及信号延迟模块产生的ck_delay,该模块输出两个数字逻辑标志信号(flag1,flag2),并将其输入至级联的组合逻辑模块。

3.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,组合逻辑模块接收信号采样模块的标志位输入,并分别输出标志位信号(mux_select和minus)到数据选择模块和数据减法模块。

4.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,信号延迟模块输入了外部时钟ck_fast_buf,它产生的ck_delay输入到信号采样模块,同时产生的两个使能信号(en1,en2)输入到计数器组模块。

5.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,计数器组模块的输入时钟信号是ck_slow_buf,还输入了两个计数器使能信号(en1,en2),两路输出数据输入到数据选择模块。

6.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,数据选择模块的输入端是计数器组模块的两组数据输出,它还有一个使能输入端口是组合逻辑模块的输出mux_select。

7.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,数据减法模块的输入是数据选择模块的输出,还有一个来自组合逻辑模块的信号minus输入到数据减法模块。

8.根据权利要求1所述的一种误码纠正型时间-数字转换器,其特征在于,最终整个误码纠正模块的输出是数据减法模块的输出。

9.根据权利要求5所述的一种误码纠正型时间-数字转换器,其特征在于,计数器组模块的输出经过锁存后再输入到数据选择模块。

技术总结本发明公开了一种误码纠正型时间‑数字转换器,它包括:信号采样模块,组合逻辑模块,信号延迟模块,计数器组模块,数据选择模块,数据减法模块。本发明的电路将双采样与所设计的组合逻辑相配合,在没有较大面积开销和功耗的情况下,能够解决因实际电路传输延迟等非理想特性所导致的时间‑数字转换器段间误码问题,相比于传统的高精度时间‑数字转换器,提高了电路系统的可靠性和稳定性。技术研发人员:张冰,王晗,辛有泽受保护的技术使用者:西安交通大学技术研发日:技术公布日:2024/3/31本文地址:https://www.jishuxx.com/zhuanli/20240730/153139.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表