一种地址线优化方法、装置、设备及存储介质与流程

- 国知局

- 2024-07-31 22:41:54

本发明涉及电路设计,具体而言,涉及一种地址线优化方法、装置、设备及存储介质。

背景技术:

1、随着人工智能、物联网和大数据等领域的快速发展,对于更大容量和更高速度的存储需求也在不断增长,各种主控芯片挂载的存储芯片数量也越来越多,存储芯片的数量增加意味着设备可以处理更多的数据,提高了数据传输和处理的效率。

2、目前多片存储芯片大多数采用菊花链(fly-by)拓扑结构进行摆放,为了避免地址线过长导致的信号质量差的问题,常规的多片fly-by拓扑结构存储芯片通常沿着fly-by结构路径进行分段等长设计。但是分段等长设计会使主控芯片到每个存储芯片的地址线间的误差逐渐增加,最终使主控芯片到最后一片存储芯片的地址线间误差变得很大,可能会导致信号在主控芯片和存储芯片间传输过程中出现延迟。

技术实现思路

1、本发明解决的问题是如何提高主控芯片和存储芯片间信号传输的稳定性。

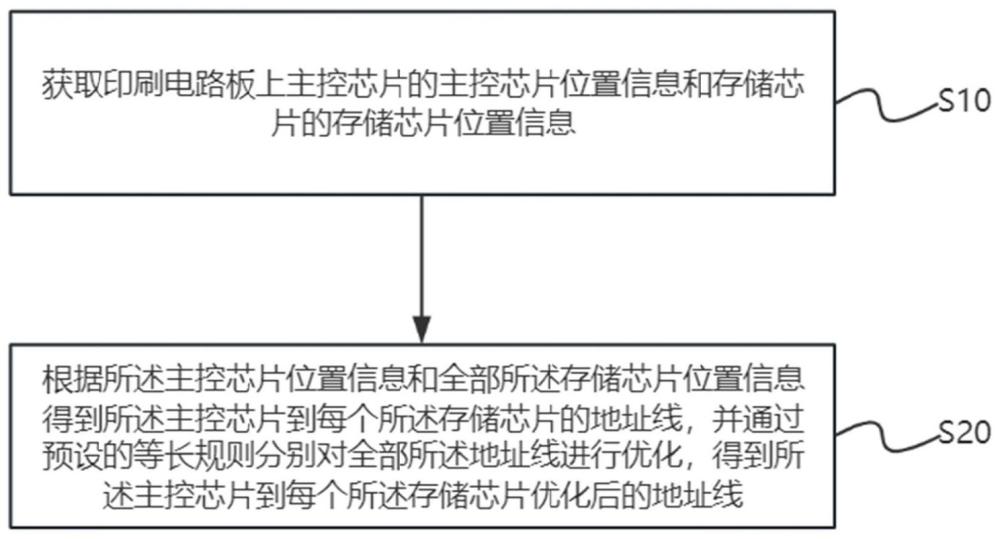

2、为解决上述问题,第一方面,本发明提供一种地址线优化方法,包括:

3、获取印刷电路板上主控芯片的主控芯片位置信息和存储芯片的存储芯片位置信息;

4、根据所述主控芯片位置信息和全部所述存储芯片位置信息得到所述主控芯片到每个所述存储芯片的地址线,并通过预设的等长规则分别对全部所述地址线进行优化,得到所述主控芯片到每个所述存储芯片优化后的地址线。

5、可选地,所述根据所述主控芯片位置信息和全部所述存储芯片位置信息得到所述主控芯片到每个所述存储芯片的地址线,并通过预设的等长规则分别对全部所述地址线进行优化,得到所述主控芯片到每个所述存储芯片优化后的地址线,包括:

6、s21,根据所述主控芯片位置信息和对应的所述存储芯片位置信息,得到所述主控芯片到对应的所述存储芯片的多个预设等长地址线组;

7、s22,基于所述等长规则,根据全部所述预设等长地址线组得到所述主控芯片到对应的所述存储芯片的所述优化后的地址线;

8、s23,重复步骤s21和步骤s22,分别对所述主控芯片到每个所述存储芯片地址线进行优化得到对应所述优化后的地址线。

9、可选地,所述基于所述等长规则,根据全部所述预设等长地址线组得到所述主控芯片到对应的所述存储芯片的所述优化后的地址线,包括:

10、根据所述预设等长地址线组中的全部预设等长地址线和预设的基准地址线的比较结果,判断所述预设等长地址线组是否满足所述等长规则;

11、当所述预设等长地址线组满足所述等长规则时,则将所述预设等长地址线组中的所述预设等长地址线的确定为所述主控芯片到对应的所述存储芯片的所述地址线。

12、可选地,所述根据所述预设等长地址线组中的全部预设等长地址线和预设的基准地址线的比较结果,判断所述预设等长地址线组是否满足所述等长规则,包括:

13、将全部所述预设等长地址线分别和所述基准地址线进行比较,得到每个预设等长地址线对应的地址线误差值;

14、根据全部所述地址线误差值分别和预设的等长阈值的比较结果,判断对应的所述预设等长地址线组是否满足所述等长规则。

15、可选地,所述地址线误差值满足:

16、ai=|xi-l|;

17、其中,ai为第i个所述地址线的所述地址线误差值,xi为第i个所述地址线的长度,l为所述基准地址线的长度。

18、可选地,所述根据全部所述地址线误差值分别和预设的等长阈值的比较结果,判断对应的所述预设等长地址线组是否满足所述等长规则,包括:

19、若全部所述地址线误差值都小于或者等于预设的等长阈值,则判断对应的所述预设等长地址线组满足所述等长规则;

20、否则,判断对应的所述预设等长地址线组不满足所述等长规则。

21、可选地,所述根据所述主控芯片位置信息和对应的所述存储芯片位置信息,得到所述主控芯片到对应的所述存储芯片的多个预设等长地址线组,包括:

22、根据所述主控芯片位置信息和对应的所述存储芯片位置信息,通过预设的时序约束和布线工具,创建所述主控芯片到对应的所述存储芯片的多组所述预设等长地址线。

23、第二方面,本发明还提供一种地址线优化装置,包括:

24、获取模块,用于获取印刷电路板上主控芯片的主控芯片位置信息和存储芯片的存储芯片位置信息;

25、优化模块,用于根据所述主控芯片位置信息和全部所述存储芯片位置信息得到所述主控芯片到每个所述存储芯片的地址线,并通过预设的等长规则分别对全部所述地址线进行优化,得到所述主控芯片到每个所述存储芯片优化后的地址线。

26、第三方面,本发明还提供一种电子设备,包括:

27、所述存储器,用于存储计算机程序;

28、所述处理器,用于当执行所述计算机程序时,实现如第一方面所述的地址线优化方法。

29、第四方面,本发明实施例提供的一种计算机可读存储介质,所述存储介质上存储有计算机程序,当所述计算机程序被处理器执行时,实现如上所述的地址线优化方法。

30、本发明通过主控芯片和每个存储芯片的位置关系,可以生成主控芯片到每个存储芯片多根等长的地址线,进而通过等长规则分别对主控芯片到每个存储芯片的地址线进行优化处理,从而使主控芯片到对应存储芯片间地址线的长度误差控制在合理的范围内,最终得到符合信号传输需要的主控芯片到每个存储芯片接近等长的地址线,保证了主控芯片到每个存储芯片的地址线间的误差都符合等长规则,即主控芯片到任一存储芯片间的全部地址线的误差值都控制在合理的范围内,通过优化后的地址线可以减小信号传输路径上的延迟差异,确保不同地址线的信号同时到达对应的每个存储芯片,保证了系统的时序稳定性,提高了主控芯片与存储芯片间信号传输的稳定性。

技术特征:1.一种地址线优化方法,其特征在于,包括:

2.根据权利要求1所述的地址线优化方法,其特征在于,所述根据所述主控芯片位置信息和全部所述存储芯片位置信息得到所述主控芯片到每个所述存储芯片的地址线,并通过预设的等长规则分别对全部所述地址线进行优化,得到所述主控芯片到每个所述存储芯片优化后的地址线,包括:

3.根据权利要求2所述的地址线优化方法,其特征在于,所述基于所述等长规则,根据全部所述预设等长地址线组得到所述主控芯片到对应的所述存储芯片的所述优化后的地址线,包括:

4.根据权利要求3所述的地址线优化方法,其特征在于,所述根据所述预设等长地址线组中的全部预设等长地址线和预设的基准地址线的比较结果,判断所述预设等长地址线组是否满足所述等长规则,包括:

5.根据权利要求4所述的地址线优化方法,其特征在于,所述地址线误差值满足:

6.根据权利要求4所述的地址线优化方法,其特征在于,所述根据全部所述地址线误差值分别和预设的等长阈值的比较结果,判断对应的所述预设等长地址线组是否满足所述等长规则,包括:

7.根据权利要求2所述的地址线优化方法,其特征在于,所述根据所述主控芯片位置信息和对应的所述存储芯片位置信息,得到所述主控芯片到对应的所述存储芯片的多个预设等长地址线组,包括:

8.一种地址线优化装置,其特征在于,包括:

9.一种电子设备,其特征在于,包括存储器和处理器;

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器读取并运行时,实现如权利要求1至7任一所述的地址线优化方法。

技术总结本发明提供了一种地址线优化方法、装置、设备及存储介质,涉及电路设计技术领域,该方法包括:获取印刷电路板上主控芯片的主控芯片位置信息和存储芯片的存储芯片位置信息;根据主控芯片位置信息和全部存储芯片位置信息得到主控芯片到每个存储芯片的地址线,并通过预设的等长规则分别对全部地址线进行优化,得到主控芯片到每个存储芯片优化后的地址线。本发明可以有效提高主控芯片和存储芯片间信号传输的稳定性。技术研发人员:李勇强,孙传斌,张建超,郭茹受保护的技术使用者:深圳中科系统集成技术有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240730/194157.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表