一种NPC1三电平驱动时序保护电路的制作方法

- 国知局

- 2024-07-31 17:55:22

本发明涉及能源电力,具体地涉及一种npc1三电平驱动时序保护电路。

背景技术:

1、近年来随着电力电子技术在电力行业的发展,对大功率变换器要求越来越高,变换器逐渐转向高压系统,同时,npc三电平技术开始越来越多的应用到各个领域,其适合用于高电压、大功率电路和系统,包括光伏逆变器、风电变流器、高压变频器、ups、apf/svg、高频电源等都有着广泛的应用。npc拓扑最常用的有两种结构,一种是“i”字型,也称npc1,另一种是“t”字型,也称npc2、mnpc、tnpc、npp等,该拓扑结构受控制模块控制进行功率控制,正常情况下,三电平拓扑只能出现正常工作状态,其他状态都是有风险的,因此,如何让上述拓扑结构保持在正常工作状态是十分重要的。

技术实现思路

1、本发明的目的在于提供一种安全稳定的npc1三电平驱动时序保护电路。

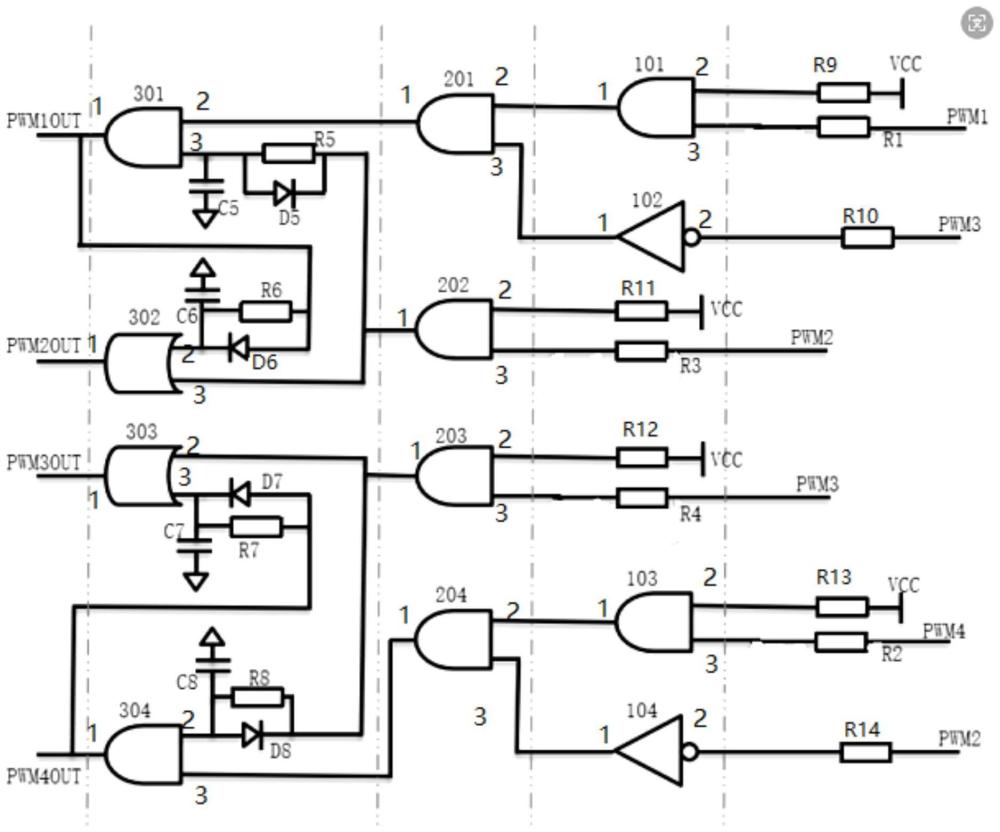

2、为解决上述技术问题,本申请采用的一个技术方案是:提供一种npc1三电平驱动时序保护电路,连接在控制电路和npc1三电平拓扑电路之间,用以驱动npc1三电平拓扑电路的i gbt功率元件,其特征在于,所述npc1三电平驱动时序保护电路包括第一门极驱动模块、第二门极驱动模块、第三门极驱动模块和第四门极驱动模块。

3、所述第一门极驱动模块的输入端连接控制电路的信号端pwm1和信号端pwm3,所述第一门极驱动模块的输出端连接所述i gbt功率元件的第一外管t1;所述第二门极驱动模块的输入端连接控制电路的信号端pwm2,所述第二门极驱动模块的输出端连接所述i gbt功率元件的第一内管t2;所述第三门极驱动模块的输入端连接控制电路的信号端pwm3,所述第三门极驱动模块的输出端连接所述i gbt功率元件的第二内管t3;所述第四门极驱动模块的输入端连接控制电路的信号端pwm2和信号端pwm4,所述第四门极驱动模块的输出端连接所述i gbt功率元件的第二外管t4。

4、所述第一门极驱动模块和第三门极驱动模块同时接收到高电平时,所述第一门极驱动模块驱动所述第一外管t1截止,所述第二门极驱动模块和第四门极驱动模块同时接收到高电平时,所述第四门极驱动模块驱动所述第二外管t4截止。

5、作为优选方案,所述第一门极驱动模块包括第一与门和第一延时模块,所述第二门极驱动模块包括第一或门、第二与门和第二延时模块,所述第一与门的1脚连接所述第一外管t1,所述第一与门的3脚连接所述第一延时模块,所述第一延时模块的另一端连接所述第二与门的1脚,所述第一或门的1脚连接所述第一内管t2,所述第一或门的2脚连接所述第二延时模块,所述第二延时模块的另一端连接所述第一与门的1脚,所述第一或门的3脚连接所述第二与门的1脚。

6、作为优选方案,所述第四门极驱动模块包括第三与门和第三延时模块,所述第三门极驱动模块包括第二或门、第四与门和第四延时模块,所述第三与门的1脚连接所述第二外管t4,所述第三与门的2脚连接所述第三延时模块,所述第三延时模块的另一端连接所述第四与门的1脚,所述第二或门的1脚连接所述第二内管t3,所述第二或门的3脚连接所述第四延时模块,所述第四延时模块的另一端连接所述第三与门的1脚,所述第二或门的2脚连接所述第四与门的1脚。

7、作为优选方案,所述第一门极驱动模块还包括第五与门、第六与门和第一非门,所述第五与门的1脚连接所述第一与门的2脚,所述第五与门的2脚连接所述第六与门的1脚,所述第五与门的3脚连接所述第一非门的1脚,所述第六与门的2脚连接高压输入端,所述第六与门的3脚连接信号端pwm1,所述第一非门的2脚连接信号端pwm3。

8、作为优选方案,所述第四门极驱动模块还包括第七与门、第八与门和第二非门,所述第七与门的1脚连接所述第三与门的3脚,所述第七与门的2脚连接所述第八与门的1脚,所述第七与门的3脚连接所述第二非门的1脚,所述第八与门的2脚连接高压输入端,所述第八与门的3脚连接信号端pwm4,所述第二非门的2脚连接信号端pwm2。

9、作为优选方案,所述第一门极驱动模块还包括电阻r1、电阻r9和电阻r10,所述电阻r1连接在所述第六与门的3脚和信号端pwm1之间,所述电阻r9连接在所述第六与门的2脚和高压输入端之间,所述电阻r10连接在所述第一非门的2脚和信号端pwm3之间。

10、作为优选方案,所述第四门极驱动模块还包括电阻r2、电阻r13和电阻r14,所述电阻r2连接在所述第八与门的3脚和信号端pwm4之间,所述电阻r13连接在所述第八与门的2脚和高压输入端之间,所述电阻r14连接在所述第二非门的2脚和信号端pwm2之间。

11、作为优选方案,所述第一延时模块包括电阻r5、二极管d5、电容c5,所述二极管d5的正极连接所述第一与门的3脚,所述二极管d5的负极连接所述第二与门的1脚,所述电阻r5并联在所述二极管d5的两端,所述电容c5的一端连接在所述第一与门的3脚和电阻r5之间,所述电容c5的另一端接地。

12、所述第二延时电路包括电阻r6、二极管d6、电容c6,所述二极管d6的正极连接所述第一与门的1脚,所述二极管d6的负极连接所述第一或门的2脚,所述电阻r6并联在所述二极管d6的两端,所述电容c6的一端连接在所述电阻r6和第一或门的2脚之间,所述电容c6的另一端接地。

13、作为优选方案,所述第三延时模块包括电阻r8、二极管d8、电容c8,所述二极管d8的正极连接所述第三与门的2脚,所述二极管d8的负极连接所述第七与门的1脚,所述电阻r8并联在所述二极管d8的两端,所述电容c8的一端连接在所述第三与门的2脚和电阻r8之间,所述电容c8的另一端接地。

14、所述第四延时电路包括电阻r7、二极管d7、电容c7,所述二极管d7的正极连接所述第三与门的1脚,所述二极管d7的负极连接所述第二或门的3脚,所述电阻r7并联在所述二极管d7的两端,所述电容c7的一端连接在所述电阻r7和第二或门的3脚之间,所述电容c7的另一端接地。

15、本发明提供的npc1三电平驱动时序保护电路,利用第一门极驱动模块、第二门极驱动模块、第三门极驱动模块和第四门极驱动模块组合对i gbt功率元件的第一外管t1、第一内管t2、第二外管t4、第二内管t3进行逻辑判断,在出现互补管同时发生时优先关断外管,避免出现半母线短路引起机器故障。

技术特征:1.一种npc1三电平驱动时序保护电路,连接在控制电路和npc1三电平拓扑电路之间,用以驱动npc1三电平拓扑电路的igbt功率元件,其特征在于,所述npc1三电平驱动时序保护电路包括第一门极驱动模块、第二门极驱动模块、第三门极驱动模块和第四门极驱动模块;

2.如权利要求1所述的npc1三电平驱动时序保护电路,其特征在于,所述第一门极驱动模块包括第一与门(301)和第一延时模块,所述第二门极驱动模块包括第一或门(302)、第二与门(202)和第二延时模块,所述第一与门(301)的1脚连接所述第一外管t1,所述第一与门(301)的3脚连接所述第一延时模块,所述第一延时模块的另一端连接所述第二与门(202)的1脚,所述第一或门(302)的1脚连接所述第一内管t2,所述第一或门(302)的2脚连接所述第二延时模块,所述第二延时模块的另一端连接所述第一与门(301)的1脚,所述第一或门(302)的3脚连接所述第二与门(202)的1脚。

3.如权利要求1所述的npc1三电平驱动时序保护电路,其特征在于,所述第四门极驱动模块包括第三与门(304)和第三延时模块,所述第三门极驱动模块包括第二或门(303)、第四与门(203)和第四延时模块,所述第三与门(304)的1脚连接所述第二外管t4,所述第三与门(304)的2脚连接所述第三延时模块,所述第三延时模块的另一端连接所述第四与门(203)的1脚,所述第二或门(303)的1脚连接所述第二内管t3,所述第二或门(303)的3脚连接所述第四延时模块,所述第四延时模块的另一端连接所述第三与门(304)的1脚,所述第二或门(303)的2脚连接所述第四与门(203)的1脚。

4.如权利要求2所述的npc1三电平驱动时序保护电路,其特征在于,所述第一门极驱动模块还包括第五与门(201)、第六与门(101)和第一非门(102),所述第五与门(201)的1脚连接所述第一与门(301)的2脚,所述第五与门(201)的2脚连接所述第六与门(101)的1脚,所述第五与门(201)的3脚连接所述第一非门(102)的1脚,所述第六与门(101)的2脚连接高压输入端,所述第六与门(101)的3脚连接信号端pwm1,所述第一非门(102)的2脚连接信号端pwm3。

5.如权利要求3所述的npc1三电平驱动时序保护电路,其特征在于,所述第四门极驱动模块还包括第七与门(204)、第八与门(103)和第二非门(104),所述第七与门(204)的1脚连接所述第三与门(304)的3脚,所述第七与门(204)的2脚连接所述第八与门(103)的1脚,所述第七与门(204)的3脚连接所述第二非门(104)的1脚,所述第八与门(103)的2脚连接高压输入端,所述第八与门(103)的3脚连接信号端pwm4,所述第二非门(104)的2脚连接信号端pwm2。

6.如权利要求4所述的npc1三电平驱动时序保护电路,其特征在于,所述第一门极驱动模块还包括电阻r1、电阻r9和电阻r10,所述电阻r1连接在所述第六与门(101)的3脚和信号端pwm1之间,所述电阻r9连接在所述第六与门(101)的2脚和高压输入端之间,所述电阻r10连接在所述第一非门(102)的2脚和信号端pwm3之间。

7.如权利要求5所述的npc1三电平驱动时序保护电路,其特征在于,所述第四门极驱动模块还包括电阻r2、电阻r13和电阻r14,所述电阻r2连接在所述第八与门(103)的3脚和信号端pwm4之间,所述电阻r13连接在所述第八与门(103)的2脚和高压输入端之间,所述电阻r14连接在所述第二非门(104)的2脚和信号端pwm2之间。

8.如权利要求2所述的npc1三电平驱动时序保护电路,其特征在于,所述第一延时模块包括电阻r5、二极管d5、电容c5,所述二极管d5的正极连接所述第一与门(301)的3脚,所述二极管d5的负极连接所述第二与门(202)的1脚,所述电阻r5并联在所述二极管d5的两端,所述电容c5的一端连接在所述第一与门(301)的3脚和电阻r5之间,所述电容c5的另一端接地;

9.如权利要求3所述的npc1三电平驱动时序保护电路,其特征在于,所述第三延时模块包括电阻r8、二极管d8、电容c8,所述二极管d8的正极连接所述第三与门(304)的2脚,所述二极管d8的负极连接所述第七与门(204)的1脚,所述电阻r8并联在所述二极管d8的两端,所述电容c8的一端连接在所述第三与门(304)的2脚和电阻r8之间,所述电容c8的另一端接地;

技术总结本发明公开了一种NPC1三电平驱动时序保护电路,连接在控制电路和NPC1三电平拓扑电路之间,用以驱动NPC1三电平拓扑电路的I GBT功率元件,所述NPC1三电平驱动时序保护电路包括第一门极驱动模块、第二门极驱动模块、第三门极驱动模块和第四门极驱动模块。实现了电路的安全稳定。技术研发人员:张志强,陈志,郁伉,王天文受保护的技术使用者:合肥华致能源科技有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/177301.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表