降低导通电阻的平面SiCMOSFET结构的制作方法

- 国知局

- 2024-07-31 18:19:54

本发明涉及半导体,特别是一种降低导通电阻的平面sic mosfet结构。

背景技术:

1、功率半导体具有大驱动电流、高击穿电压、开关速度快、低功耗、输出功率大等优点,可完成在不同功率范围内的控制和转换,广泛应用于在消费电子、航空航天、铁路、电动汽车和电力系统等领域。由于材料科学技术的进步,用碳化硅(sic)、氮化镓(gan)等宽带隙材料制造的功率器件已经被提出,功率半导体的发展向着具有小尺寸和高电压的方向发展。

2、缩减元胞尺寸是提升碳化硅mosfet效率的有效手段,然而当传统的碳化硅mosfet元胞尺寸缩减至一定程度后,工艺加工能力制约了元胞尺寸的进一步缩减。在最新的技术中减小元胞尺寸,减小器件导通电阻,提高电流密度的方法中最普遍的就是将平面栅改为沟槽栅,例如专利us20220336602a1,使用沟槽栅达到减小器件尺寸的效果;专利us20220262906a1,使用沟槽栅,再加上减小p型基区的达到减小导通电阻的效果;专利202310177334.5,使用沟槽栅和屏蔽区电压自适应调整减小导通电阻。沟槽栅能够消除jfet效应,减小元胞尺寸,但是存在工艺难度大,工艺成本高,可靠性不高等问题,而本发明的阶梯形jfet能够最大限度减小jfet效应,减小元胞尺寸,同时工艺简单,工艺成本低,平面栅的可靠性高。还有的方法就是从元胞的深p+区手,减小器件尺寸,例如专利202311498426.x,使用沟槽源区减小元胞尺寸;专利202311225903.5,也是使用沟槽源区减小元胞尺寸;专利202310901094.9,使用完全自对准方法减小元胞尺寸。在深p+区刻蚀沟槽能够打破最小工艺尺寸对元胞尺寸的限制,但是该方法减小的程度有限,并且jfet效应的存在使的元胞不能进一步减小,而本发明的阶梯形jfet大幅度减小了jfet效应对导通电阻的影响,能够进一步减小元胞尺寸,并且工艺也比刻蚀沟槽工艺更加简单,在工艺简单的前提下即减小了导通电阻、元胞尺寸,又增大了器件电流密度,大大提高了器件的整体性能。

技术实现思路

1、为解决现有技术中存在的问题,本发明的目的是提供一种降低导通电阻的平面sic mosfet结构,本发明解决了传统平面栅结构中方形jfet对导通电阻的限制而导致导通电阻不能减小的问题,并且减小了栅宽,进一步增大了器件电流密度。

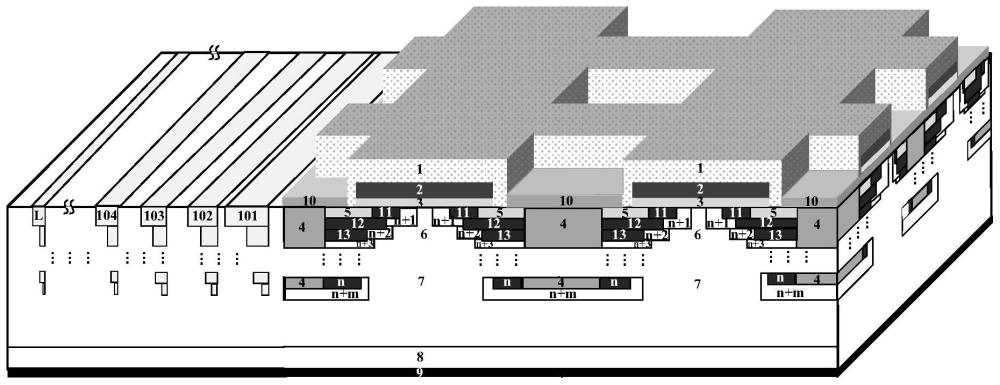

2、为实现上述目的,本发明采用的技术方案是:一种降低导通电阻的平面sicmosfet结构,包括金属源极和自下而上依次堆叠的金属漏极、n+衬底以及n-外延层,所述n-外延层的一端自下而上依次堆叠有阶梯形jfet区、倒阶梯形nwell区、倒阶梯形p型基区、栅氧层、多晶硅栅极和介质层,n-外延层内还设有深p+区和n+源区,所述n-外延层的另一端设有阶梯形终端结构。

3、作为本发明的进一步改进,所述倒阶梯形nwell区位于n-外延层上面的两侧,由多个不同宽度的方形的n-型半导体区组成,包括多个依次堆叠的n-型半导体。

4、作为本发明的进一步改进,所述倒阶梯形p型基区位于倒阶梯形nwell区上方,由多个不同宽度的方形的p型基区组成,包括多个依次堆叠的p型基区,所述倒阶梯形p型基区侧边与深p+区左右接壤,上面与n+源区上下接壤。

5、作为本发明的进一步改进,所述阶梯形jfet区位于n-外延层上面,被元胞两侧的倒阶梯形p型基区以及元胞两侧的倒阶梯形nwell区包围,形成左右对称的阶梯形jfet区,上面部分与栅氧层上下接壤。

6、作为本发明的进一步改进,所述n+源区镶嵌于倒阶梯形p型基区内部,侧边部分与深p+区左右接壤,上面部分分别与栅氧层、介质层以及金属源极上下接壤。

7、作为本发明的进一步改进,所述深p+区镶嵌于倒阶梯形nwell区内部,侧边部分分别与倒阶梯形p型基区以及n+源区左右接壤,上面部分与金属源极上下接壤。

8、作为本发明的进一步改进,所述栅氧层设置于n+源区、倒阶梯形p型基区、倒阶梯形nwell区以及阶梯形jfet区上面,下面部分分别与n+源区、倒阶梯形p型基区、倒阶梯形nwell区以及阶梯形jfet区上下接壤,上面部分与多晶硅栅极上下接壤。

9、作为本发明的进一步改进,所述多晶硅栅极被介质层围住,下面部分与栅氧层上下接壤,上面以及侧边都与介质层接壤。

10、作为本发明的进一步改进,所述结终端结构包括多个倒阶梯形p型场限环。

11、本发明的有益效果是:

12、本发明将传统的单个方形的p型基区,设计成由多个不同宽度的方形的p型基区组成的倒阶梯形p型基区,所述倒阶梯形p型基区包括第一p型基区、第二p型基区、第三p型基区等;所述倒阶梯形p型基区外围设计了由多个不同宽度的方形的n-型半导体区组成的倒阶梯形nwell区,所述nwell区包括第一n-型半导体区、第二n-型半导体区、第三n-型半导体区等;由所述元胞左侧倒阶梯形p型基区、元胞右侧倒阶梯形p型基区、元胞左侧倒阶梯形nwell区以及元胞右侧倒阶梯形nwell区围成阶梯形jfet区,所述阶梯形jfet区没有进行额外的n型杂质掺杂,阶梯形jfet区的浓度和外延层的浓度一致;在开启时电流快速通过了阶梯形jfet区,提前流入外延层,很大程度上降低了导通电阻;由于p型基区为倒阶梯型形,开启时左右两侧pn结的耗尽区相隔较远,两侧耗尽区不容易发生夹断,因此阶梯形jfet区的宽度可以做的更窄,元胞宽度做得更小,提高器件的电流密度。

技术特征:1.一种降低导通电阻的平面sic mosfet结构,其特征在于,包括金属源极和自下而上依次堆叠的金属漏极、n+衬底以及n-外延层,所述n-外延层的一端自下而上依次堆叠有阶梯形jfet区、倒阶梯形nwel l区、倒阶梯形p型基区、栅氧层、多晶硅栅极和介质层,n-外延层内还设有深p+区和n+源区,所述n-外延层的另一端设有阶梯形终端结构。

2.根据权利要求1所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述倒阶梯形nwel l区位于n-外延层上面的两侧,由多个不同宽度的方形的n-型半导体区组成,包括多个依次堆叠的n-型半导体。

3.根据权利要求2所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述倒阶梯形p型基区位于倒阶梯形nwel l区上方,由多个不同宽度的方形的p型基区组成,包括多个依次堆叠的p型基区,所述倒阶梯形p型基区侧边与深p+区左右接壤,上面与n+源区上下接壤。

4.根据权利要求3所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述阶梯形jfet区位于n-外延层上面,被元胞两侧的倒阶梯形p型基区以及元胞两侧的倒阶梯形nwel l区包围,形成左右对称的阶梯形jfet区,上面部分与栅氧层上下接壤。

5.根据权利要求3所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述n+源区镶嵌于倒阶梯形p型基区内部,侧边部分与深p+区左右接壤,上面部分分别与栅氧层、介质层以及金属源极上下接壤。

6.根据权利要求5所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述深p+区镶嵌于倒阶梯形nwel l区内部,侧边部分分别与倒阶梯形p型基区以及n+源区左右接壤,上面部分与金属源极上下接壤。

7.根据权利要求1所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述栅氧层设置于n+源区、倒阶梯形p型基区、倒阶梯形nwel l区以及阶梯形jfet区上面,下面部分分别与n+源区、倒阶梯形p型基区、倒阶梯形nwel l区以及阶梯形jfet区上下接壤,上面部分与多晶硅栅极上下接壤。

8.根据权利要求1所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述多晶硅栅极被介质层围住,下面部分与栅氧层上下接壤,上面以及侧边都与介质层接壤。

9.根据权利要求1所述的降低导通电阻的平面sic mosfet结构,其特征在于,所述结终端结构包括多个倒阶梯形p型场限环。

技术总结本发明公开了降低导通电阻的平面SiC MOSFET结构,包括金属源极和自下而上依次堆叠的金属漏极、N+衬底以及N‑外延层,所述N‑外延层的一端自下而上依次堆叠有阶梯形JFET区、倒阶梯形Nwell区、倒阶梯形P型基区、栅氧层、多晶硅栅极和介质层,N‑外延层内还设有深P+区和N+源区,所述N‑外延层的另一端设有阶梯形终端结构;本发明解决了传统平面栅结构中方形JFET对导通电阻的限制而导致导通电阻不能减小的问题,并且减小了栅宽,进一步增大了器件电流密度。技术研发人员:汪志刚,黄孝兵,余建祖,张卓,熊琴,钟驰宇受保护的技术使用者:强华时代(成都)科技有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178796.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表