一种屏蔽栅沟槽MOSFET结构及其制备方法与流程

- 国知局

- 2024-07-31 18:58:19

本发明涉及功率半导体芯片制造,具体涉及一种屏蔽栅沟槽mosfet结构及其制备方法。

背景技术:

1、随着mosfet器件应用环境的不断变化和发展,对mosfet 器件的性能要求越来越高,栅极漏电就是评价性能的一个关键参数。mosfet栅极漏电是指由栅极到源极或漏极之间的漏电流,一般需要将栅极漏电控制在100纳安以下,过大的栅极电流可能影响器件的工作电压,使得器件功耗增大。另外过大的栅极电流还会使得器件的可靠性变差,从而缩短器件的使用寿命,甚至导致栅极和源极发生短路,造成器件失效。

2、屏蔽栅沟槽mosfet器件随着工艺技术的不断成熟,目前在很多领域有逐渐取代传统沟槽mosfet的趋势。同时,随着工艺技术的不断发展,器件尺寸也进一步缩小,当器件尺寸缩小到一定程度后,屏蔽多晶硅的接触孔和沟槽之间的距离会设计的非常小,再加上受光刻套准精度的影响,接触孔的位置会存在一定的偏差。传统的器件制造工艺,会在屏蔽多晶硅的接触孔附近形成较多的栅极多晶硅的残留,残留的栅极多晶硅与屏蔽多晶硅的接触孔距离很近,造成屏蔽多晶硅的接触孔易与栅极多晶硅之间形成漏电流,而屏蔽栅沟槽mosfet的屏蔽多晶硅与源极相连,最终表现为栅极漏电增大甚至短路,影响器件的性能。如图1所示为扫描电镜拍摄的传统的器件制造工艺栅极多晶硅刻蚀后形成的器件结构图,从图中可以看到在屏蔽多晶硅的附近有明显的栅极多晶硅残留。如图2所示为扫描电镜拍摄的传统的器件制造工艺接触孔形成后的器件结构图,从图中可以看到接触孔金属与残留的栅极多晶硅之间的距离非常小,接触孔金属与栅极多晶硅之间的绝缘氧化层厚度较薄,加上受光刻套准精度的影响,残留的栅极多晶硅与屏蔽多晶硅之间很容易形成漏电流,最终造成栅极与源极之间的漏电增大影响器件的可靠性,甚至造成器件短路失效。

技术实现思路

1、为解决背景技术中存在的全部或部分技术问题,本发明提供一种屏蔽栅沟槽mosfet结构及其制备方法,通过采用两次屏蔽多晶硅刻蚀和两次第一氧化层刻蚀,刻蚀后在屏蔽多晶硅引出区的屏蔽多晶硅的顶部两侧形成较小凹陷宽度和凹陷深度的凹槽;栅极多晶硅刻蚀后,在屏蔽多晶硅引出区的屏蔽多晶硅顶部附近无栅极多晶硅残留;本发明使用与传统工艺相同的光罩数量,通过沟槽、屏蔽多晶硅、沟道离子注入、源极注入、接触孔以及金属层六层光罩就能实现屏蔽栅沟槽mosfet器件的制造;通过该制备方法制备的器件能有效改善栅极漏电,降低器件的功率损耗以及提升器件栅极可靠性,避免器件栅极和源极发生短路失效。

2、本发明提供的技术方案如下:

3、本发明提供一种屏蔽栅沟槽mosfet结构的制备方法,包括以下步骤:

4、提供衬底,在衬底上生长一层外延层,将所述外延层划分为有源区和屏蔽多晶硅引出区,在所述有源区与所述屏蔽多晶硅引出区分别刻蚀形成连通的第一沟槽和第二沟槽;

5、在所述第一沟槽表面、所述第二沟槽表面以及所述外延层表面生长一层第一氧化层,在所述第一沟槽与所述第二沟槽内形成屏蔽多晶硅;

6、将所述第一沟槽内的屏蔽多晶硅刻蚀至第一深度,再对所述第一氧化层进行刻蚀,保留第一厚度的所述第一氧化层在所述第一沟槽侧壁以及所述第一沟槽、所述第二沟槽内的硅表面;

7、对所述第一沟槽与所述第二沟槽内的屏蔽多晶硅进行刻蚀,直至所述第一沟槽内的屏蔽多晶硅高度低于所述第一沟槽内的第一氧化层刻蚀高度,且所述第二沟槽内的屏蔽多晶硅高于所述外延层的表面;

8、去除所述外延层表面的第一氧化层,将所述第一氧化层刻蚀至所述第一沟槽和所述第二沟槽内的硅表面,在所述第二沟槽内的屏蔽多晶硅的顶部两侧形成凹陷深度小于0.1微米的凹槽;

9、在所述外延层表面、所述第一沟槽侧壁以及所述第二沟槽内的屏蔽多晶硅顶部形成第二氧化层,在所述第一沟槽内形成栅极多晶硅;

10、形成第三氧化层、隔离层、接触孔以及金属层,得到所述的屏蔽栅沟槽mosfet结构。

11、进一步地,所述在所述第一沟槽内形成栅极多晶硅,具体为:

12、在所述第一沟槽内进行多晶硅沉积,通过研磨、刻蚀,将沉积的多晶硅刻蚀至所述外延层表面以下至少0.1微米,形成所述栅极多晶硅。

13、进一步地,所述形成第三氧化层、隔离层、接触孔以及金属层之前,还包括:

14、进行沟道以及源极离子注入,在所述外延层上方分别形成相邻的体区和源区,且所述源区注入形成于所述体区上方。

15、进一步地,所述形成第三氧化层、隔离层、接触孔以及金属层,包括以下步骤:

16、在所述第二氧化层表面、所述栅极多晶硅表面以及所述凹槽表面沉积一层低温氧化物形成所述第三氧化层;

17、在所述第三氧化层表面形成隔离层;

18、确定所述有源区与所述屏蔽多晶硅引出区内接触孔位置,通过接触孔光罩,刻蚀形成接触孔;

19、在所述接触孔内进行金属层沉积,形成接触孔金属层,在所述隔离层表面形成金属层。

20、进一步地,所述第一氧化层第一次刻蚀后的厚度为100~200纳米。

21、进一步地,所述衬底为n型重掺杂;

22、所述外延层为n型轻掺杂;

23、所述隔离层为硼磷硅玻璃材质。

24、进一步地,所述在所述第一沟槽与所述第二沟槽内形成屏蔽多晶硅,具体为:

25、通过多晶硅沉积,在所述第一沟槽与所述第二沟槽内形成屏蔽多晶硅,采用化学机械研磨方式,将所述屏蔽多晶硅研磨至所述第一氧化层的表面。

26、进一步地,所述体区为p型体区,所述源区为n+源区;

27、所述接触孔底部穿过所述n+源区伸入所述p型体区,在所述接触孔底部形成有接触孔注入层。

28、同时,本发明还提供一种屏蔽栅沟槽mosfet结构,采用上述的屏蔽栅沟槽mosfet结构的制备方法制备而成,包括:

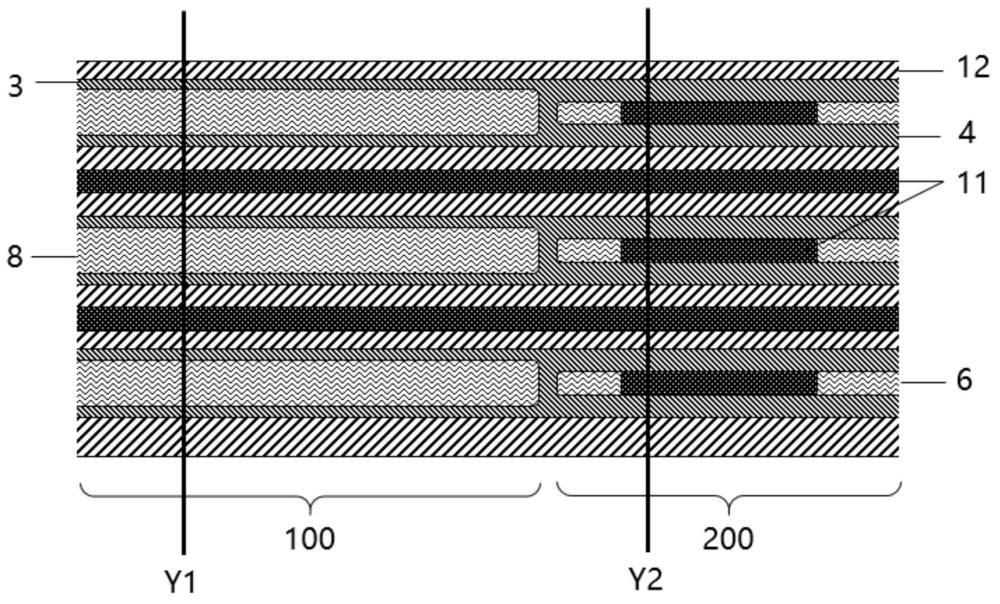

29、衬底,在所述衬底上生长有外延层,在所述外延层表面沿第一方向依次划分为有源区和屏蔽多晶硅引出区;

30、沟槽,所述沟槽为条形沟槽,多条所述条形沟槽沿第一方向等间距分布,且所述条形沟槽从所述有源区端部延伸至所述屏蔽多晶硅引出区端部;位于所述有源区内的沟槽为第一沟槽,位于所述屏蔽多晶硅引出区内的沟槽为第二沟槽;

31、所述第一沟槽内从上至下分布有隔离的栅极多晶硅和屏蔽多晶硅;所述第二沟槽内分布有屏蔽多晶硅,且在所述屏蔽多晶硅顶部两侧形成有凹陷深度小于0.1微米的凹槽;

32、p型体区,所述p型体区注入形成于所述外延层表面;

33、n+源区,所述n+源区注入形成于所述p型体区表面;

34、隔离层,所述隔离层淀积形成于所述外延层上表面,所述隔离层表面设置有金属层;

35、接触孔,所述接触孔分布于相邻所述沟槽之间以及所述第二沟槽内;分布于相邻所述沟槽之间的接触孔与所述沟槽平行,且接触孔底部穿过所述n+源区伸入所述p型体区,在接触孔底部形成有接触孔注入层;在所有接触孔中填充有接触孔金属层。

36、进一步地,所述第一沟槽与所述第二沟槽内的栅极多晶硅周侧分布有第一氧化层;

37、所述外延层表面、所述第一沟槽内的栅极多晶硅周侧以及屏蔽多晶硅顶部形成有第二氧化层;

38、所述外延层表面、所述栅极多晶硅表面、所述第二沟槽内的凹槽中以及屏蔽多晶硅顶部的第二氧化层表面形成有第三氧化层。

39、与现有技术相比,本发明的有益效果是:

40、1.本发明提供的屏蔽栅沟槽结构及制造方法,通过该制造方法制备的屏蔽栅沟槽结构可以有效改善栅极漏电,从而提升器件性能,如降低器件在断电情况下的功率损耗以及提升器件栅极可靠性,避免器件栅极和源极发生短路失效。同时本发明的工艺制造方法能够与传统mosfet制造工艺兼容;

41、2.本发明采用了两次屏蔽多晶硅刻蚀和两次第一氧化层刻蚀;刻蚀后在屏蔽多晶硅引出区的屏蔽多晶硅的顶部两侧形成较小凹陷深度的凹槽;栅极多晶硅刻蚀后,在屏蔽多晶硅引出区的屏蔽多晶硅顶部附近无栅极多晶硅残留;

42、3.本发明使用与传统工艺相同的光罩数量,即沟槽,屏蔽多晶硅、沟道离子注入,源极注入,接触孔以及金属层六层光罩就能实现屏蔽栅沟槽mosfet器件的制造;

43、4.本发明工艺制造方法能有效改善栅极漏电,降低器件的功率损耗以及提升器件栅极可靠性,避免器件栅极和源极发生短路失效。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181176.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表