一种多功能集成抗浪涌防护器件芯片及其制作工艺的制作方法

- 国知局

- 2024-07-31 19:00:52

本发明涉及芯片制造内的多功能集成抗浪涌防护器件芯片及其制作工艺。

背景技术:

1、随着科技的不断进步和发展,浪涌防护器件作为一种通信、安防等领域不可缺少的元器件,应用越来越广泛,市场容量也逐步增加,随着终端产品不断向小型化发展,器件的集中度也越来越高,常规的大功率单管防护器件如:二极管、三极管、晶闸管已不局限于做成单颗芯片使用,而更多低将多芯片集成在一颗芯片上,生产效率大大提升、产品的成本也随之大大下降,因此,芯片的集成化、多功能化成为了各芯片制造企业设计人员重点研究的方向。现有技术中的抗浪涌防护器件,只能单一地满足正浪涌的快速释放、负浪涌的快速释放,工作电压可调中的一种功能,无法更好地适合目前通信领域的应用环境。

技术实现思路

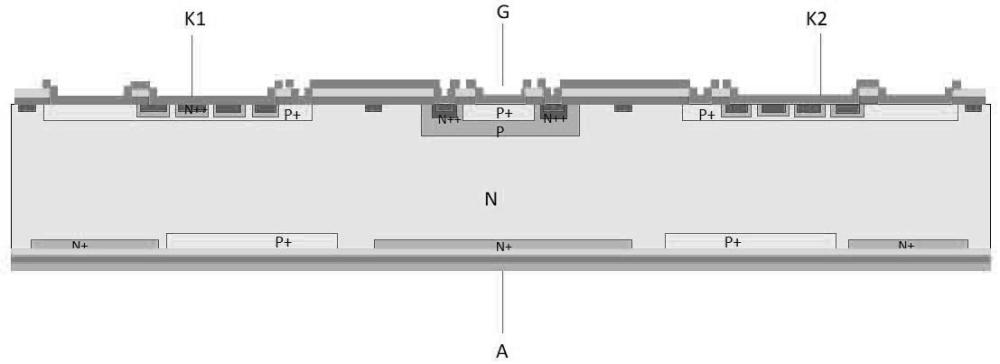

1、本发明的目的是提供一种多功能集成抗浪涌防护器件芯片及其制作工艺,实现了晶闸管、二极管、三极管多路、多功能,芯片既能够满足正浪涌的快速释放,也能满足负浪涌的快速释放,工作电压可调,可实现编程,更加适合目前通信领域的应用环境。

2、为实现上述目的,本发明提供了一种防金属连线断裂的半导体防护器件芯片,包括以下步骤,

3、步骤1)在n型单晶硅片上通过热氧化生长一层二氧化硅,其中热氧化的温度为:1120℃~1200℃,所得二氧化硅层厚度:1.2~2.0μm;

4、步骤2)在二氧化硅层上光刻出集成芯片中三极管的基区;

5、步骤3)对集成芯片中三极管的基区进行硼离子注入;

6、硼离子注入能量e=50~130kev,剂量dose=5e12/cm2~3e13/cm2。

7、步骤4)对集成芯片中三极管的基区进行硼再分布,形成p区,同时该p区表面生长一层二氧化硅;

8、步骤5)光刻出集成芯片中晶闸管的短基区、三极管的基区补硼区、二极管的正面阳极区;

9、步骤6)对集成芯片中晶闸管的短基区、三极管的基区补硼区、二极管的正面阳极区进行硼掺杂,并通过再分布形成p+区,同时该p+区表面生长一层二氧化硅;

10、步骤7)光刻出集成芯片中三极管的发射区;

11、步骤8)在三极管发射区上注入磷离子进行三极管的发射区磷掺杂,通过磷再分布形成三极管的n+区,同时该三极管的n+区表面生长一层二氧化硅;

12、步骤9)光刻出集成芯片中晶闸管的阴极区、二极管的背面阴极补磷区和三极管背面集电极补磷区;

13、步骤10)在集成芯片中晶闸管的阴极区、二极管的背面阴极补磷区和三极管背面集电极补磷区进行磷掺杂,形成晶闸管的阴极区、二极管的背面阴极补磷区和三极管背面集电极补磷区的n+区,同时该n+区的表面生长一层二氧化硅;

14、步骤11)光刻三极管的发射区补磷区和晶闸管的阴极区补磷区;

15、晶闸管的阴极补磷区短路点直径为40~60μm,比晶闸管的阴极区的短路点直径大10μm,三极管的发射区补磷区比三极管的n+区窄10~15μm

16、步骤12)三极管的发射区补磷区和晶闸管的阴极区补磷区进行淡磷扩散,形成n++区,同时该n++区表面生长一层二氧化硅;

17、步骤13)正面光刻出引线窗口;

18、步骤14)通过cvd在表面沉积一层psg多晶硅,psg多晶硅厚度为0.6~1.0μm;

19、步骤15)刻出引线孔内的psg层;

20、步骤16)正面金属化;

21、步骤17)光刻出正面金属引线;

22、步骤18)正面金铝合金;

23、步骤19)背面蒸铝;

24、步骤20)背面铝合金;

25、步骤21)背面钛镍银。

26、与现有技术相比,本发明的有益效果在于,通三极管采用共用同一基区极和集电极、双发射极的对称结构,对三极管纵向结构优化,基区采用低掺杂浓度和深结扩散,满足eb结的高反向击穿电压要求的同时,增大基区宽度,控制共射极电流放大倍数β;对二极管采用p+nn+纵向结构,三极管背面的n+区采用高掺杂浓度和深结扩散,以降低的串连电阻,改善器件的开启特性,降低器件开启时在控制管上的功耗;对单向晶闸管阴极区采用两次补磷工艺,进一步提升了抗浪涌能力。

27、作为本发明的进一步改进,步骤4中硼再分布的温度为:1220℃~1265℃,时间:50~90h,最终三极管p区的深度xj=28~50μm,该p区表面的二氧化硅层的厚度:1.2~1.6μm。

28、作为本发明的进一步改进,步骤5中晶闸管的短基区和三极管的基区补硼区采用中心对称结构。

29、这样可以保证各有缘区之间不受影响的同时,各有源区面积最大化,从而使浪涌最大化。

30、作为本发明的进一步改进,步骤6中再扩散温度为:1210℃~1260℃,时间:8~15h,最终晶闸管的短基区、三极管的基区补硼区、二极管的正面阳极区的p+区深度xj=18~27μm,该p+区表面的二氧化硅层的厚度:1.0~1.6μm。

31、作为本发明的进一步改进,步骤8中磷离子注入能量e=60~100kev,剂量dose=6e12/cm2~1.2e13/cm2;磷再扩散的温度为:1170℃~1210℃,时间:6~12h,最终三极管n+区的深度xj=10~16μm,该n+区表面的二氧化硅层厚度:0.8~1.2μm。

32、作为本发明的进一步改进,步骤9中晶闸管的阴极区的短路点采用的直径为30~50μm,短路点间距为80~120μm;二极管的背面阴极区补磷区宽度比正面对应阳极区宽10~20μm。

33、作为本发明的进一步改进,步骤10中磷扩散的温度为:1020℃~1120℃,r□=0.8~1.8ω/□,□为磷扩散后n+区的方块电阻值,表示的是磷在n+区的扩散浓度;磷扩散的温度为:1060℃~1180℃,时间:3~6h,最终晶闸管的阴极区、二极管的背面阴极补磷区和三极管背面集电极补磷区的n+区的深度xj=6~12μm,该n+区的二氧化硅层厚度:0.6~1.2μm。

34、作为本发明的进一步改进,步骤11中晶闸管的阴极补磷区短路点直径为40~60μm,比晶闸管的阴极区的短路点直径大10μm,三极管的发射区补磷区比三极管的n+区窄10~15μm。

35、作为本发明的进一步改进,步骤12中淡磷的预扩散的温度为:960℃~1040℃,r□=1.8~3.2ω/□,□为淡磷扩散后n++区的方块电阻值,表示的是淡磷在n++区的扩散浓度;淡磷扩散的温度为:980℃~1120℃,时间:3~4h,最终该n++区的深度xj=2.5~5μm,该n++区表面二氧化硅层厚度:0.5~1.0μm。

36、为了实现上述目的,本发明还提供了一种多功能集成抗浪涌防护器件芯片,包括一对对称结构的npn三极管、一对称结构二极管、一对对称结构单向晶闸管,通过金属互联的方式形成一个多功能组合芯片,三极管采用共用同一基区极和集电极、双发射极的对称结构,对三极管纵向结构优化,基区采用低掺杂浓度和深结扩散;二极管采用p+nn+纵向结构,三极管背面的n+区采用高掺杂浓度和深结扩散;单向晶闸管阴极区采用两次补磷工艺。

37、与现有技术相比,本发明的有益效果在于,输入正电流通过三极管的基区流入,使三极管开启,电流经三极管放大后流入晶闸管的控制极,从而使晶闸管打开,电路的浪涌电流经过晶闸管快速释放掉;当电路流入负电流时,三极管、晶闸管不开启,电路的浪涌电流经过二极管快速释放掉,从而保护后端的ic。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181353.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表