一种压力控制DRAM系统级测试芯片测试插座的制作方法

- 国知局

- 2024-07-31 19:14:01

本技术涉及半导体存储芯片封测,尤其涉及一种压力控制dram系统级测试芯片测试插座。

背景技术:

1、芯片测试插座(socket)在存储芯片系统级测试中,是连接芯片与pcb板的连接器插座,主要作用就是满足芯片引脚端子与pcb测试主板的联接需求,在芯片测试环节可以随时拆换芯片,不损坏芯片和pcb,从而实现快速高效的测试。

2、目前以上结构存在两个痛点,其一为探针易导致pcb表面损坏,使用一段时间后pcb表面镀层脱落,导致接触不良,影响pcb使用寿命;其二,通过控制行程来保证接触良好,在长期使用过程中,芯片测试插座机械结构会由于ic尺寸的偏差以及结构中弹簧老化,行程不变下接触压力变化,无法直观识别接触压力,导致接触不良或过压,影响测试良率甚至损坏产品。

3、有鉴于此,设计制造出一种有效降低测试过程中接触划伤、同时压力可控的的芯片测试插座,在动态随机存取内存系统级测试中显得尤为重要。

技术实现思路

1、本实用新型的目的在于:为了解决传统的芯片测试插座,使用过程中易损伤ic和pcb,同时下压力不可精准把控的问题,而提出的一种压力控制dram系统级测试芯片测试插座。

2、为了实现上述目的,本实用新型采用了如下技术方案:

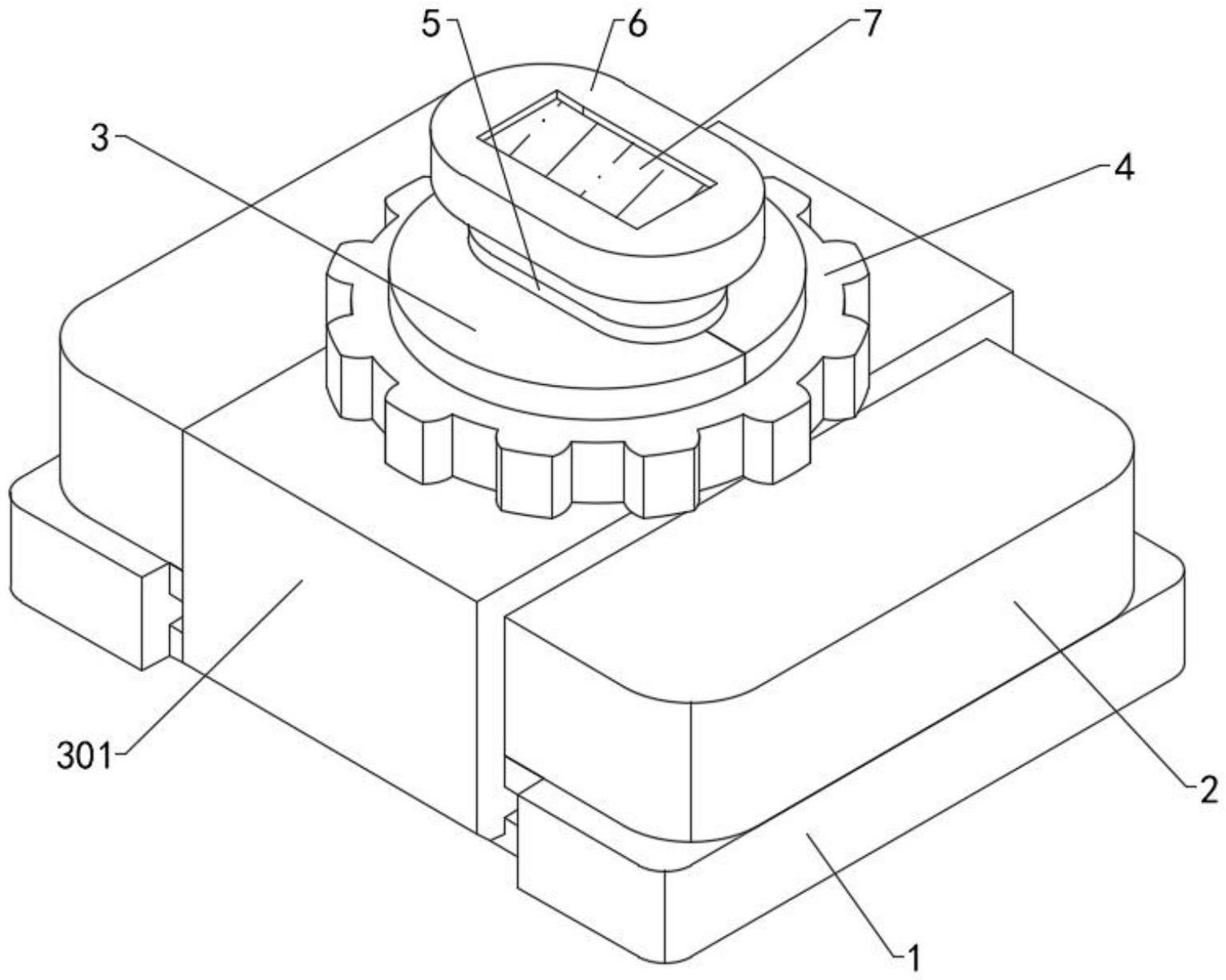

3、一种压力控制dram系统级测试芯片测试插座,包括底座、设置在底座上方的盖板、可拆卸安装在底座和盖板之间的ic和设置在底座下端用于连接ic和电路板电路的导电体,所述盖板的中部活动安装有升降滑筒,所述升降滑筒的下端固定连接有与ic上端面相互贴合的压片,所述升降滑筒和压片之间设置有用于ic测试过程中下压力监测的压感部。

4、作为上述技术方案的进一步描述:

5、所述压感部包括活动安装在升降滑筒中部的t型压头、安装在压片上端且位于t型压头下方的薄片压力传感器和嵌设在t型压头上方且与薄片压力传感器建立电性连接的微型数显屏。

6、作为上述技术方案的进一步描述:

7、所述底座和盖板外部之间设置有用于底座和盖板组合固定的扣合部。

8、作为上述技术方案的进一步描述:

9、所述扣合部包括对称在设置在盖板上方且包围升降滑筒的两个外螺扣块、通过螺纹旋合安装在两个外螺扣块之间的内螺旋套、固定在外螺扣块外部且包覆底座和盖板侧向的扣条和开设在底座侧向且与扣条相对应的扣槽。

10、作为上述技术方案的进一步描述:

11、所述压片的上端两侧和盖板下端之间对称固定连接有两个折叠弹片。

12、作为上述技术方案的进一步描述:

13、所述底座的上端为下凹状,所述底座的上端可拆卸安装有用于ic辅助定位的限位框。

14、作为上述技术方案的进一步描述:

15、所述底座上开设有多个连通ic和电路板的贯通孔,所述导电体设置在贯通孔的内侧。

16、作为上述技术方案的进一步描述:

17、所述导电体为中部为导电胶柱、两端为导电金属球组合而成的探针。

18、综上所述,由于采用了上述技术方案,本实用新型的有益效果是:

19、1、本实用新型中,通过将原先的刚性探针结构进行了科学合理化改良,改良后的探针结构是由导电胶柱和导电金属球组合而成,这种结构在保证能够正常接电测试的情况下,有效降低探针与ic和pcb之间的接触摩擦力和冲击力,降低了pcb表面镀层脱落、接触不良等问题的发生,从而延长了pcb测试的使用寿命。

20、2、本实用新型中,通过在原先的测试插座结构基础上增加了t型压头、薄片压力传感器和微型数显屏,当下压t型压头时,处于t型压头和压片之间的薄片压力传感器能够直观监测t型压头的下压力,并将数据传输至微型数显屏上进行显示,这种结构能够直观识别测试插座的接触压力,降低了测试过程中接触不良或过压等问题的发生,从而提升了pcb测试的良品率。

技术特征:1.一种压力控制dram系统级测试芯片测试插座,包括底座(1)、设置在底座(1)上方的盖板(2)、可拆卸安装在底座(1)和盖板(2)之间的ic(12)和设置在底座(1)下端用于连接ic(12)和电路板电路的导电体,其特征在于,所述盖板(2)的中部活动安装有升降滑筒(5),所述升降滑筒(5)的下端固定连接有与ic(12)上端面相互贴合的压片(9),所述升降滑筒(5)和压片(9)之间设置有用于ic(12)测试过程中下压力监测的压感部。

2.根据权利要求1所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述压感部包括活动安装在升降滑筒(5)中部的t型压头(6)、安装在压片(9)上端且位于t型压头(6)下方的薄片压力传感器(10)和嵌设在t型压头(6)上方且与薄片压力传感器(10)建立电性连接的微型数显屏(7)。

3.根据权利要求1所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述底座(1)和盖板(2)外部之间设置有用于底座(1)和盖板(2)组合固定的扣合部。

4.根据权利要求3所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述扣合部包括对称在设置在盖板(2)上方且包围升降滑筒(5)的两个外螺扣块(3)、通过螺纹旋合安装在两个外螺扣块(3)之间的内螺旋套(4)、固定在外螺扣块(3)外部且包覆底座(1)和盖板(2)侧向的扣条(301)和开设在底座(1)侧向且与扣条(301)相对应的扣槽(101)。

5.根据权利要求1所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述压片(9)的上端两侧和盖板(2)下端之间对称固定连接有两个折叠弹片(11)。

6.根据权利要求1所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述底座(1)的上端为下凹状,所述底座(1)的上端可拆卸安装有用于ic(12)辅助定位的限位框(103)。

7.根据权利要求1所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述底座(1)上开设有多个连通ic(12)和电路板的贯通孔(102),所述导电体设置在贯通孔(102)的内侧。

8.根据权利要求7所述的一种压力控制dram系统级测试芯片测试插座,其特征在于,所述导电体为中部为导电胶柱(801)、两端为导电金属球(802)组合而成的探针(8)。

技术总结本技术涉及半导体存储芯片封测技术领域,尤其涉及一种压力控制DRAM系统级测试芯片测试插座,包括底座、设置在底座上方的盖板、可拆卸安装在底座和盖板之间的IC和设置在底座下端用于连接IC和电路板电路的导电体,所述盖板的中部活动安装有升降滑筒。本技术中,首先,改良后的探针结构是由导电胶柱和导电金属球组合而成,有效降低探针与IC和PCB之间的接触摩擦力和冲击力,降低了PCB表面镀层脱落、接触不良等问题的发生,其次,通过在原先的测试插座结构基础上增加了T型压头、薄片压力传感器和微型数显屏,能够直观识别测试插座的接触压力,降低了测试过程中接触不良或过压等问题的发生,从而提升了PCB测试的良品率。技术研发人员:陈俊,余森炉,周雷,何洪文受保护的技术使用者:合肥沛顿存储科技有限公司技术研发日:20230320技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181966.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表