存储器设备及其控制方法与流程

- 国知局

- 2024-07-31 19:44:33

本发明涉及存储器设备,特别涉及非易失性存储器设备及其控制方法。

背景技术:

1、为了提高信号完整性及增强信号强度,存储器芯片采用输出驱动器及终端电阻来驱动及接收信号。然而由于存储器芯片内部的输出驱动器的驱动力及终端电阻的电阻值会受制程、电压及温度变化的影响而发生改变,因此需要定期校准输出驱动器及终端电阻来确保信号品质。zq校准是一种调整芯片的输出驱动器的驱动力及终端电阻的电阻值的校准方法,采用存储器芯片外部的精密zq电阻来对存储器芯片内部的输出驱动器的驱动力及终端电阻的电阻值进行校准。

2、在相关技术中的zq校准中,每个存储器芯片及控制器芯片均需配置独立的zq电阻,造成电路面积增加及制造费用增加。

技术实现思路

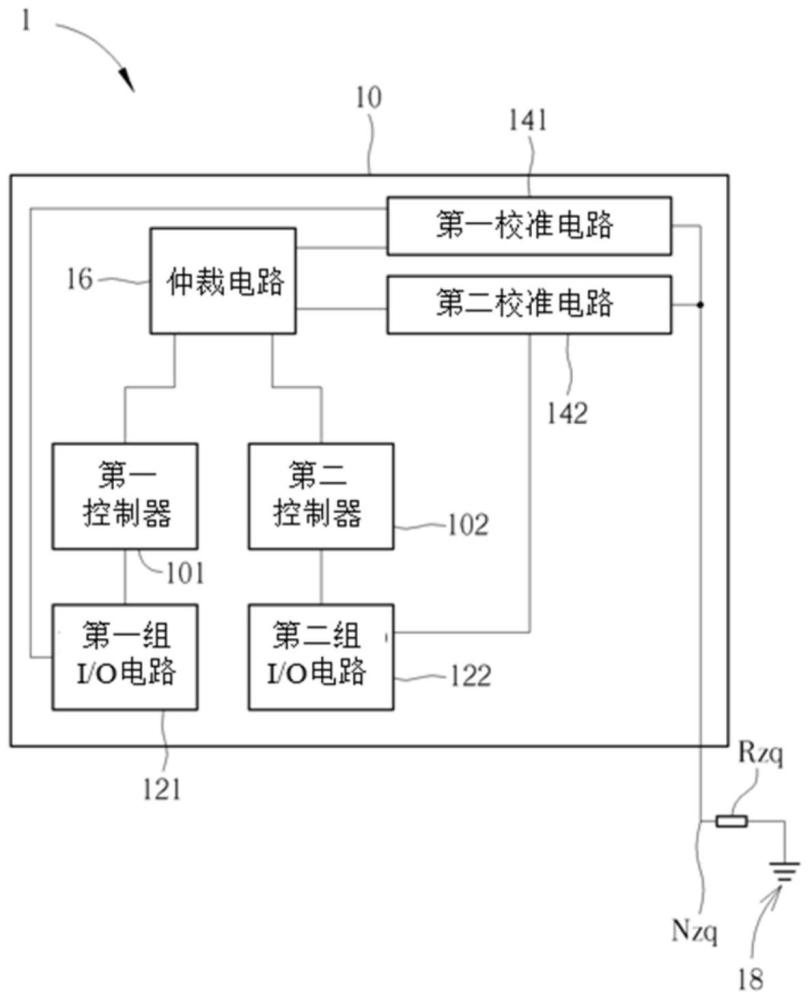

1、本发明实施例提供一种存储器设备,包括电阻及控制器芯片。电阻耦接在连接端及接地端之间。控制器芯片包括第一控制器、第二控制器、第一组输入输出电路、第二组输入输出电路、第一校准电路、第二校准电路及仲裁电路。第一控制器用于传输第一控制器校准请求。第二控制器用于传输第二控制器校准请求。第一组输入输出电路耦接于第一控制器。第二组输入输出电路耦接于第二控制器。第一校准电路耦接于连接端及第一组输入输出电路,用于使用电阻进行第一组输入输出电路的第一控制器校准。第二校准电路耦接于连接端及第二组输入输出电路,用于使用电阻进行第二组输入输出电路的第二控制器校准。仲裁电路耦接于第一控制器、第二控制器、第一校准电路及第二校准电路,用于响应于第一控制器校准请求,指示第一校准电路进行第一控制器校准,及响应于第二控制器校准请求,指示第二校准电路进行第二控制器校准。第一校准电路进行第一控制器校准的第一时段及第二校准电路进行第二控制器校准的第二时段不重叠。

2、本发明实施例还提供一种存储器设备的控制方法。存储器设备包括电阻及控制器芯片,电阻耦接在连接端及接地端之间,控制器芯片包括第一控制器、第二控制器、第一组输入输出电路、第二组输入输出电路、第一校准电路、第二校准电路及仲裁电路,第一组输入输出电路耦接于第一控制器,第二组输入输出电路耦接于第二控制器,第一校准电路耦接于连接端及第一组输入输出电路,第二校准电路耦接于连接端及第二组输入输出电路,仲裁电路耦接于第一控制器、第二控制器、第一校准电路及第二校准电路。控制方法包括第一控制器传输第一控制器校准请求,第二控制器传输第二控制器校准请求,及仲裁电路响应于第一控制器校准请求,指示第一校准电路进行第一控制器校准,及响应于第二控制器校准请求,指示第二校准电路进行第二控制器校准。第一校准电路进行第一控制器校准的第一时段及第二校准电路进行第二控制器校准的第二时段不重叠。

技术特征:1.一种存储器设备,其特征在于,包括:

2.根据权利要求1所述的存储器设备,其特征在于,所述仲裁电路在所述第一时段中收到所述第二控制器校准请求,及在所述第一时段结束后,响应于所述第二控制器校准请求,指示所述第二校准电路进行所述第二控制器校准。

3.根据权利要求1所述的存储器设备,其特征在于,所述第一时段的一长度及所述第二时段的一长度等于一预定时间长度。

4.根据权利要求1所述的存储器设备,其特征在于,所述第一校准电路还用于在收到进行所述第一控制器校准的一指示后,反馈所述第一控制器校准的一所需时间至所述仲裁电路。

5.根据权利要求1所述的存储器设备,其特征在于,还包括:

6.一种存储器设备的控制方法,所述存储器设备包括一电阻及一控制器芯片,所述电阻耦接在一连接端及一接地端之间,所述控制器芯片包括一第一控制器、一第二控制器、一第一组输入输出电路、一第二组输入输出电路、一第一校准电路、一第二校准电路及仲裁电路,所述第一组输入输出电路耦接于所述第一控制器,所述第二组输入输出电路耦接于所述第二控制器,所述第一校准电路耦接于所述连接端及所述第一组输入输出电路,所述第二校准电路耦接于所述连接端及所述第二组输入输出电路,所述仲裁电路耦接于所述第一控制器、所述第二控制器、所述第一校准电路及所述第二校准电路,所述控制方法包括:

7.根据权利要求6所述的控制方法,其特征在于,还包括:

8.根据权利要求6所述的控制方法,其特征在于,所述第一时段的一长度及所述第二时段的一长度等于一预定时间长度。

9.根据权利要求6所述的控制方法,其特征在于,还包括:所述第一校准电路收到进行所述第一控制器校准的一指示后,反馈所述第一控制器校准的一所需时间至所述仲裁电路。

10.根据权利要求6所述的控制方法,其特征在于:

技术总结本发明提供一种存储器设备,包括电阻及控制器芯片。电阻耦接在连接端及接地端之间。控制器芯片包括第一控制器、第二控制器、第一组输入输出(input/output,I/O)电路、第二组I/O电路、第一校准电路、第二校准电路及仲裁电路。第一控制器传输第一控制器校准请求。第二控制器传输第二控制器校准请求。仲裁电路响应于第一控制器校准请求,指示第一校准电路使用电阻进行第一组I/O电路的第一控制器校准,及响应于第二控制器校准请求,指示第二校准电路使用电阻进行第二组I/O电路的第二控制器校准。进行第一控制器校准的第一时段及进行第二控制器校准的第二时段不重叠。技术研发人员:林文威,郑景升受保护的技术使用者:瑞昱半导体股份有限公司技术研发日:技术公布日:2024/3/12本文地址:https://www.jishuxx.com/zhuanli/20240731/183789.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表