存储器的读取电路的制作方法

- 国知局

- 2024-07-31 19:48:13

本发明涉及一种存储器的读取电路。

背景技术:

1、阻变随机存储器(rram;resistive random access memory)是一种以非导性材料的电阻在外加电场的作用下在高阻态和低阻态之间实现可逆转换为基础的新兴的非挥发性存储技术。它具有静态随机存储器的高速读写能力、动态随机存储器的高集成度,并且基本上可以实现无限次的数据写入。在施加不同电压条件后,rram能表现出高低两种阻态并且能在断电后永久地保留存储数据。rram当前主要应用于iot设备、神经网络和人工智能等领域。在商业化方面,rram主要有两大应用方向——存储应用和存算应用。存储应用上,目前已经有厂商将rram应用于mcu领域;存算一体化上,目前也已经有公司正在尝试基于rram通过存算一体架构实现ai大算力芯片,并将其应用在中心侧与边缘侧的应用场景中。

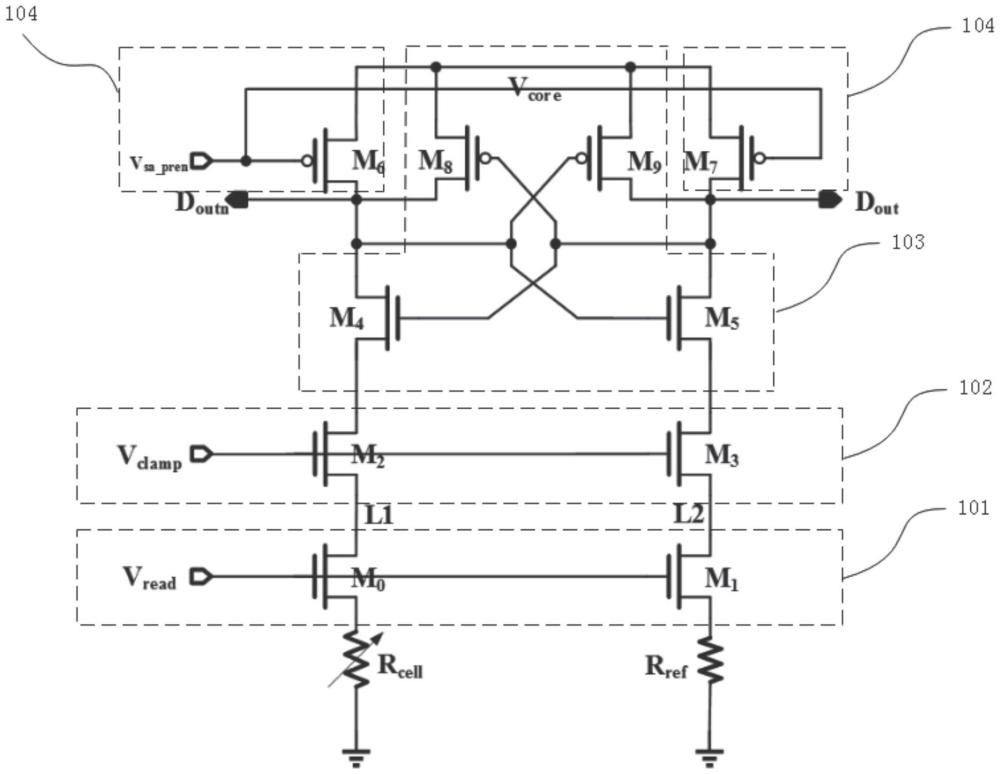

2、rram存储信息的读取方式是通过将其阻值信号转变为可供外围电路读取的电流或电压信号。随着工艺不断优化,目前关于rram存储器的读结构面临功耗大、速度变慢与面积过大等问题。现有的一种rram读取电路如图1所示。相同尺寸的晶体管m0、晶体管m1作为开关管,在读使能电压vread拉高的期间将读电路和阵列电阻进行连通。由相同尺寸的晶体管m2、晶体管m3和两个相同的ota(operational transconductance amplifier;运算跨导放大器)组成的ldo(low dropout regulaor;低压差线性稳压器)结构对a、b两点电压进行钳位,将rram的可变电阻的信息与参考电阻的信息转化为电流信息。a、b两点产生的两路电流分别被送至相同尺寸的晶体管m4和晶体管m5,晶体管m4和晶体管m5作为二极管连接的pmos晶体管可以将电流信息转化为电压信息送入比较器cmp的两端进行比较,然后输出读取数据dout。

3、此外,磁阻随机存取存储器mram(magnetic random access memory)是一种非易失性(non-volati le)的磁性随机存储器。mram拥有静态随机存储器(sram)的高速读取写入能力,以及动态随机存储器(dram)的高集成度,而且基本上可以无限次地重复写入。与传统的ram技术不同,mram不以电荷或电流存储数据,而是由磁性隧道结mtj(magnetictunnel junction)磁性存储数据。mtj是mram的基本存储单元,其核心部分是由两个铁磁金属层夹着一个隧穿势垒层构成类似于三明治结构的纳米多层膜。其中一个铁磁层被称为参考层或固定层,它的磁化沿易磁化轴方向固定不变。另一个铁磁层被称为自由层,它的磁化有两个稳定的取向,分别与参考层平行或反平行。另外,mram中的数据以一种磁性状态存储,并且通过测量电阻来感应,因此mram的读取电路与rram的读取电路的原理和结构相类似。

技术实现思路

1、虽然上述rram读取电路可以实现对rram阻值信息的读取,但是该结构存在如下缺陷。首先,随着工艺节点不断缩小,rram的高阻与低阻之间的窗口也在缩小;上述rram读取电路的方式中只是在存储单元与参考单元中产生两路比较电流之后将其转化成比较电压,其没有增大读取裕度,随着电阻窗口的减小会存在读取失败的风险。其次,存储器一般要求高于8位输出,意味着一个rram存储器至少需要8个读取电路并行输出数据,而上述rram读取电路的结构将会至少占用16个运算跨导放大器(ota)的面积,其会影响芯片的存储密度。此外,该结构的运算跨导放大器和比较器都会消耗较大功耗,并且如果要求提高精度和加快建立时间则会导致功耗更高。此外,由于mram的读取电路与rram的读取电路的原理和结构相类似,因此在现有的mram的读取电路中也存在同样的问题。

2、本发明就是鉴于上述情况而提出的,其目的在于,提供一种存储器的读取电路,该存储器的读取电路包括参考电阻、开关模块、钳位模块、交叉耦合输出模块、以及预充电模块,其通过预充电步骤以及比较读出步骤,将读使能电压、钳位电压、预充电压设定为使得可利用存储器的读取电路进行读取,以将存储器的可变电阻的阻值信号转化成差值为电源电压的输出信号和反相输出信号。

3、解决技术问题的技术方案

4、为了解决上述问题,本发明的第一方面所涉及的存储器的读取电路中,包括:

5、参考电阻;

6、开关模块,该开关模块的一侧与所述参考电阻及所述存储器的可变电阻连接,用于对所述参考电阻及所述存储器的可变电阻与钳位模块之间的通断进行控制;

7、钳位模块,该钳位模块的一侧与所述开关模块的另一侧连接,用于在预充电步骤中对该钳位模块与所述开关模块之间的节点的电压进行钳位;

8、交叉耦合输出模块,该交叉耦合输出模块的一侧与所述钳位模块的另一侧连接,用于通过正反馈将所述预充电步骤中形成的差值电流转化成差值为电源电压的输出信号和反相输出信号;以及

9、预充电模块,该预充电模块与所述交叉耦合输出模块的其他侧连接,用于对所述存储器的读取电路进行预充电。

10、进一步地,所述存储器为rram或mram。

11、进一步地,所述存储器的读取电路在进行读取时执行如下步骤:

12、预充电步骤,该预充电步骤用于使所述存储器的读取电路的第一输出端子和第二输出端子充电至电源电压;以及

13、比较读出步骤,该比较读出步骤用于通过正反馈将所述预充电步骤中形成的差值电流转化成差值为电源电压的输出信号和反相输出信号。

14、进一步地,所述开关模块包括第一晶体管以及第十晶体管,

15、所述钳位模块包括第二晶体管以及第三晶体管,

16、所述交叉耦合输出模块包括第四晶体管、第五晶体管、第八晶体管以及第九晶体管,

17、所述预充电模块包括第六晶体管以及第七晶体管,

18、所述第十晶体管的源极与rram的可变电阻连接,所述第十晶体管的栅极与所述第一晶体管的栅极连接,所述第十晶体管的漏极与所述第二晶体管的源极连接,所述第一晶体管的源极与所述参考电阻连接,所述第一晶体管的漏极与所述第三晶体管的源极连接,

19、所述第二晶体管的栅极与所述第三晶体管的栅极连接,所述第二晶体管的漏极与所述第四晶体管的源极连接,所述第三晶体管的漏极与所述第五晶体管的源极连接,

20、所述第四晶体管的栅极与所述第八晶体管的栅极、所述第五晶体管的漏极、所述第九晶体管的漏极、所述第七晶体管的漏极、以及所述存储器的读取电路的第一输出端子连接,

21、所述第五晶体管的栅极与所述第九晶体管的栅极、所述第四晶体管的漏极、所述第八晶体管的漏极、所述第六晶体管的漏极、以及所述存储器的读取电路的第二输出端子连接,

22、所述第六晶体管的栅极与所述第七晶体管的栅极连接,所述第六晶体管的源极与所述第七晶体管的源极、所述第八晶体管的源极、所述第九晶体管的源极连接,

23、所述第九晶体管的驱动能力高于所述第五晶体管的驱动能力,所述第八晶体管的驱动能力高于所述第四晶体管的驱动能力,

24、所述第六晶体管的源极、所述第七晶体管的源极、所述第八晶体管的源极、所述第九晶体管的源极被施加电源电压,

25、所述第十晶体管的栅极和所述第一晶体管的栅极被施加读使能电压,所述第二晶体管的栅极和所述第三晶体管的栅极被施加钳位电压,所述第六晶体管的栅极和所述第七晶体管的栅极被施加预充电压,

26、所述读使能电压、所述钳位电压、所述预充电压被设定为使得可利用所述存储器的读取电路进行读取,以将所述rram的可变电阻的阻值信号转化成差值为电源电压的输出信号和反相输出信号。

27、进一步地,将所述第十晶体管的漏极与所述第二晶体管的源极之间的节点设为l1,将所述第一晶体管的漏极与所述第三晶体管的源极之间的节点设为l2,

28、所述存储器的读取电路在进行读取时执行如下步骤:

29、预充电步骤,该预充电步骤中,将所述读使能电压设定为高电平,将所述预充电压设定为低电平,使得所述第十晶体管、所述第一晶体管、所述第六晶体管、所述第七晶体管导通,以使所述第一输出端子和所述第二输出端子充电至所述电源电压,并且将l1、l2钳位在所述钳位电压;以及

30、比较读出步骤,该比较读出步骤中,使所述读使能电压保持为高电平,将所述预充电压设定为高电平,使得所述第十晶体管、所述第一晶体管保持导通,所述第六晶体管、所述第七晶体管断开,以通过正反馈将所述预充电步骤中形成的差值电流转化成差值为电源电压的输出信号和反相输出信号。

31、进一步地,在所述比较读出步骤中,

32、当所述存储器的可变电阻的阻值比所述参考电阻的阻值要低时,在开始阶段所述第二输出端子的电压下降速度比所述第一输出端子的电压下降速度要快,从而使得所述第九晶体管比所述第八晶体管先导通,并且利用所述第九晶体管的驱动能力高于所述第五晶体管的驱动能力的特性,使得所述第一输出端子的电压下降停止并上升至所述电源电压,且所述第二输出端子的电压下降至0,

33、当所述存储器的可变电阻的阻值比所述参考电阻的阻值要高时,在开始阶段所述第一输出端子的电压下降速度比所述第二输出端子的电压下降速度要快,从而使得所述第八晶体管比所述第九晶体管先导通,并且利用所述第八晶体管的驱动能力高于所述第四晶体管的驱动能力的特性,使得所述第二输出端子的电压下降停止并上升至所述电源电压,且所述第一输出端子的电压下降至0。

34、进一步地,将所述存储器的可变电阻的高阻的最低值设为rh,将所述存储器的可变电阻的低阻的最高值设为rl,将所述参考电阻的阻值设为rref,

35、所述参考电阻的阻值通过如下的计算式得出:

36、

37、进一步地,所述存储器的可变电阻的高阻大于500kω,所述存储器的可变电阻的低阻小于100kω,所述参考电阻的阻值为166.67kω。

38、进一步地,所述存储器的可变电阻的高阻大于40kω,所述存储器的可变电阻的低阻小于10kω,所述参考电阻的阻值为16kω。

39、进一步地,所述第十晶体管的规格与所述第一晶体管的规格相同,

40、所述第二晶体管的规格与所述第三晶体管的规格相同,

41、所述第四晶体管的规格与所述第五晶体管的规格相同,

42、所述第六晶体管的规格与所述第七晶体管的规格相同,

43、所述第八晶体管的规格与所述第九晶体管的规格相同。

44、进一步地,所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第十晶体管是nmos晶体管,所述第六晶体管、所述第七晶体管、所述第八晶体管、所述第九晶体管是pmos晶体管。

45、发明效果

46、本发明中,读取rram阻值的过程主要分为预充电阶段和比较读出阶段这两个阶段,预充电阶段由于只存在mos晶体管的寄生电容以及连接至rram阵列的线寄生电容,因此能快速形成稳定的il1、il2;而在比较读出阶段,利用由第四晶体管m4、第五晶体管m5与第九晶体管m9、第八晶体管m8组成的交叉耦合nmos晶体管与pmos晶体管对,将电流信号通过正反馈转换为电压信号,从而可增大读取裕度,增加了rram读取数据的可靠性,并且极大加快了比较速度(例如,在28nm工艺中,rram的阻值为100kω,线寄生电容为300ff的情况下,正常工艺角下完整读取动作时间在1ns以内)。

47、此外,由于预充电阶段中从电源电压vcore到rram的可变电阻和参考电阻之间的寄生电容较低,因此预充电时间较短并且将第一输出端子dout和第二输出端子doutn充电到电源电压vcore的功耗较低,而且钳位电压vclamp将l1、l2的电压钳位在一个低值从而限制了il1与il2的电流。此外,在比较读出阶段中交叉耦合正反馈结构使第一输出端子dout和第二输出端子doutn很快拉到0或1,之后电路不再有动态电流,因此整个读出过程产生的电源功耗很低。

48、另外,为了避免对rram的可变电阻造成误写,需要对第二晶体管m2、第三晶体管m3的栅极端施加稳定抗干扰的钳位电压vclamp;而此结构在任意时刻都没有浮空点,因此不需要放电晶体管,并且也不需要运算放大器或者比较器等结构,占用面积较小。

49、此外,由于mram的读取电路与rram的读取电路的原理和结构相类似,因此可起到与上述rram读取电路类似的技术效果。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184117.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。