带Forming保护的RRAM存储器写电路的制作方法

- 国知局

- 2024-07-31 19:52:58

所属的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的存储装置、处理装置的具体工作过程及有关说明,可以参考前述方法实施例中的对应过程,在此不再赘述。本领域技术人员应该能够意识到,结合本文中所公开的实施例描述的各示例的模块、方法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,软件模块、方法步骤对应的程序可以置于随机存储器(ram)、内存、只读存储器(rom)、电可编程rom、电可擦除可编程rom、寄存器、硬盘、可移动磁盘、cd-rom、或内所公知的任意其它形式的存储介质中。为了清楚地说明电子硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以电子硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。本领域技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。术语“第一”、“第二”等是用于区别类似的对象,而不是用于描述或表示特定的顺序或先后次序。术语“包括”或者任何其它类似用语旨在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备/装置不仅包括那些要素,而且还包括没有明确列出的其它要素,或者还包括这些过程、方法、物品或者设备/装置所固有的要素。至此,已经结合附图所示的优选实施方式描述了本发明的技术方案,但是,本领域技术人员容易理解的是,本发明的保护范围显然不局限于这些具体实施方式。在不偏离本发明的原理的前提下,本领域技术人员可以对相关技术特征做出等同的更改或替换,这些更改或替换之后的技术方案都将落入本发明的保护范围之内。

背景技术:

1、阻变存储器(rram,resistive random access memory)是一种新型非易失性存储器,通过外加电场改变阻变器件介质材料的电阻值,通过不同的电阻值实现数据的存储。将阻变器件由高阻态(hrs,high resistance state)改写为低阻态(lrs,low resistancestate)的过程被称为“set”,由低阻态改写为高阻态的过程被称为“reset”。阻变器件第一次从高阻态(通常比前述set或reset过程中的高阻态的阻值更高)跳变为低阻态的过程被称为“forming”。

2、目前,基于常见的阻变材料和工艺制造的阻变器件,其set、reset电压通常在1~2v,forming电压通常需要达到3v左右。因此,对于小工艺尺寸、低电压cmos器件来说,如1.8v cmos晶体管,forming电压过高,可能导致cmos晶体管出现击穿等可靠性问题,限制了rram存储器的集成度的提升。

3、因此,如何基于低电压cmos器件设计rram存储器的写电路,实现一种基于低电压cmos晶体管的rram存储器forming保护电路,使写操作过程中不出现超过晶体管耐压能力的情况,是本领域亟待解决的技术问题。

技术实现思路

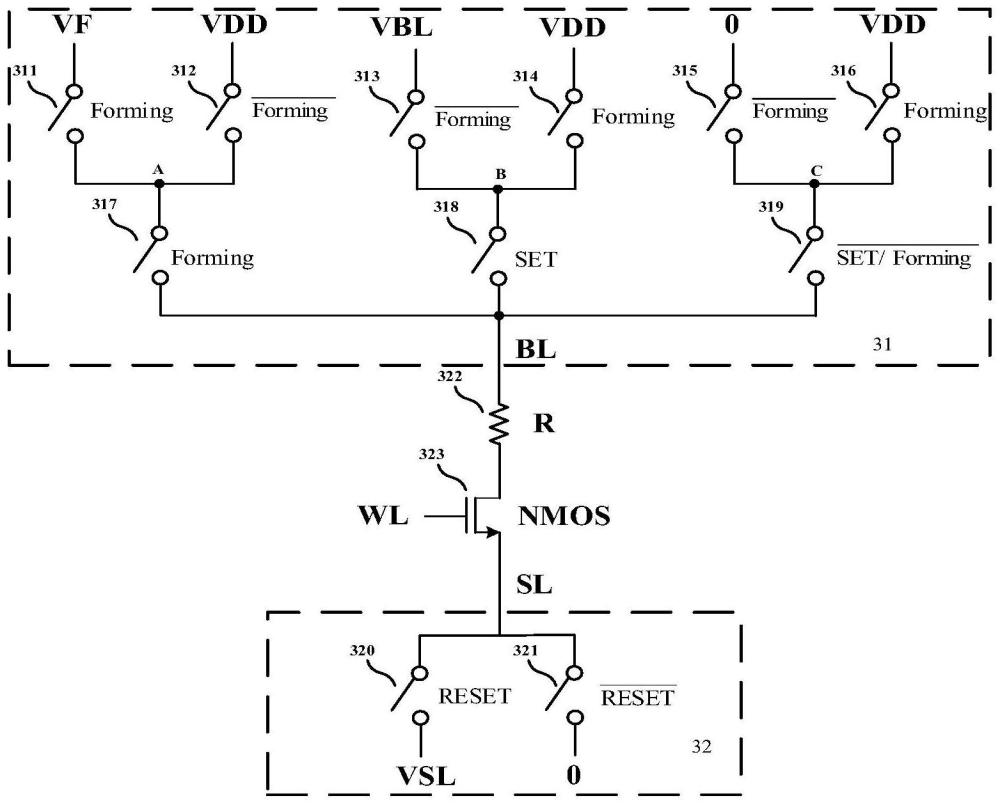

1、为了解决现有技术中的上述问题,即现有的低电压cmos器件设计的rram存储器的写电路在确保写操作过程中不出现超过晶体管耐压能力的可靠性不足的问题,本发明提供了一种带forming保护的rram存储器写电路,所述电路包括:阻变器件322、选通nmos管323和选通开关组;

2、阻变器件322的两端分别连接位线bl和选通nmos管323的漏级;

3、选通nmos管323的源极连接源线sl;

4、所述选通开关组包括第一部分31和第二部分32;

5、所述位线bl连接至第一部分31;

6、其中,所述第一部分31包括第一分支、第二分支和第三分支;

7、所述第一分支由位线bl后经过第一部分第七选通开关317和第一分支公节点a、经过第一部分第八选通开关318和第二分支公节点b、经过第一部分第九选通开关319和第三分支公节点c;所述第一分支公节点a经过第一部分第一选通开关311连接至forming电源vf,所述第一分支公节点a经过第一部分第二选通开关312连接至工作电源vdd;所述第二分支公节点b经过第一部分第三选通开关313连接至set电源vbl,所述第二分支公节点b经过第一部分第四选通开关314连接至工作电源vdd;所述第三分支公节点c经过第一部分第五选通开关315接地,所述第三分支公节点c经过第一部分第六选通开关316连接至工作电源vdd;

8、所述源线sl连接至第二部分32;

9、其中,所述第二部分32包括第二部分第一开关320和第二部分第二开关321;

10、所述源线sl同时连接至第二部分第一开关320和第二部分第二开关321;第二部分第一开关320连接reset电源vsl,第二部分第二开关321连接连接0电位。

11、进一步的,所述第一部分第一选通开关311,为互补传输门,包括:第一pmos管41、第一nmos管42和第一反相器43;

12、具体包括:

13、第一pmos管41的源极与第一nmos管42的漏极相连并连接forming电源vf;第一pmos管41的漏极与第一nmos管42的源极相连并连接第一分支公节点a;

14、第一nmos管42的栅极通过第一控制信号线连接至第一反相器43的输入端;第一反相器43的输出端连接至第一pmos管41的栅极;

15、所述第一反相器43包括第一反相器pmos管431和第一反相器nmos管432;第一反相器pmos管431的栅极与第一反相器nmos管432的栅极连接至第一反相器43的输入端;第一反相器pmos管431的漏极与第一反相器nmos管432的漏极连接至第一反相器43的输出端;第一反相器pmos管431的源极连接forming电源vf;第一反相器nmos管432的源极接地;

16、第一控制信号s1为高电平时,通过第一反相器43输出第一控制信号s1的反相信号为低电平,第一nmos管42和第一nmos管42均导通;

17、第一控制信号s1为低电平时,通过第一反相器43输出第一控制信号s1的反相信号为高电平,第一nmos管42和第一nmos管42均关断;

18、当所述阻变器件322进行forming操作时,第一控制信号s1电压为vf,第一控制信号s1的反相信号为vdd,第一选通开关311互补传输门导通;第一pmos管41、第一nmos管42、第一反相器pmos管431和第一反相器nmos管432的栅源电压和栅漏电压均为0或vf-vdd;

19、当所述阻变器件322不进行forming操作时,第一控制信号s1电压为vdd,第一控制信号s1的反相信号为vf,第一选通开关311互补传输门关闭,第一分支公节点a的电压为vdd,第一pmos管41、第一nmos管42、第一反相器pmos管431和第一反相器nmos管432的栅源电压和栅漏电压为0或vf-vdd。

20、进一步的,所述第三选通开关313,为互补传输门,包括:

21、第三pmos管61、第三nmos管62、第二反相器63和第三控制信号线;

22、具体包括:

23、第三pmos管61的源极与第三nmos管62的漏极相连并连接set电源电源vbl;第三pmos管61的漏极与第三nmos管62的源极相连并连接第二分支公节点b;

24、第三nmos管62的栅极通过第一控制信号线连接至第二反相器63的输入端;第二反相器63的输出端连接至第三pmos管61的栅极;

25、所述第二反相器63包括第二反相器pmos管631和第二反相器nmos管632;第二反相器pmos管631的栅极与第二反相器nmos管632的栅极连接至第二反相器63的输入端;第二反相器pmos管631的漏极与第二反相器nmos管632的漏极连接至第二反相器63的输出端;第二反相器pmos管631的源极连接工作电源vdd;第二反相器nmos管632的源极接地;

26、第三控制信号s3和第三控制信号s3的反相信号的高电平电压为vdd,低电平电压为0;

27、当所述阻变器件322进行forming操作时,第三控制信号s3电压为0,第三控制信号s3的反相信号电压为vdd,第三选通开关313互补传输门关闭,第二分支公节点b电压被第四选通开关314置为vdd,第三pmos管61的栅源电压为0和栅漏电压为vdd-vbl,第三nmos管62的栅源电压为vdd和栅漏电压为vbl,第二反相器pmos管631的栅源电压和栅漏电压均为vdd,第二反相器nmos管632的栅源电压为0栅漏电压为vdd;

28、当所述阻变器件322不进行forming操作时,第三控制信号s3电压为vdd,第三控制信号s3的反相信号电压为0,第三选通开关313互补传输门导通,第二分支公节点b电压为vbl。

29、所述第一部分第四选通开关314,为互补传输门,包括:

30、第四pmos管71、第四nmos管72、第三反相器73和第四控制信号线;

31、具体包括第四pmos管71的源极与第四nmos管72的漏极相连并连接工作电压vdd;第四pmos管71的漏极与第四nmos管72的源极相连并连接第二分支共节点b;

32、第四nmos管72的栅极通过第四控制信号线连接至第三反相器73的输入端;第三反相器73的输出端连接至四pmos管71的栅极;

33、所述第三反相器73包括第三反相器pmos管731和第三反相器nmos管732;第三反相器pmos管731的栅极与第三反相器nmos管732的栅极连接至第三反相器73的输入端;第三反相器pmos管731的漏极与第三反相器nmos管732的漏极连接至第三反相器73的输出端;第三反相器pmos管731的源极连接工作电源vdd;第三反相器nmos管732的源极接地;

34、当所述阻变器件322进行forming操作时,第四控制信号s4电压为vdd,第四控制信号s4的反相信号电压为0,第一部分第四选通开关314的互补传输门导通;

35、当所述阻变器件322不进行forming操作时,第四控制信号s4电压为0,第四控制信号s4的反相信号电压为vdd,第一部分第四选通开关314的互补传输门关闭。

36、进一步的,所述第一部分第五选通开关315,包括第五nmos管81;

37、第五nmos管81的栅极连接第五控制信号线,第五nmos管81的源极接地,第五nmos管81的漏极连接第三分支公节点c;

38、当所述阻变器件322进行forming操作时,第五控制信号s5的电压为0,第五nmos管81关闭,而第三分支公节点c的电压被第一部分第六选通开关316置为vdd;第五nmos管的栅源电压为0,栅漏电压为vdd;

39、当所述阻变器件322不进行forming操作时,第五控制信号s5电压为vdd,第五nmos管81导通,而第三分支公节点c的电压被第一部分第六选通开关316置为0,第五nmos管81的栅源电压和栅漏电压均为vdd。

40、进一步的,所述第一部分第六选通开关316,为互补传输门,包括:第六pmos管91、第六nmos管92和第四反相器93;

41、具体包括第六pmos管91的漏极与第六nmos管92的漏极相连并连接工作电压vdd;第六pmos管91的源极与第六nmos管92的源极相连并连接第三分支共节点c;

42、第六nmos管92的栅极通过第四控制信号线连接至第四反相器93的输入端;第四反相器93的输出端连接至六pmos管91的栅极;

43、所述第四反相器93包括第四反相器pmos管931和第四反相器nmos管932;第四反相器pmos管931的栅极与第四反相器nmos管932的栅极连接至第四反相器93的输入端;第四反相器pmos管931的漏极与第四反相器nmos管932的漏极连接至第四反相器93的输出端;第四反相器pmos管931的源极连接工作电源vdd;第四反相器nmos管932的源极接地;

44、当所述阻变器件322进行forming操作时,第六控制信号s6电压为vdd,第四控制信号s6的反相信号电压为0,第一部分第六选通开关316的互补传输门导通,第六pmos管91、第六nmos管92和第四反相器93的栅源电压为0,漏源电压为vdd;

45、当所述阻变器件322不进行forming操作时,第四控制信号s4电压为0,第四控制信号s4的反相信号电压为vdd,第一部分第六选通开关316的互补传输门关闭,第三分支公节点c被第一部分第五选通开关315置为0,第六pmos管91、第六nmos管92和第四反相器93的栅源电压和漏源电压为0或vdd。

46、进一步的,所述第一部分第七选通开关317,包括第七nmos管101;

47、第七nmos管101的栅极连接第七控制信号线,第七nmos管101的源极连接位线bl,第七nmos管101的漏极连接第一分支公节点a;

48、当所述阻变器件322进行forming操作时,第七控制信号s7的电压为vf,第七nmos管101导通,位线bl被置为第一分支公节点a的电位,第一部分第一选通开关311闭合,第一分支公节点a被置为vf,第七nmos管101的栅源电压和漏源电压为0;

49、当所述阻变器件322不进行forming操作时,第七控制信号s7电压为0,第七nmos管101关闭,而第一分支公节点a的电压被第一部分第二选通开关312置为vdd,此时当所述阻变器件322进行set操作时,位线bl被第一部分第三选通开关313和第一部分第八选通开关318置为vbl,第七nmos管101的栅源电压为vdd-vbl,栅漏电压为0;当当所述阻变器件322进行reset操作时,位线bl被第一部分第五选通开关315和第一部分第九选通开关319置为0,第七nmos管101的栅源电压为vdd,栅漏电压为0。

50、进一步的,所述第一部分第八选通开关318,包括第八nmos管111;

51、第八nmos管111的栅极连接第八控制信号线,第八nmos管111的源极连接位线bl,第八nmos管111的漏极连接第二分支公节点b;

52、当所述阻变器件322进行forming操作时,所述位线vl被第一部分第一选通开关311和第一部分第七选通开关317置为vf,第二公节点b被第一部分第四选通开关314置为vdd,第八控制信号s8电压为vdd,第八nmos管111关闭,第八nmos管111的栅源电压为vf-vdd,栅漏电压为0;

53、当所述阻变器件322进行set操作时,第二分支公节点b被第一部分第三选通开关313置为vbl,第八控制信号s8电压为vdd,第八nmos管111导通,位线bl的电压被置为vbl;set电源应满足vbl<vdd-vth,vth为第八nmos管111的阈值电压,以保证位线bl不被第八nmos管111限幅;

54、当所述阻变器件322进行reset操作时,位线bl被第一部分第六选通开关316和第一部分第九选通开关319置为0,第二分支公节点b的电压为第一部分第四选通开关314置为vdd,第八控制信号s8的电压为0,第八nmos管111关闭,第八nmos管111的栅源电压为0,栅漏电压为vdd。

55、进一步的,所述第一部分第九选通开关319,包括第九nmos管121;

56、第九nmos管121的栅极连接第九控制信号线,第九nmos管121的源极连接位线bl,第九nmos管121的漏极连接第三分支公节点c;

57、当所述阻变器件322进行forming操作时,位线bl被第一部分第一选通开关311和第一部分第七选通开关317置为vf,第三公节点c被第一部分第六选通开关316置为vdd,第九控制信号s9的电压为vdd,第九nmos管121关闭,第九nmos管121的栅源电压为vf-vdd,栅漏电压为0;

58、当所述阻变器件322进行set操作时,位线bl被第一部分第三选通开关313和第一部分第八选通开关318置为vbl,第三分支公节点c被第一部分第五选通开关315置为0,第九控制信号s9的电压为0,第九nmos管121关闭,第九nmos管121的栅源电压为vbl,栅漏电压为0;

59、当所述阻变器件322进行reset操作时,第三分支公节点c被第一部分第四选通开关314置为0,第九控制信号s9的电压为vdd,第九nmos管121导通,位线bl电压被置为0,第九nmos管121的栅源电压和栅漏电压均为vdd。

60、进一步的,所述第二部分第一开关320,为互补传输门;

61、所述第二部分第一开关320包括第十pmos管131和第十nmos管132和;

62、第十pmos管131的源极与第十nmos管132的源极连接并连接至reset电源vsl;第十pmos管131的漏极与第十nmos管132的漏极连接并连接至源线sl;

63、第十nmos管132的栅极通过第十控制信号线连接至第五反相器133的输入端;第五反相器133的输出端连接至第十pmos管131的栅极;

64、第五反相器133包括第五反相器pmos管1331和第五反相器nmos管1332;第五反相器pmos管1331的栅极和第五反相器nmos管1332的栅极连接至第五反相器133的输入端;第五反相器pmos管1331的源极连接工作电压vdd;第五反相器nmos管1332的源极接地;第五反相器pmos管1331的漏极和第五反相器nmos管1332的漏极连接至第五反相器133的输出端;

65、当所述阻变器件322进行forming操作或set操作时,第十控制信号s10的电压为0,第十控制信号s10的反相信号的电压为vdd,第二部分第一开关320的互补传输门关闭,源线sl的电压被第二部分第二开关321置为0,第十pmos管131、第十nmos管132、第五反相器pmos管1331和第五反相器nmos管1332的栅源电压和栅漏电压为0或vdd或vdd-vsl;

66、当所述阻变器件322进行reset操作是,第十控制信号s10的电压为vdd,第十控制信号s10的反相信号电压为0,第二部分第一开关320的互补传输门导通,源线电压被置为vsl,第十pmos管131、第十nmos管132、第五反相器pmos管1331和第五反相器nmos管1332的栅源电压和栅漏电压为0或vdd或vdd-vsl。

67、进一步的,所述第二部分第二开关321,包括第十一nmos管141;

68、第十一nmos管141的栅极连接第十一控制信号线,第十一nmos管141的漏极连接源线sl,第十一nmos管141的源极接地;

69、当所述阻变器件322进行forming或set操作时,第十一控制信号s11的电压为vdd,第十一nmos管141导通,源线sl被置为0,第十一nmos管141的栅源电压和栅漏电压分别均为vdd;

70、当所述阻变器件322进行reset操作时,源线sl被第二部分第一开关320置为vsl,第十一控制信号s11电压为0,第十一nmos管141关闭,第十一nmos管141的栅源电压0和栅漏电压为vsl。

71、本发明的有益效果:

72、(1)本发明提供的带forming保护的rram存储器写电路,使电源电压vdd降低到forming电压的一半,降低了电路功耗,使电路可以通过采用低压小线宽晶体管提升电路的集成度和读写速度,使新型存储器rram可以采用更小工艺节点,实现更大容量、更高速度和更低功耗。

73、(2)本发明提供的带forming保护的rram存储器写电路,能够保证在forming过程中,低压器件不超过其耐压能力。

74、(3)本发明通过两级开关配合vdd电源的选通保证了所有开关两端压差不超过耐压能力,又给出了开关控制信号的产生方案和电路,保证了控制信号产生电路本身的器件以及所有开关晶体管栅源、栅漏电压均不超过耐压能力,全面提升了电路的可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184484.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表