低延迟DDR双列直插式存储模块、存储系统及其操作方法与流程

- 国知局

- 2024-07-31 20:00:38

本发明属于存储器,更具体地,涉及一种低延迟ddr双列直插式存储模块、存储系统及其操作方法。

背景技术:

1、目前广泛使用的双数据速率(double data rate,ddr)同步动态随机存取存储器(synchronous dynamic random access memory,sdram)(也称为dram)标准适用于ddr4和ddr5存储器,并提供了一个可支持双列直插式存储模块(dual-in-line memory module,dimm)设备的通道,其可以在时钟的上升沿和下降沿记录数据。

2、ddr5 dram支持故障行地址修复,封装后修复(post package repair,ppr)允许在dimm系统中使用简单易行的修复方法。ddr5中提供了两种方法:用于永久行修复的封装后硬修复(hppr)和用于临时行修复的封装后软修复(soft post package repair,sppr)。使用封装后硬修复,ddr5可以纠正每个逻辑存储阵列(bank group,bg)中的至少一个行地址。使用封装后软修复,ddr5可以修复每个bg的一个行地址。如果bg的封装后硬修复资源用完,该bg将没有更多可用于封装后软修复的资源。

3、随着dram技术的不断发展,由于ddr5的密度更高,其收益率问题变得越来越重要。收益率问题是指:1)在dram制造过程中更可能存在缺陷。2)在dimm的整个生命周期中,某些dram单元可能丧失存储能力。即使dram制造商可以应用更严格的规则来避免上述情况1,对于dram制造商来说,要避免上述情况2并不容易。

4、业界正在开发故障行替换技术以改善上述收益率问题。使用此技术,操作系统将对dram颗粒中的故障行进行替换。rcd会记录rdimm或lrdimm中dram的故障行信息,每次需要访问dram时,rcd都会查找其记录的故障行表来进行行地址替换。但对于ddr5,rcd需要增加接收完整命令的等待时间,再考虑到查找表搜索时间,导致整个ddr5系统的效率降低。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明提供了一种低延迟ddr双列直插式存储模块,能够针对act命令及其相关命令设置单独的延时,从而有效解决进行坏行替换时影响整体系统效率的问题。

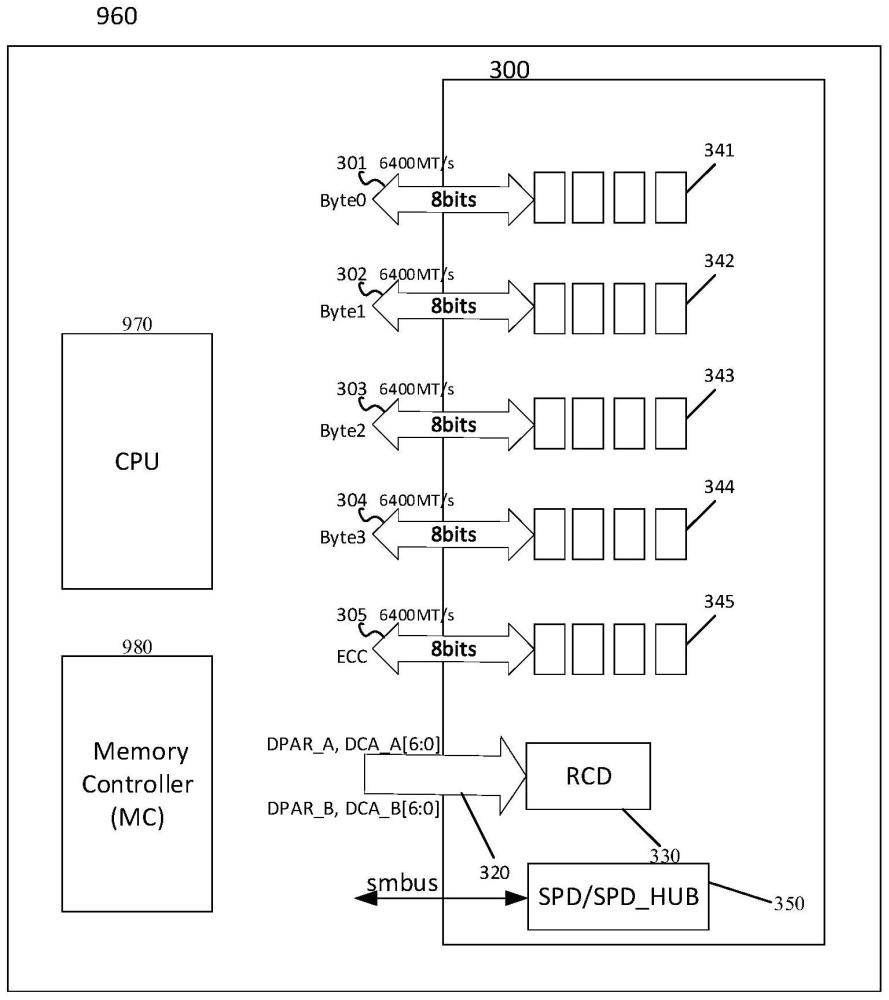

2、为实现上述目的,按照本发明的一个方面,提供了一种低延迟ddr双列直插式存储模块,包括:两个子通道、时钟锁存驱动器和spd数据存储器,其中,每一所述子通道包括多组dram芯片颗粒;所述时钟锁存驱动器用于对所述dram芯片颗粒中的坏行地址进行替换;所述spd数据存储器用于存储spd数据,所述spd数据被配置为支持ddr激活命令的独立延时设置,其中,所述独立延时设置满足所述dram芯片颗粒的时序要求。

3、在一些实施方式中,所述spd数据还被配置为对与所述ddr激活命令不相关的命令具有统一延时设置。

4、在一些实施方式中,所述独立延时设置的时长大于所述统一延时设置的时长。

5、在一些实施方式中,所述spd数据还被配置为根据所述独立延时设置的时长与所述统一延时设置的时长之间的额外差值,对与所述ddr激活命令相关的延时增加所述额外差值。

6、在一些实施方式中,所述时钟锁存驱动器具有延迟加法器,所述延迟加法器用于对所述时钟锁存驱动器接收命令的时间参数进行预设时长的延时。

7、在一些实施方式中,所述两个子通道具有相同的结构,所述时钟锁存驱动器为所述两个子通道共用。

8、在一些实施方式中,所述时钟锁存驱动器具有查找表,用于对dram芯片颗粒中的故障存储空间进行存储地址替换,所述时钟锁存驱动器包括标准时钟锁存驱动器、高带宽时钟锁存驱动器和多路复用时钟锁存驱动器。

9、在一些实施方式中,所述spd数据用于使cpu或内存控制器对发送的命令进行延时。

10、按照本发明的另一个方面,提供了一种存储系统,包括cpu和上述低延迟ddr双列直插式存储模块。

11、按照本发明的又一个方面,提供了一种存储系统的操作方法,所述存储系统包括内存控制器和低延迟ddr双列直插式存储模块,该操作方法包括:

12、所述内存控制器读取所述低延迟ddr双列直插式存储模块的spd数据存储器中的spd数据,所述spd数据被配置为支持所述低延迟ddr双列直插式存储模块的时钟锁存驱动器对ddr激活命令设置独立延时;

13、当所述低延迟ddr双列直插式存储模块的dram芯片颗粒中存在故障存储空间时,所述时钟锁存驱动器用于对所述故障存储空间进行存储地址替换;

14、所述时钟锁存驱动器还用于对接收的所述ddr激活命令进行独立延时。

15、在一些实施方式中,所述时钟锁存驱动器还用于对与所述ddr激活命令不相关的命令设置统一延时;所述spd数据还被配置为根据所述独立延时设置的时长与所述统一延时设置的时长之间的额外差值,对与所述ddr激活命令相关的延时增加所述额外差值。

16、在一些实施方式中,所述存储系统还包括系统管理总线,所述系统管理总线用于访问所述spd数据存储器。

17、在一些实施方式中,所述时钟锁存驱动器还用于在接收到所述ddr激活命令时对访问地址进行查找,若所述访问地址为故障行地址时,则使用预留地址对所述访问地址进行替换。

18、在一些实施方式中,所述低延迟ddr双列直插式存储模块包括标准ddr双列直插式存储模块、高带宽ddr双列直插式存储模块和多路合并阵列双列直插内存模组。

19、总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:通过针对act命令进行独立延时设置,并对与act命令相关的命令的延时进行补偿,同时其他命令仍处于正常的延迟加法器的控制之下,使得ddr dimm在使用行替换技术时,免除所有命令均要延长等待时间的限制,有效提升ddr5系统的效率。

技术特征:1.一种低延迟ddr双列直插式存储模块,其特征在于,包括:两个子通道、时钟锁存驱动器和spd数据存储器,其中,每一所述子通道包括多组dram芯片颗粒;所述时钟锁存驱动器用于对所述dram芯片颗粒中的坏行地址进行替换;所述spd数据存储器用于存储spd数据,所述spd数据被配置为支持ddr激活命令的独立延时设置,其中,所述独立延时设置满足所述dram芯片颗粒的时序要求。

2.如权利要求1所述的低延迟ddr双列直插式存储模块,其特征在于,所述spd数据还被配置为对与所述ddr激活命令不相关的命令具有统一延时设置。

3.如权利要求2所述的低延迟ddr双列直插式存储模块,其特征在于,所述独立延时设置的时长大于所述统一延时设置的时长。

4.如权利要求2所述的低延迟ddr双列直插式存储模块,其特征在于,所述spd数据还被配置为根据所述独立延时设置的时长与所述统一延时设置的时长之间的额外差值,对与所述ddr激活命令相关的延时增加所述额外差值。

5.如权利要求1所述的低延迟ddr双列直插式存储模块,其特征在于,所述时钟锁存驱动器具有延迟加法器,所述延迟加法器用于对所述时钟锁存驱动器接收命令的时间参数进行预设时长的延时。

6.如权利要求1所述的低延迟ddr双列直插式存储模块,其特征在于,所述两个子通道具有相同的结构,所述时钟锁存驱动器为所述两个子通道共用。

7.如权利要求1至6中任一项所述的低延迟ddr双列直插式存储模块,其特征在于,所述时钟锁存驱动器具有查找表,用于对dram芯片颗粒中的故障存储空间进行存储地址替换,所述时钟锁存驱动器包括标准时钟锁存驱动器、高带宽时钟锁存驱动器和多路复用时钟锁存驱动器。

8.如权利要求1至6中任一项所述的低延迟ddr双列直插式存储模块,其特征在于,所述spd数据用于使cpu或内存控制器对发送的命令进行延时。

9.一种存储系统,其特征在于,包括cpu、内存控制器和如权利要求1至8中任一项所述的低延迟ddr双列直插式存储模块。

10.一种存储系统的操作方法,所述存储系统包括内存控制器和低延迟ddr双列直插式存储模块,其特征在于,所述操作方法包括:

11.如权利要求10所述的操作方法,其特征在于,所述时钟锁存驱动器还用于对与所述ddr激活命令不相关的命令设置统一延时;所述spd数据还被配置为根据所述独立延时设置的时长与所述统一延时设置的时长之间的额外差值,对与所述ddr激活命令相关的延时增加所述额外差值。

12.如权利要求10所述的操作方法,其特征在于,所述存储系统还包括系统管理总线,所述系统管理总线用于访问所述spd数据存储器。

13.如权利要求10所述的操作方法,其特征在于,所述时钟锁存驱动器还用于在接收到所述ddr激活命令时对访问地址进行查找,若所述访问地址为故障行地址时,则使用预留地址对所述访问地址进行替换。

14.如权利要求10至13中任一项所述的操作方法,其特征在于,所述低延迟ddr双列直插式存储模块包括标准ddr双列直插式存储模块、高带宽ddr双列直插式存储模块和多路合并阵列双列直插内存模组。

技术总结本发明公开了一种低延迟DDR双列直插式存储模块、存储系统及其操作方法。该低延迟DDR双列直插式存储模块包括两个子通道、时钟锁存驱动器和SPD数据存储器,其中,每一所述子通道包括多组DRAM芯片颗粒;所述时钟锁存驱动器用于对所述DRAM芯片颗粒中的坏行地址进行替换;所述SPD数据存储器用于存储SPD数据,所述SPD数据被配置为支持DDR激活命令的独立延时设置,其中,所述独立延时设置满足所述DRAM芯片颗粒的时序要求。本发明通过针对ACT命令进行独立延时设置,并对与ACT命令相关的命令的延时进行补偿,同时其他命令仍处于正常的延迟加法器的控制之下,使得DDR DIMM在具备行替换功能的同时,有效提升DDR5系统的效率。技术研发人员:李伟,胡跃文,尚荣军受保护的技术使用者:芯动微电子科技(武汉)有限公司技术研发日:技术公布日:2024/6/11本文地址:https://www.jishuxx.com/zhuanli/20240731/185023.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表