一种改善主干阻抗连续性的NAND闪存菊花链拓扑结构的制作方法

- 国知局

- 2024-07-31 20:00:37

本技术涉及电路板设计,更具体地说,是涉及一种改善主干阻抗连续性的nand闪存菊花链拓扑结构。

背景技术:

1、印制电路板(printed circuit board,pcb板)又称印刷电路板,是电子产品的物理支撑以及信号传输的重要组成部分。nand flash是一种非易失性存储器(non-volatilememory,nvm)技术,广泛应用于各种电子设备中,例如固态硬盘(ssd)、闪存卡和usb闪存驱动器等。又称之为nand闪存,其中nand全称为“not and”,代表与非门。nand flash是一种基于快速擦除和编程的闪存技术,具有高密度、低成本和快速读写的特点。存储密度通常比其他闪存技术更高,可以容纳更多的数据。此外,相对于传统的机械硬盘,nand flash具有更快的读写速度和更低的功耗。这使得nand flash在许多应用中成为首选的存储解决方案,如移动设备、嵌入式系统和数据中心等。

2、随着信号速率不断提升和负载nand闪存芯片数量的增加,互连链路的非理想效应日益显著,主要表现在多负载的情况下,由于分支和负载芯片的影响,容性负载效应不可避免,容性效应会降低信号传输路径的有效特征阻抗,导致信号路径阻抗的不连续,进而造成信号的幅值在正常电平上下震荡,振铃的出现,可能会引起电路的时序问题或误触发,增加了高速多负载互连设计的风险。

3、以上不足,有待改进。

技术实现思路

1、为了解决现有技术中nand闪存菊花链拓扑结构中容性效应会降低信号传输路径的有效特征阻抗,导致信号路径阻抗的不连续,进而造成信号的幅值在正常电平上下震荡,振铃的出现,可能会引起电路的时序问题或误触发,增加了高速多负载互连设计的风险的问题,本实用新型提供一种改善主干阻抗连续性的nand闪存菊花链拓扑结构。

2、本实用新型技术方案如下所述:

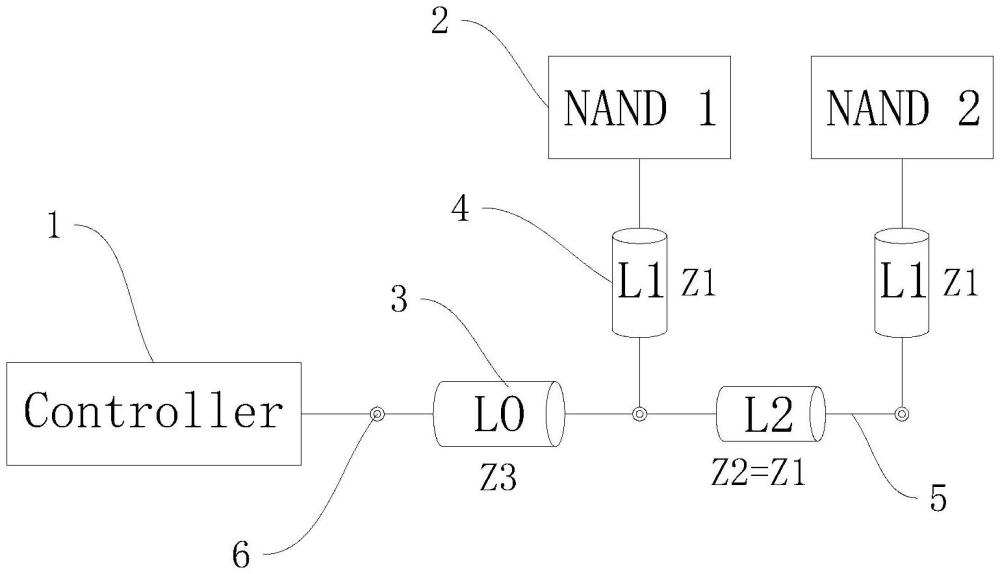

3、一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,包括设置在电路板表层的主控芯片、多个nand闪存芯片以及设置在电路板内部的用于连接所述主控芯片和各个所述nand闪存芯片的线路,所述线路包括与所述主控芯片连接的主干线路,与所述nand闪存芯片连接的分支线路,所述分支线路之间的副线路,所述主干线路另一端与相邻所述分支线路和所述副线路连接;所述主干线路的特征阻抗小于所述分支线路特征阻抗,且所述主干线路的特征阻抗小于所述副线路特征阻抗。

4、上述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,所述主控芯片通过过孔与所述主干线路连接。

5、上述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,所述主干线路与相邻所述分支线路之间、所述主干线路与相邻所述副线路之间均通过过孔连接。

6、上述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,所述分支线路与所述副线路通过过孔连接。

7、上述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,各个所述分支线路的特征阻抗相等。

8、进一步,所述分支线路的特征阻抗与所述副线路的特征阻抗相等。

9、进一步,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.6至0.8倍。

10、进一步,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.8倍。

11、进一步,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.7倍。

12、进一步,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.6倍。

13、根据上述方案的本实用新型,其有益效果在于,本实用新型通过减小主干线路的特征阻抗,即在层叠确定的前提下,增加主干线路的线宽,使信号路径的阻抗趋于一致,从而改善容性负载造成的信号路径阻抗不连续,提高信号路径的阻抗连续性,从而减少信号的振铃。

技术特征:1.一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,包括设置在电路板表层的主控芯片、多个nand闪存芯片以及设置在电路板内部的用于连接所述主控芯片和各个所述nand闪存芯片的线路,所述线路包括与所述主控芯片连接的主干线路,与所述nand闪存芯片连接的分支线路,所述分支线路之间的副线路,所述主干线路另一端与相邻所述分支线路和所述副线路连接;

2.根据权利要求1中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主控芯片通过过孔与所述主干线路连接。

3.根据权利要求1中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主干线路与相邻所述分支线路之间、所述主干线路与相邻所述副线路之间均通过过孔连接。

4.根据权利要求1中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述分支线路与所述副线路通过过孔连接。

5.根据权利要求1-4中任一项所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,各个所述分支线路的特征阻抗相等。

6.根据权利要求5中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述分支线路的特征阻抗与所述副线路的特征阻抗相等。

7.根据权利要求6中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.6至0.8倍。

8.根据权利要求7中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.8倍。

9.根据权利要求7中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.7倍。

10.根据权利要求7中所述的一种改善主干阻抗连续性的nand闪存菊花链拓扑结构,其特征在于,所述主干线路的特征阻抗等于所述分支线路的特征阻抗的0.6倍。

技术总结本技术公开了一种改善主干阻抗连续性的NAND闪存菊花链拓扑结构,包括设置在电路板表层的主控芯片、多个NAND闪存芯片以及设置在电路板内部的用于连接主控芯片和各个NAND闪存芯片的线路,线路包括与主控芯片连接的主干线路,与NAND闪存芯片连接的分支线路,分支线路之间的副线路,主干线路另一端与相邻分支线路和副线路连接;主干线路的特征阻抗小于分支线路特征阻抗,且主干线路的特征阻抗小于副线路特征阻抗。本技术通过减小主干线路的特征阻抗,即在层叠确定的前提下,增加主干线路的线宽,使信号路径的阻抗趋于一致,从而改善容性负载造成的信号路径阻抗不连续,提高信号路径的阻抗连续性,从而减少信号的振铃。技术研发人员:姜杰,吴均受保护的技术使用者:深圳市一博科技股份有限公司技术研发日:20231109技术公布日:2024/6/11本文地址:https://www.jishuxx.com/zhuanli/20240731/185021.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表