一种存储器、数据读取方法、芯片系统及电子设备与流程

- 国知局

- 2024-07-31 20:00:24

本技术涉及计算机数据存储,尤其涉及一种存储器、数据读取方法、芯片系统及电子设备。

背景技术:

1、存储器中包括存储单元和读取电路,读取电路可用于执行读取数据操作,以获取存储单元中存储的数据的取值。根据存储单元的类型不同,读取数据操作可分为单端读取和双端读取。双端读取为:每个读取电路设置两条读取位线。其中一条读取位线用于获取数据电压,该数据电压的大小用于指示该存储单元中存储数据的取值。另一条位线用于获取参考电压。读取电路通过比较数据电压和参考电压的大小,即可获取存储单元中存储的数据的取值。单端读取为:每个读取电路设置一个读取位线。该读取位线用于输出数据电压。读取电路根据数据电压的电压值的大小,确定存储单元中存储的数据的取值。

2、在实际的应用中,通过数据电压的不同电压值来代表存储单元中存储的数据的取值。在双端读取的实现方式中,对数据电压的不同电压值的识别精度在几十毫伏(mv)。即在双端读取的方式下,数据电压的不同电压值的设置跨度在几十毫伏(mv)到上百毫伏之间,即可实现对数据的不同取值的读取。而在单端读取的实现方式中,对数据电压的不同电压值的识别精度在几伏(v)。即在单端读取的实现方式中,需要在读取位线上施加更大的数据电压。而更大的数据电压会降低存储器的读取速率。

技术实现思路

1、本技术实施例提供一种存储器、数据读取方法、芯片系统及电子设备,提高了基于单端读取的存储器的读取数据时的读取速率。

2、为达到上述目的,本技术的实施例采用如下技术方案:

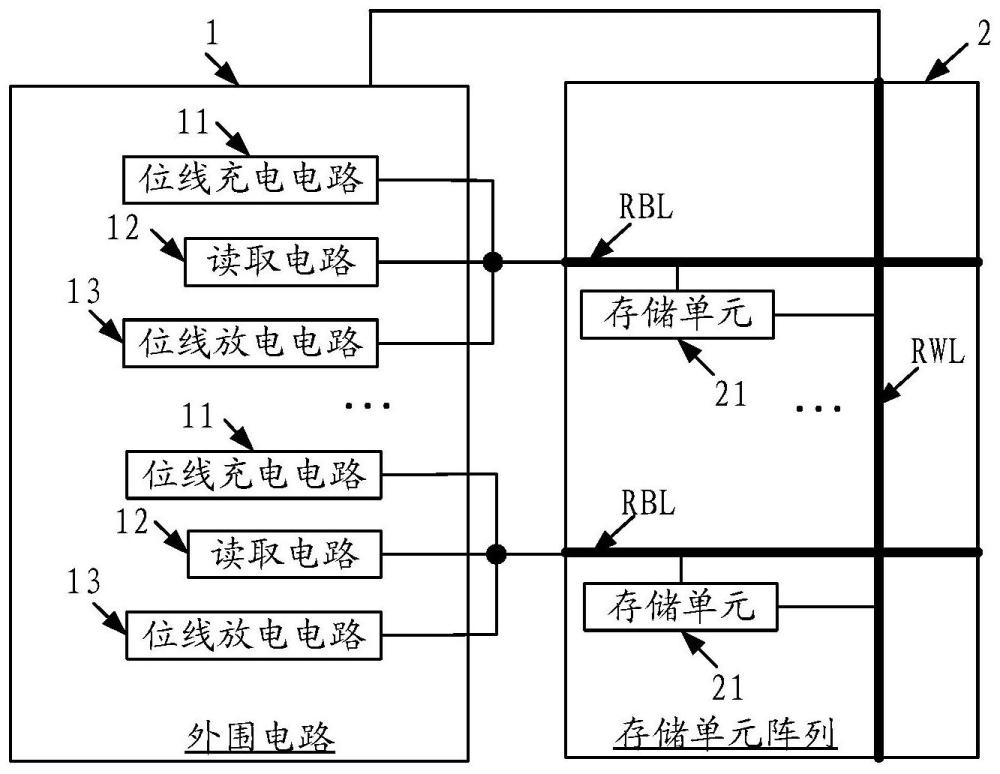

3、第一方面,提供了一种存储器,该存储器包括:存储单元阵列、读取位线、读取电路和位线放电电路;存储单元阵列包括存储单元和;存储单元通过读取位线与读取电路的输入端耦合;位线放电电路包括第一晶体管;第一晶体管的第一极与读取位线耦合;第一晶体管的栅极用于输入第一控制信号;第一控制信号用于控制第一晶体管导通或关断。

4、在本技术实施例中,在对该存储单元进行数据读取时,分为两个阶段:位线预充电阶段和读取存储数据阶段。在位线预充电阶段中,将读取位线的数据电压充电至第一电压值。在读取存储数据阶段,导通存储单元,存储单元中的存储电压的电压值不同,读取位线上的数据电压的电压值也不同。读取电路根据当前读取位线上的数据电压的电压值判断存储单元中的存储电压所指示的数据的取值。而到存储单元中的数据的取值为0时,数据电压需要从第一电压值下降到高低电平的翻转电压以下,读取电路才能判断出存储单元中的数据的取值为0。因第一电压值与高低电平的翻转电压之间的差值较大,需要较长的放电时间,才能使得数据电压下降到高低电平的翻转电压以下。这将导致存储器的读取速率的下降。而在本技术实施例中,将第一晶体管的第二极接地或连接负电压在位线预充电阶段,当数据电压的电压值在第一电压值后,通过控制第一晶体管导通,使得第一晶体管的第一极与第一晶体管的第二极之间导通,进而使得读取位线上的正电荷从第一晶体管的第一极流向第一晶体管的第二极,以实现对读取位线的放电。而通过第一控制信号来控制第一晶体管的导通时长,即可控制放电的时间。通过控制放电的时间长短来使得读取位线上的数据电压的电压值从第一电压值放电到第二电压值。

5、通过位线放电电路将数据电压的电压值放电到第二电压值,该第二电压值大于高低电平的翻转电压。然后在读取存储数据阶段,当存储单元中的数据的取值为0时,数据电压从第二电压值下降到高低电平的翻转电压以下,因第二电压值与高低电平的翻转电压之间的差值较小,使得对该存储单元的读取速度更快,从而提高了该存储器的读取速率。

6、在一种可能的实施方式中,位线放电电路包括第一晶体管、第二晶体管和储能单元;第一晶体管的第一极与读取位线耦合;第一晶体管的第二极与储能单元的第一端耦合;储能单元的第二端与第二晶体管的第一极耦合;第二晶体管的第二极接地或者连接负电压;第一晶体管的栅极用于输入第一控制信号;第二晶体管的栅极用于输入第二控制信号;第一控制信号用于控制第一晶体管导通或关断,第二控制信号用于控制第二晶体管导通或关断。

7、在本技术实施例中,通过储能单元存储读取位线上的正电荷,以将读取位线上的数据电压的电压值从第一电压值放电到第二电压值。此时,通过第一控制信号来导通第一晶体管,使得读取位线和储能单元之间导通,储能单元对读取位线上的正电荷进行存储。当储能单元存储到最大存储量时,不再对读取位线上的正电荷进行存储。通过控制储能单元的最大存储量,即可控制对读取位线的放电量。而在不需要对读取位线进行放电时,将第一晶体管关断。当存储单元内存储的正电荷达到最大存储量时,可以通过第二控制信号来导通第二晶体管,通过导通的第二晶体管对储能单元内存储的正电荷进行释放,从而清空储能单元的电荷存储空间,以便于下一周期内,储能单元可以正常对读取位线上的正电荷进行存储。

8、在一种可能的实施方式中,储能单元包括金属线耦合电容;第一晶体管的第二极与金属线耦合电容的第一极耦合;金属线耦合电容的第二极与第二晶体管的第一极耦合。

9、在本技术实施例中,通过第一晶体管的第二极和第二晶体管之间的金属线构成金属线耦合电容,以金属线的耦合电容的电容值作为单次放电的最大电荷存储量。

10、在一种可能的实施方式中,金属线耦合电容包括第一缠绕金属线和第二缠绕金属线;第一缠绕金属线为金属线耦合电容的第一极,第二缠绕金属线为金属线耦合电容的第二极;第一缠绕金属线的总长度和第二缠绕金属线的总长度分别与读取位线上耦合的存储单元的数量对应。

11、在本技术实施例中,两个互相绝缘的金属板或者金属线即可构成电容。在本技术实施例中,通过第一缠绕金属线和第二缠绕金属线分别构成金属线耦合电容的两极,即可构成金属线耦合电容。在具体的应用中,单条读取位线上耦合的存储单元的数量不同,则读取位线上的负载大小也不同。在电路设计阶段,根据读取位线的负载大小,设计相应电容值的金属线耦合电容。而当金属线耦合电容包括第一缠绕金属线和第二缠绕金属线时,可以通过控制每段缠绕金属线的电容值,以及控制第一缠绕金属线的总长度和第二缠绕金属线的总长度,来实现对金属线耦合电容的电容值的调整。例如,将每段金属线耦合电容中的缠绕金属线的数量设置为与单条读取位线的存储单元的数量相对应。

12、在一种可能的实施方式中,存储器还包括金属层;第一缠绕金属线和第二缠绕金属线设置在金属层中。

13、在本技术实施例中,在芯片制造工艺中,一般可分为前道工艺(front end ofline,feol)和后道工艺(back end of line,beol)。在前道工艺中,通过前道掩膜(mask)在晶圆(wafer)上进行刻蚀等加工操作,生成晶体管等构成的基础电路,如上述实施例中的位线充电电路、读取电路、位线放电电路、存储单元阵列等。然后再在后道工艺中,通过后道掩膜(mask)在生成的基础电路上刻蚀出多个金属层,通过不同的金属层上牵引出金属走线,以完成集成电路的内部与内部,和/或,内部与外部之间的电气连接。在设计的后道掩膜(mask)中,可能包括多个金属层,但是只有多个金属层中的部分金属层用于进行上述电气连接,我们可以将用于连接的金属层定义为连接金属层。而一些金属层可能处于空余状态。我们将这些处于空余状态的金属层定义为空余金属层。以一个存储器的设计版图中包括四层金属层为例,其中第一层和第二层的金属层用于实现电气连接,而第三层的空余金属层和第四层的空余金属层则未用于进行电气连接。此时,可以在第三层和/或第四层的空余金属层上,位于各个存储单元的上方的位置对应设置各段缠绕金属线,并将这些缠绕金属线连接后耦合至第一晶体管和第二晶体管作为金属线耦合电容。在本技术实施例中,若在前道工艺beol中设置金属线耦合电容,因金属线耦合电容需要具有一定的电容值,则需要大量的金属线进行缠绕,才能得到具备该电容值的耦合电容,这将占用芯片大量的布局面积,导致存储器的实际的芯片面积增加。故通过在位于存储单元上方的空余金属层上设置缠绕金属线,无需额外设计缠绕金属线的布局面积,可以节约存储器的芯片面积,使得存储器的芯片布局更紧凑。第一缠绕金属线和第二缠绕金属线可根据在金属层中的不同设置方式,构成金属-绝缘体-金属(metal-insulator-metal,mim)电容,或者,构成金属-氧化物-金属(metal-oxide-metal,mom)电容。

14、在一种可能的实施方式中,储能单元还包括至少一个可调电容组;一个可调电容组包括第三晶体管和第一电容;第三晶体管的第一极与金属线耦合电容耦合;第三晶体管的第二极与第一电容耦合。

15、在本技术实施例中,在实际的应用中,因生产工艺等的差异,不同读取位线的负载大小等可能存在差异。故通过生产制造的金属线耦合电容进行放电时,金属线耦合电容的电容值大小不一定可以适应将所有的读取位线的数据电压都降到第二电压值,通过上文实施例可知,第二电压值需要满足大于高低电平的翻转电压,才能保证不会对读取存储数据阶段造成干扰。故若金属线耦合电容的电容值设置的较大,根据该较大的电容值设计缠绕金属线等,然后进行生产制造。那么对于存储单元阵列中的多个读取位线而言,通过金属线耦合电容放电后,数据电压的电压值可能较高低电平的翻转电压而言较低,也可能接近于高低电平的翻转电压但仍然大于高低电平的翻转电压,也可能低于高低电平的翻转电压。而放电后的数据电压的电压值大于高低电平的翻转电压的情况下,不同的电压差带来的影响是对接下来的读取存储数据阶段中放电速度的不一致。但在放电后的数据电压的电压值等于或小于高低电平的翻转电压的情况下,在后续读取存储数据阶段所读取到的数据存在不可靠性。基于这种情况,可以将金属线耦合电容的电容值设置得比理想值稍小一些(理想值为满足所有读取位线刚好使得放电后的第二电压值刚好略大于高低电平的翻转电压的理论值),以确保经过金属线耦合电容放电后,所有读取位线的电压值都大于高低电平的翻转电压。而后,根据每条读取位线实际的负载大小,可以控制每条读取位线上的至少一个可调电容组中的第三晶体管导通或关断,以实现对每条读取位线所对应的位线放电电路的放电量的适应性调整。

16、可选地,第三晶体管的第一极可以耦合在金属线耦合电容的输入端,也可以耦合在金属线耦合电容的输出端,也可以耦合在金属线耦合电容的中间金属线上。

17、在本技术实施例中,在位线预充电阶段,当需要通过位线放电电路对读取位线进行放电时,导通第一晶体管并关断第二晶体管。对于某一可调电容组,当导通对应的第三晶体管时:如果第三晶体管的第一极耦合在金属线耦合电容的输入端,第三晶体管的第一极耦合在金属线耦合电容的输入端时,金属线耦合电容与第一电容之间并联,可以通过导通后的第一晶体管,同时将读取位线上的正电荷存储到金属线耦合电容和第一电容中。如果第三晶体管的第一极耦合在金属线耦合电容的输出端,第三晶体管的第一极耦合在金属线耦合电容的输出端时,金属线耦合电容和第一电容之间为串联,可以通过导通后的第一晶体管,将读取位线上的正电荷经过金属线耦合电容后传输到第一电容中。如果第三晶体管的第一极耦合在金属线耦合电容的中间金属线上,金属线耦合电容中包括缠绕金属线,第三晶体管的第一极耦合在缠绕金属线之间,在第一晶体管导通且第二晶体管关断时,第一电容与部分缠绕金属线串联并与部分缠绕金属线并联。上述三种方式,均为本技术实施例可能存在的实施方式,对读取位线进行放电使得读取位线上的数据电压的电压值下降到第二电压值。第二电压值的大小由位线放电电路可以存储的电荷量决定。而位线放电电路可以存储的电荷量主要由金属线耦合电容的电容值决定,除此以外,通过导通第三晶体管,可以使得对应的第一可调电容组中第一电容与金属线耦合电容导通,进而实现对位线放电电路可以存储的电荷量的调整。当第三晶体管导通状态或者关断状态固定时,位线放电电路可以存储的电容量是一致的,其大小等于金属线耦合电容的电容值与导通的第三晶体管对应的第一电容的电容值之和。上述三种不同的连接结构下,影响的是位线放电电路存储电荷和释放电荷的速度。在本技术实施例中,根据位线预充电阶段和读取存储数据阶段的周期时长等,可以适应性选择对应的连接结构。

18、在一种可能的实施方式中,位线放电电路还包括开关控制电路;开关控制电路分别与第一晶体管的栅极、第二晶体管的栅极耦合;开关控制电路用于向第一晶体管的栅极输出第一控制信号,向第二晶体管的栅极输出第二控制信号;第一控制信号用于控制第一晶体管导通或关断,第二控制信号用于控制第二晶体管导通或关断。

19、在本技术实施例中,通过开关控制电路分别输出第一控制信号和第二控制信号至第一晶体管的栅极和第二晶体管的栅极,使得第一晶体管和第二晶体管之间交叉导通。在这种交叉导通的情况下,通过第一控制信号导通第一晶体管,并通过第二控制信号关断第二晶体管,读取位线上的正电荷流入位线放电电路中。此时第二晶体管为关断状态,不会将位线放电电路所存储的正电荷进行释放,以保证位线放电电路的存储量可以刚好将数据电压的电压值下降到第二电压值的。而在放电结束后,通过第一控制信号控制第一晶体管关断,并通过第二控制信号控制第二晶体管导通。此时,通过第二晶体管对位线放电电路进行持续放电,以确保位线放电电路中存储的正电荷释放完全,进而确保在后续的放电过程中,位线放电电路有足够的存储量继续存储读取位线上的正电荷。

20、在一种可能的实施方式中,开关控制电路包括与非门和第一反相器;第一反相器的输出端分别与与非门的第一输入端、第二晶体管的栅极耦合,第一反相器的输出端用于输出第二控制信号;与非门的第二输入端用于输入使能信号;与非门的输出端与第一晶体管的栅极耦合;与非门的输出端用于输出第一控制信号。

21、在本技术实施例中,若第一晶体管和第二晶体管采用同种类型的晶体管(例如同样为p型金属-氧化物-半导体晶体管,或者,同样为n型金属-氧化物-半导体晶体管等),则可以将第一控制信号和第二控制信号设置为相反电平,以实现第一晶体管和第二晶体管之间为交叉耦合。通过包括与非门和第一反相器的开关控制电路,可以实现输出的第一控制信号和第二控制信号恒定为相反电平的控制信号。

22、在一种可能的实施方式中,存储器还包括输出缓冲电路;输出缓冲电路的输入端与读取电路的输出端耦合;输出缓冲电路用于周期性锁存读取电路输出的数据。

23、在本技术实施例中,通过输出缓冲电路对读取电路输出的数据进行锁存缓冲。这样可以实现周期性从输出缓冲电路获取读取电路所输出的数据,避免读取电路输出的数据没有时间性和区分性等,造成读取错乱等。

24、在一种可能的实施方式中,输出缓冲电路包括第一充电电路、高电平保持电路和锁存器;锁存器的输入端为输出缓冲电路的输入端,锁存器的输入端与读取电路的输出端耦合;第一充电电路的输出端、高电平保持电路的保持端分别与锁存器的输入端耦合;第一充电电路用于向读取电路的输出端输出为高电平的电压。

25、在本技术实施例中,在位线预充电阶段,通过第一充电电路输出充电电压,使得第六晶体管的第一极和锁存器的第一极为高电平。当第六晶体管导通时,将第一充电电路输出的充电电压流入第六晶体管的第二极,以拉低第六晶体管的第一极的电压。当第六晶体管关断时,通过高电平保持电路使得第六晶体管的第一极始终保持高电平,锁存器的输入端输入高电平,对该高电平进行锁存缓冲后,再输出进行输出。

26、在一种可能的实施方式中,锁存器包括时钟控制电路和锁存电路;时钟控制电路包括级联的两个第四反相器;锁存电路包括级联的三个第五反相器;第一级的第五反相器的输入端作为锁存器的输入端;第三级的第五反相器的输出端作为锁存器的输出端;第一级的第四反相器的输出端与第一级的第五反相器的第一电压端和第三级的第五反相器的第一电压端耦合;第二级的第四反相器的输出端还与第一级的第五反相器的第二电压端和第三级的第五反相器的第二电压端耦合。

27、在本技术实施例中,通过时钟控制电路控制第一级的第五反相器和第三级的器不工作,以实现将输入的电平信号锁存在第二级的第五反相器中。并通过时钟控制电路控制第一级的第五反相器和第三级的第五反相器工作,以实现将锁存在第二级的第五反相器中的电平信号输出。时钟控制电路通过两个级联的第四反相器,实现第一级的第四反相器的输出信号与第二级的第四反相器的输出信号之间的电平始终相反。通过输入第一级的第四反相器输入的电平不同,可以控制第一级的第五反相器和第三级的第五反相器工作或者不工作。

28、在一种可能的实施方式中,输出缓冲电路还包括第二反相器;第二反相器的输入端与锁存器的输出端耦合。

29、在本技术实施例中,通过第二反相器对输出缓冲电路输出的数据进行反相。

30、在一种可能的实施方式中,读取电路包括第三反相器和第六晶体管;第三反相器的输入端为读取电路的输入端,且第三反相器的输入端与读取位线耦合;第三反相器的输出端与第六晶体管的栅极耦合;第六晶体管的第二极接地或者连接负电压;第六晶体管的第一极为读取电路的输出端。

31、在本技术实施例中,以第六晶体管为nmos晶体管为例。在读取存储阶段,通过第三反相器获取读取位线上的数据电压的电压值,当该电压值高于高低电平的翻转电压时,第三反相器输出低电平至第六晶体管(nmos晶体管)的栅极,以控制第六晶体管关断。当该电压值低于高低电平的翻转电压时,第三反相器输出高电平至第六晶体管(nmos晶体管)的栅极,以控制第六晶体管导通。通过第六晶体管的第二极连接接地电压或负电压,使得在第六晶体管导通和关断的情况下,第六晶体管的第一极的电压值不同,以第六晶体管的第一极的电压值来指示存储单元中的数据的取值。例如,第六晶体管的第一极为高电平时,指示存储单元中的数据的取值为1;第六晶体管的第一极为低电平时,指示存储单元中的数据的取值为0。

32、在一种可能的实施方式中,存储器还包括状态保持器,状态保持器还包括至少一个第五晶体管;至少一个第五晶体管与第四晶体管的第一极耦合,且至少一个第五晶体管与第四晶体管串联。

33、在本技术实施例中,在读取存储数据阶段,读取位线可能会存在浮空(floating)信号,造成对读取数据的干扰。通过第三反相器的输出端与第四晶体管的栅极耦合,第三反相器的输出端输出低电平时,第四晶体管导通,通过第四晶体管向数据位线输入一定值的保持电流,以防止浮空信号的产生。第四晶体管输入的电流的电流值需要设置的比较小,一般要小于第三反相器可以进行识别读取的程度,以避免对第三反相器造成读取数据的干扰。

34、在一种可能的实施方式中,状态保持器还包括至少一个第五晶体管;至少一个第五晶体管与第四晶体管的第一极耦合,且至少一个第五晶体管与第四晶体管串联。

35、在本技术实施例中,第五晶体管的数量可以为一个或多个,第五晶体管与第四晶体管串联。控制第五晶体管始终导通。通过设置第五晶体管可以增加状态保持器的稳定性等。

36、在一种可能的实施方式中,存储器还包括位线充电电路;位线充电电路与读取位线耦合。

37、在本技术实施例中,在位线预充电阶段,通过位线充电电路对读取位线进行充电,以使得读取位线上的数据电压的电压值为第一电压值。

38、在一些可能的实施方式中,位线充电电路包括第七晶体管。第七晶体管的第一极用于输入充电电压,第七晶体管的第二极与读取位线耦合。第七晶体管的栅极用于输入第一充电控制信号,第一充电控制信号用于控制第七晶体管导通,以向读取位线充电。

39、在本技术实施例中,通过第七晶体管的第一极输入充电电压。当第一控制信号控制第七晶体管导通后,充电电压从第七晶体管的第一极导通至第七晶体管的第二极,并从第七晶体管的第二极输出至读取位线,从而实现对读取位线的充电。

40、示例性地,将充电电压的电压值设置为第一电压值,则可实现通过充电电压将读取位线上的数据电压的电压值充电至第一电压值。

41、在一些可能的实施方式中,存储单元阵列中的所有存储单元均为单端读取型存储单元。

42、在本技术实施例中,当存储单元阵列中的所有存储单元都为单端读取型存储单元时,为每一个存储单元所耦合的读取字线都对应设置上述实施例所记载的读取电路、位线充电电路和位线放电电路。

43、在一些可能的实施方式中,存储单元阵列中的一部分存储单元为单端读取型存储单元,另一部分存储单元为双端读取型存储单元。

44、在本技术实施例中,在与单端读取型存储单元耦合的读取位线上设置上述实施例中所记载的读取电路、位线放电电路和位线充电电路。通过该位线放电电路,对对应的读取位线进行放电,从而提高单端读取型存储单元的读取速率,以提高存储器的读取速率。

45、在一些可能的实施方式中,当存储单元为双端读取型存储单元时,该存储单元可以为包括六个晶体管的存储单元。

46、示例性地,当存储单元为双端读取型存储单元时,存储单元阵列包括存储单元、字线、位线。每条位线包括第一位线和第二位线。六个晶体管分别为第一导通晶体管、第二导通晶体管、第一存储晶体管、第二存储晶体管、第三存储晶体管、第四存储晶体管。第一存储晶体管和第三存储晶体管为pmos晶体管。第一导通晶体管、第二导通晶体管、第二存储晶体管、第四存储晶体管为nmos晶体管。读取电路包括读出放大器。其中:第一导通晶体管的第一极与第一位线耦合。第一导通晶体管的第二极分别与第一存储晶体管的第二极、第二存储晶体管的第一极、第三存储晶体管的栅极和第四存储晶体管的栅极耦合至第一存储点。第一导通晶体管的栅极与字线耦合。第二导通晶体管的第一极与第二位线耦合。第二导通晶体管的第二极分别与第三存储晶体管的第二极、第四存储晶体管的第一极、第一存储晶体管的栅极和第二存储晶体管的栅极耦合至第二存储点。第二导通晶体管的栅极与字线耦合。第一位线和第二位线都与位线充电电路和读出放大器耦合。

47、在本技术实施例中,第一存储点的存储电压所指示的取值,与第二存储点的存储电压所指示的取值为相反的两个取值。且以第一存储点的存储电压所指示的取值作为该存储单元21中所存储的数据的取值。该包括六个晶体管的双端读取型存储单元,读取数据的具体操作为:

48、一、位线预充电阶段:不对字线进行充电,以使得第一导通晶体管(nmos晶体管)和第二导通晶体管(nmos晶体管)受低电平而关断。然后通过位线充电电路对第一位线和第二位线进行预充电,使得在第一导通晶体管(nmos晶体管)和第二导通晶体管(nmos晶体管)关断的情况下,第一位线上的数据电压和第二位线上的数据电压的电压值为第一电压值。

49、二、读取存储数据阶段:对字线进行充电,以使得第一导通晶体管(nmos晶体管)和第二导通晶体管(nmos晶体管)受高电平而导通。读出放大器通过比较此时第一位线上的数据电压和第二位线上的数据电压的大小,来确定第一存储点的存储电压所指示的取值,进而以确定该存储单元所存储的数据的取值,具体确定方式为:若第一存储点处的存储电压对应的数据的取值为1,第二存储点处的存储电压对应的取值为0,则第一存储点处的存储电压高于第二存储点处的存储电压。因为第二存储点处的存储电压低于第一电压值,所以会拉低第二位线处的数据电压,进而导致第二位线上的数据电压低于第一位线上的数据电压。此时读出放大器比较第一位线上的数据电压和第二位线上的数据电压的电压值大小。第一位线上的数据电压的电压值大于第二位线上的数据电压的电压值。则可以确定第一位线对应的第一存储点处的存储电压对应的数据的取值为1(即存储单元中的数据的取值为1)。若第一存储点处的存储电压对应的数据的取值为0,第二存储点处的存储电压对应的取值为1,则第一存储点处的存储电压低于第二存储点处的存储电压。因为第一存储点处的存储电压低于第一电压值,所以会拉低第一位线处的数据电压,进而导致第一位线上的数据电压低于第二位线上的数据电压。此时读出放大器比较第一位线上的数据电压和第二位线上的数据电压的电压值大小。第一位线上的数据电压的电压值小于第二位线上的数据电压的电压值。则可以确定第一位线对应的第一存储点处的存储电压对应的数据的取值为0(即存储单元中的数据的取值为0)。

50、在一些可能的实施方式中,当存储单元为单端读取型存储单元时,该存储单元可以为包括八个晶体管的存储单元,或者,为包括一个晶体管的存储单元。

51、示例性地,当存储单元为包括八个晶体管的存储单元时。每条字线包括写入字线(write wordline,wwl)、读取字线(read wordline,rwl)。每条位线包括第一写入位线、第二写入位线、读取位线。八个晶体管分别为第一导通晶体管、第二导通晶体管、第三导通晶体管、第四导通晶体管、第一存储晶体管、第二存储晶体管、第三存储晶体管、第四存储晶体管。第一存储晶体管和第三存储晶体管为pmos晶体管。第一导通晶体管、第二导通晶体管、第三导通晶体管、第四导通晶体管、第二存储晶体管、第四存储晶体管为nmos晶体管。读取电路包括第三反相器和第六晶体管。其中:

52、第一导通晶体管的第一极与第一写入位线耦合。第一导通晶体管的第二极分别与第一存储晶体管的第二极、第二存储晶体管的第一极、第三存储晶体管的栅极和第四存储晶体管的栅极耦合至第一存储点。第一导通晶体管的栅极与写入字线耦合。第二导通晶体管的第一极与第二写入位线耦合。第二导通晶体管的第二极分别与第三存储晶体管的第二极、第四存储晶体管的第一极、第一存储晶体管的栅极和第二存储晶体管的栅极耦合至第二存储点。第二导通晶体管的栅极与写入字线耦合。第三导通晶体管的栅极与第二存储点耦合。第三导通晶体管的第二极接地或者连接负电压。第三导通晶体管的第一极与第四导通晶体管的第二极耦合。第四导通晶体管的栅极与读取字线耦合。第四导通晶体管的第一极与读取位线耦合。位线充电电路、位线放电电路和第三反相器的输入端都与读取位线耦合。第三反相器的输出端与第六晶体管的栅极耦合。

53、在本技术实施例中,采用了单端读取型存储单元,其读取数据的操作为:

54、一、位线预充电阶段:不对读取字线进行充电,以使得第四导通晶体管(nmos晶体管)受低电平而关断。然后通过位线充电电路对读取位线进行预充电,使得在第四导通晶体管关断的情况下,读取位线上的数据电压的电压值为第一电压值。

55、二、位线放电阶段:通过位线放电电路对读取位线进行放电,使得读取位线的数据电压的电压值等于第二电压值。

56、三、存储单元导通阶段:对读取字线进行充电,以导通第四导通晶体管(nmos晶体管)。使得存储单元与读取位线之间导通。

57、四、读取存储数据阶段:根据第二存储点处的存储电压的电压值确定是否导通第三导通晶体管。根据第三晶体管导通与否,读取位线上的数据电压呈现出不同的电压值。然后第三反相器根据读取位线上的数据电压的电压值确定存储单元中的数据的取值。具体确定方式为:

58、当第一存储点处的存储电压对应的数据的取值为0,第二存储点处的存储电压对应的取值为1时。第二存储点处的存储电压为高电平,使得第三导通晶体管(nmos晶体管)导通。则导通的第三导通晶体管和导通的第四导通晶体管使得第三导通晶体管的第二极与读取位线之间导通,第三导通晶体管的第二极处的接地电压或负电压会拉低读取位线上的数据电压,使得数据电压的电压值低于高低电平的翻转电压。高低电平的翻转电压为第三反相器的工作点,对于电压值高于高低电平的翻转电压的电压,第三反相器判断其为高电平的电压;反之,对于电压值低于高低电平的翻转电压的电压,第三反相器判断其为低电平的电压。读取电路采用第三反相器对读取位线上的数据电压进行读取,此时的数据电压低于高低电平的翻转电压,第三反相器输入的是低电平,则第三反相器向第六晶体管(nmos晶体管)的栅极输出高电平,第六晶体管导通,第六晶体管的第二极的接地电压或负电压将第六晶体管的第一极的电压拉低为低电平,此时第六晶体管的第一极处的电压值的取值为0,用于指示第一存储点的存储电压对应的数据的取值为0(即存储单元中的数据的取值为0)。

59、当第一存储点处的存储电压对应的数据的取值为1,第二存储点处的存储电压对应的取值为0时。第二存储点处的存储电压为低电平,使得第三导通晶体管(nmos晶体管)关断。因第三导通晶体管关断,使得第三导通晶体管的第二极与读取位线之间也关断,读取位线上的数据电压为第二电压值到第一电压值之间。第三反相器对读取位线上的数据电压进行读取,此时的数据电压的电压值高于高低电平的翻转电压,第三反相器输入的是高电平,则第三反相器向第六晶体管(nmos晶体管)的栅极输出低电平,第六晶体管关断。第六晶体管的第一极的电压保持为高电平状态,此时第六晶体管的第一极处的电压值的取值为1,用于指示第一存储点的存储电压对应的数据的取值为1(即存储单元中的数据的取值为1)。

60、在本技术实施例中,当存储单元为单端读取型存储单元时,读取电路采用第三反相器对读取位线上的数据电压进行读取。第二存储点处的存储电压的电压值不同,存在导通第三导通晶体管,或者,关断第三导通晶体管,两种情况。两种情况下读取位线上的数据电压的电压值不同,根据数据电压的电压值得到第二存储点处的存储电压所指示的数据的取值。因第一存储点处的存储电压所指示的数据的取值和第二存储点处的存储电压所指示的取值为相反取值。在本技术实施例中,可以将第二存储点处的数据的取值作为存储单元中存储的数据的取值。也可以将第一存储点处的数据的取值作为存储单元中存储的数据的取值,并根据第二存储点处的数据的取值得到第一存储点处的数据的取值。

61、第二方面,本技术实施例还提出了一种数据读取方法,应用于存储器;该存储器包括存储单元阵列、读取位线和位线放电电路;存储单元阵列包括存储单元;存储单元和位线放电电路分别与读取位线耦合;该方法包括:控制位线放电电路将读取位线上的数据电压的电压值从第一电压值放电到第二电压值;第二电压值大于读值比较电压;导通存储单元和读取位线;根据数据电压的电压值得到存储单元中的数据;当数据电压的电压值大于读值比较电压时,判断存储单元中的数据的取值为第一取值;当数据电压的电压值小于读值比较电压时,判断存储单元中的数据的取值为第二取值。

62、示例性地,第一取值可以为1,第二取值可以为0。

63、在一种可能的实施方式中,上述控制位线放电电路将读取位线上的数据电压的电压值从第一电压值放电到第二电压值,包括:控制位线放电电路的放电时间,将读取位线上的数据电压的电压值从第一电压值放电到第二电压值。

64、在一种可能的实施方式中,上述控制位线放电电路将读取位线上的数据电压的电压值从第一电压值放电到第二电压值,包括:控制位线放电电路的放电量,将读取位线上的数据电压的电压值从第一电压值放电到第二电压值。

65、在一种可能的实施方式中,上述位线放电电路包括金属线耦合电容;控制位线放电电路的放电量,将读取位线上的数据电压的电压值从第一电压值放电到第二电压值,包括:控制位线放电电路与读取位线导通,将读取位线上的数据电压的电压值从第一电压值放电到第二电压值。

66、在一种可能的实施方式中,上述位线放电电路还包括至少一个第一电容;该方法还包括:根据第一电压差和/或第一数量控制每个第一电容是否与金属线耦合电容导通,以调整位线放电电路的放电量;第一电压差为第一电压值与读值比较电压之差;第一数量为单条读取位线上所耦合的存储单元的数量。

67、在一种可能的实施方式中,该方法还包括:通过第一控制信号控制位线放电电路是否存储读取位线上的电荷;通过第二控制信号控制位线放电电路是否释放位线放电电路中存储的电荷。

68、在一种可能的实施方式中,该方法还包括:在根据数据电压的电压值得到存储单元中的数据的取值后,对得到的存储单元中的数据进行锁存后输出。

69、第三方面,本技术实施例还提出了一种芯片系统,该芯片系统包括处理器和如上述第一方面所记载的存储器;处理器用于向存储器中写入数据、读取存储器中存储的数据,或者,刷新存储器中存储的数据。

70、第四方面,本技术实施例还提出了一种电子设备,该电子设备包括如上述第三方面所记载的芯片系统和电路板,该芯片系统设置在电路板上。

71、关于上述第二方面、第三方面和第四方面的技术效果的描述,可参考上述第一方面的相关描述,在此不再赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184994.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种防碰撞硬盘的制作方法

下一篇

返回列表