基于动态忆阻器的权重资格迹更新方法和神经网络芯片

- 国知局

- 2024-07-31 20:00:23

本发明涉及深度学习硬件,尤其是涉及基于动态忆阻器的权重资格迹更新方法和神经网络芯片。

背景技术:

1、脉冲神经网络(snn)被称为第三代人工神经网络,由于其高度仿生性而具有能耗、时序信号处理能力方面的优势。为了提高snn与实际生物大脑皮层工作机制的一致性,片上学习功能的实现具有重要意义。在snn的片上训练方法中,基于脉冲突触时间可塑性(stdp)机制的方法表现出最良好的硬件可行性。与基于反向传播等算法的方案来说,stdp进行神经网络的片上训练带来的计算资源消耗较小,同时具有更高的生物可解释性。然而由于stdp本身数学特性存在对指数运算的需求,低功耗的硬件实现方案仍然较为稀缺。

2、文献“ieee transactions on circuits and systems i:regular papers”(joob,han jw,kong b s.2022,69(9):3632-3642.)利用cmos技术实现资格迹记录模块的技术,但晶体管工作于亚阈值区,在可靠性方面较为不足;同时电路结构复杂、面积开销大。

3、文献“ieee international symposium on circuits and systems(iscas)”(y.et al.,2021.pp.1-5)基于相变存储器(pcm)短时程特性实现利用迹的突触可塑性的工作。该方案在对pcm进行短时程调控时需要施加一组多个连续的脉冲,以利用pcm的漂移特性达到实现短时程可塑性的目的。但连续多脉冲的调制方案具有相对更高的能耗,且更难调整参数以适配不同的任务情景。

技术实现思路

1、本发明的目的就是为了克服上述现有技术存在的缺陷而提供一种基于动态忆阻器的权重资格迹更新方法和神经网络芯片,降低权重资格迹的片上运算与存储的硬件开销和计算延时。

2、本发明的目的可以通过以下技术方案来实现:

3、一种基于动态忆阻器的权重资格迹更新方法,用于更新采用脉冲突触时间可塑性机制进行脉冲神经网络片上训练中的权重资格迹,所述方法包括以下步骤:

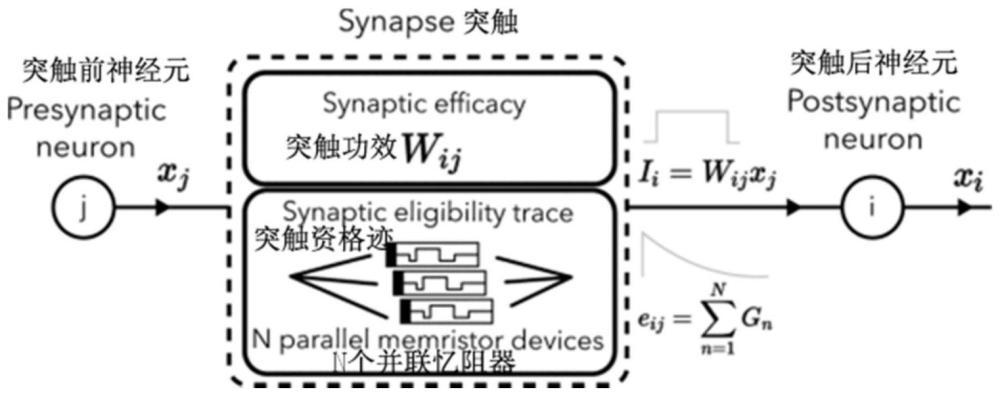

4、基于动态忆阻器构建突触结构,在突触结构前后分别设置突触前神经元和突触后神经元,并设置前迹存储器件和后迹存储器件,分别用于记录突触结构前的脉冲活动变化和突触结构后的脉冲活动变化;

5、进行权重资格迹更新时,分别在突触前神经元和突触后神经元的脉冲发放时刻,对后迹存储器件和前迹存储器件进行采样,获取后迹累加量和前迹累加量,后迹累加量减去前迹累加量即为权重资格迹的改变量。

6、进一步地,所述动态忆阻器为被施加电学激励信号后,降低电阻;失去电学激励信号后,电阻将随时间自发恢复至原本的阻态的器件。

7、进一步地,所述动态忆阻器为扩散型的离子忆阻器、电荷俘获忆阻器、基于铁电转变的短时程铁电忆阻器或离子晶体管。

8、进一步地,所述动态忆阻器包括上电极、功能层和下电极,所述上电极和下电极分别设置在功能层的上下两侧,构成三明治形结构。

9、进一步地,所述方法还包括设置控制电路,该控制电路用于在突触前神经元发放脉冲的时刻,访问后迹存储器件,并进行取值采样,获取后迹累加量;在突触后神经元发放脉冲的时刻,访问前迹存储器件,并进行取值采样,获取前迹累加量。

10、本发明还提供一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,包括神经元电路、突触电路和控制电路,所述突触电路连接在两个神经元电路之间,用于将神经元电路的输出脉冲转换为电流或电压信号,并传递给另一个神经元电路,所述突触电路包括动态忆阻器、前迹存储器件和后迹存储器件,所述前迹存储器件和后迹存储器件分别连接在动态忆阻器的前后两端,分别用于记录突触结构前的脉冲活动变化和突触结构后的脉冲活动变化;

11、所述控制电路在突触电路前的神经元电路发放脉冲的时刻,访问后迹存储器件,并进行取值采样,获取后迹累加量;在突触电路后的神经元电路发放脉冲的时刻,访问前迹存储器件,并进行取值采样,获取前迹累加量,将后迹累加量减去前迹累加量作为权重资格迹的改变量。

12、进一步地,所述动态忆阻器为被施加电学激励信号后,降低电阻;失去电学激励信号后,电阻将随时间自发恢复至原本的阻态的器件。

13、进一步地,所述动态忆阻器为扩散型的离子忆阻器、电荷俘获忆阻器、基于铁电转变的短时程铁电忆阻器或离子晶体管。

14、进一步地,所述动态忆阻器包括上电极、功能层和下电极,所述上电极和下电极分别设置在功能层的上下两侧,构成三明治形结构。

15、进一步地,所述突触电路包括一个或多个相互并联的动态忆阻器,各个动态忆阻器的前后两端均分别对应设有前迹存储器件和后迹存储器件。

16、与现有技术相比,本发明具有以下优点:

17、(1)本发明提出基于动态忆阻器实现权重资格迹并利用其实现脉冲时序依赖可塑性(stdp)学习机制的脉冲神经网络芯片,相比于其他stdp的硬件实现方案,本发明利用了忆阻器本征的短时程动力学特性,降低了权重资格迹的片上运算与存储的硬件开销和计算延时。

18、(2)本发明提出通过在突触前神经元和突触后神经元的脉冲发放时刻,对动态忆阻器的后迹和前迹进行采样,获取后迹累加量和前迹累加量,后迹累加量减去前迹累加量即为权重资格迹的改变量,即通过计算迹的采样进行权重更新,与stdp的标准形式中计算脉冲对时间差的指数进行权重更新的方法具有相同的数学意义,能在实现stdp学习机制的同时,利用了忆阻器本征的短时程动力学特性,降低权重资格迹的片上运算与存储的硬件开销和计算延时。

技术特征:1.一种基于动态忆阻器的权重资格迹更新方法,用于更新采用脉冲突触时间可塑性机制进行脉冲神经网络片上训练中的权重资格迹,其特征在于,所述方法包括以下步骤:

2.根据权利要求1所述的一种基于动态忆阻器的权重资格迹更新方法,其特征在于,所述动态忆阻器为被施加电学激励信号后,降低电阻;失去电学激励信号后,电阻将随时间自发恢复至原本的阻态的器件。

3.根据权利要求1所述的一种基于动态忆阻器的权重资格迹更新方法,其特征在于,所述动态忆阻器为扩散型的离子忆阻器、电荷俘获忆阻器、基于铁电转变的短时程铁电忆阻器或离子晶体管。

4.根据权利要求1所述的一种基于动态忆阻器的权重资格迹更新方法,其特征在于,所述动态忆阻器包括上电极、功能层和下电极,所述上电极和下电极分别设置在功能层的上下两侧,构成三明治形结构。

5.根据权利要求1所述的一种基于动态忆阻器的权重资格迹更新方法,其特征在于,所述方法还包括设置控制电路,该控制电路用于在突触前神经元发放脉冲的时刻,访问后迹存储器件,并进行取值采样,获取后迹累加量;在突触后神经元发放脉冲的时刻,访问前迹存储器件,并进行取值采样,获取前迹累加量。

6.一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,包括神经元电路、突触电路和控制电路,所述突触电路连接在两个神经元电路之间,用于将神经元电路的输出脉冲转换为电流或电压信号,并传递给另一个神经元电路,其特征在于,所述突触电路包括动态忆阻器、前迹存储器件和后迹存储器件,所述前迹存储器件和后迹存储器件分别连接在动态忆阻器的前后两端,分别用于记录突触结构前的脉冲活动变化和突触结构后的脉冲活动变化;

7.根据权利要求6所述的一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,其特征在于,所述动态忆阻器为被施加电学激励信号后,降低电阻;失去电学激励信号后,电阻将随时间自发恢复至原本的阻态的器件。

8.根据权利要求6所述的一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,其特征在于,所述动态忆阻器为扩散型的离子忆阻器、电荷俘获忆阻器、基于铁电转变的短时程铁电忆阻器或离子晶体管。

9.根据权利要求6所述的一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,其特征在于,所述动态忆阻器包括上电极、功能层和下电极,所述上电极和下电极分别设置在功能层的上下两侧,构成三明治形结构。

10.根据权利要求6所述的一种基于脉冲突触时间可塑性机制的脉冲神经网络芯片,其特征在于,所述突触电路包括一个或多个相互并联的动态忆阻器,各个动态忆阻器的前后两端均分别对应设有前迹存储器件和后迹存储器件。

技术总结本发明涉及一种基于动态忆阻器的权重资格迹更新方法和神经网络芯片,用于更新采用脉冲突触时间可塑性机制进行脉冲神经网络片上训练中的权重资格迹,方法包括:基于动态忆阻器构建突触结构,在突触结构前后分别设置突触前神经元和突触后神经元,并设置前迹存储器件和后迹存储器件,分别用于记录突触结构前的脉冲活动变化和突触结构后的脉冲活动变化;进行权重资格迹更新时,分别在突触前神经元和突触后神经元的脉冲发放时刻,对后迹存储器件和前迹存储器件进行采样,获取后迹累加量和前迹累加量,后迹累加量减去前迹累加量即为权重资格迹的改变量。与现有技术相比,本发明降低了权重资格迹的片上运算与存储的硬件开销和计算延时。技术研发人员:张续猛,梁晋豪,刘琦,刘明受保护的技术使用者:复旦大学技术研发日:技术公布日:2024/6/11本文地址:https://www.jishuxx.com/zhuanli/20240731/184991.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表