基于超前补偿型跨阻放大器的光电存算阵列读出电路

- 国知局

- 2024-07-31 19:59:06

本发明涉及基于超前补偿型跨阻放大器的光电存算阵列读出电路,属于集成电路领域。

背景技术:

1、众所周知,早期的计算机是由各种门电路组成的,这些门电路通过组装出一个固定的电路板来执行一个特定的程序。一旦需要修改程序功能,就要重新组装电路板,所以早期的计算机程序都是固化在硬件电路上,不利于程序开发。为了实现硬件设计与程序设计的分离,出现了冯诺依曼结构,该结构中计算单元与存储单元分离,大大推动了计算机产业发展,但是随着当前大计算场景的出现,每次计算时将数据从存储单元搬运至计算单元,计算完成后再将数据写回存储单元,这就导致了极大的数据搬运功耗,而存算一体技术的出现则很好的解决了计算时数据搬运的问题。存算一体将运算从计算单元转入存储单元中进行,也就是在存储资源中嵌入计算能力,因而不需要在计算前后往复搬运数据,避免了数据在频繁传输过程中带来的延迟和功耗问题。比如专利cn111208865a公开了一种基于光电计算单元的存算一体技术,相对于其他现有的存算一体技术方案,该技术具有工艺兼容性好,单器件存储位宽高等优势,利于超大规模集成。

2、现有的存算一体方案中,相较于数字域累加,模拟域累加的运算方法推理速度快,具备高能效比的优势。专利cn116029351a提出了一种权重电流镜运算电路与权重电容运算电路相结合的模拟域累加读出电路,以两个高增益高带宽的运算放大器分别实现电流的拷贝和将电流转换成电压的线性处理,有效避免了较高比特位电容与较高比特位电流镜的设计,利用两种结构的优势互补实现了多比特位激励下的模拟域累加;与现有的模拟域累加电路相比,具有高精度、小面积的优势。然而,对于高线性度的模拟域读出,主要的功耗开销来源于高增益高带宽的运算放大器,该专利所提出的方案中电流拷贝电路与电流-电压转换电路共存在两个高增益高带宽运算放大器,造成了较高的功耗开销,存在进一步降低的空间。而且随着神经网络的发展,网络规模越来越大,能效比的提高对于实现网络加速越来越重要。

技术实现思路

1、为了解决现有的光电计算单元系统在神经网络加速中存在的问题,本发明提供了一种基于超前补偿型跨阻放大器的光电存算阵列读出电路,使用单一高增益高带宽放大器,针对光电存算阵列负载的阻容电路进行超前补偿,在确保稳定性的前提下兼备电流拷贝和电流电压转换两个功能,减少了模拟域累加读出电路中高增益高带宽放大器的数目,从而降低功耗开销,且其计算方法仍能有效避免较高比特位电容与较高比特位电流镜的设计;与现有的模拟域累加电路相比,在保持了高精度、小面积的基础上,进一步降低功耗,满足了基于光电存算单元的高能效比的神经网络加速需求。

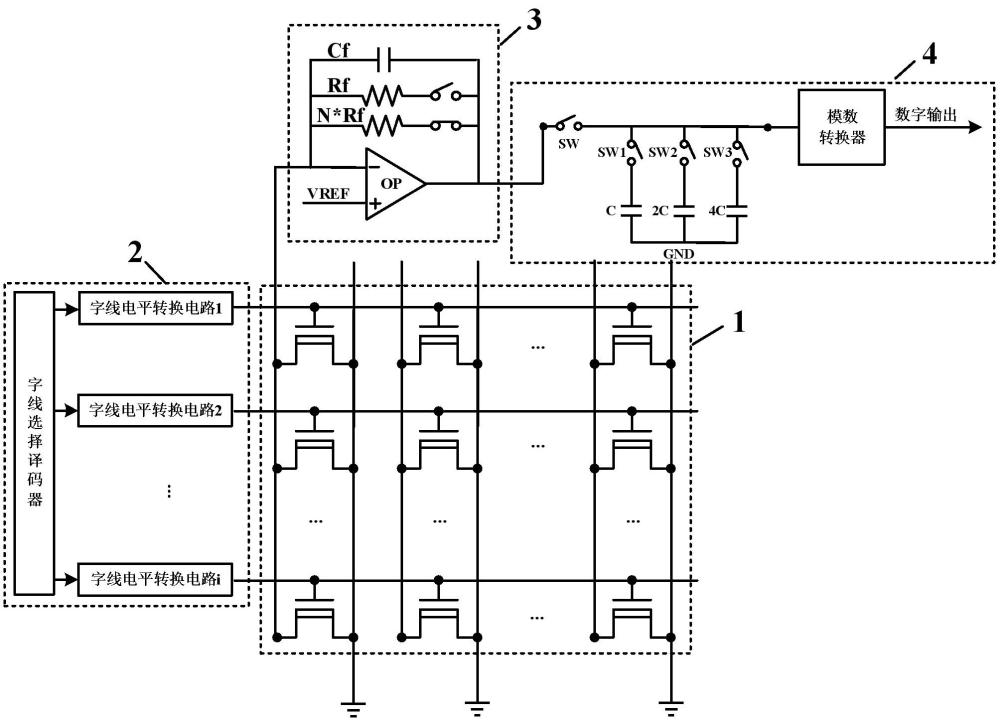

2、本发明的第一个目的在于提供一种基于超前补偿型跨阻放大器的光电存算阵列读出电路,该电路包括:由多个光电存算单元构成的晶体管阵列、字线驱动电路、超前补偿型跨阻放大器和后处理电路;所述晶体管阵列中,同行的所有光电存算单元对应的晶体管的栅极相连构成字线,与所述字线驱动电路输出端相连;同列的所有光电存算单元对应的晶体管的源极相连构成源线,源线接地;同列的所有光电存算单元对应的晶体管的漏极相连并与所述超前补偿型跨阻放大器输入端相连;所述超前补偿型跨阻放大器输出端与所述后处理电路相连。

3、可选的,所述超前补偿型跨阻放大器包括由运算放大器构成的前馈电路以及双档位运算电阻与超前补偿电容并联构成的反馈电路;所述超前补偿型跨阻放大器用于利用所述双档位反馈电阻实现对电流的r倍或n*r倍的权重乘法运算,n为大于1的整数。

4、可选的,所述双档位反馈电阻的阻值分别为rf和n*rf;超前补偿电容的容值为cf,记前馈电路中运算放大器的小信号传输函数为h(s),那么系统小信号环路增益loop gain的传输函数为:

5、

6、对于高带宽的前馈放大器h(s),反馈电路运算电阻rf(kω级)、阻容电路中的负载电阻rs(mω级)与负载电容cs(pf级)形成低频极点,时间常数为,达到微秒量级,恶化了系统稳定性;而本技术超前补偿型跨阻放大器中rf、cf构成的并联反馈电路形成低频零点,提供信号快速通路,针对光电存算阵列列方向负载的低频阻容电路进行超前补偿,设置cf≈cs,使该零点对应时间常数达到微秒量级,实现零点与极点基本互相抵消(零点-极点的相对大小关系与rf档位基本无关),在满足高带宽的同时保证稳定性,从而实现单一高性能放大器兼具电流拷贝与电流-电压转换功能,降低系统功耗。

7、可选的,超前补偿电容为mom电容,典型值为2pf,双档位运算电阻为多晶硅电阻,典型值为32kω。

8、可选的,所述运算放大器采用cmos差分放大器,所述cmos差分放大器的正输入端接参考电平vref,负输入端与同列的所有光电存算单元对应的晶体管的漏极相接,输出端接后处理电路;同时输出端通过双档位运算电阻与超前补偿电容并联构成的反馈电路连接到运算放大器的负输入端。

9、所述超前补偿型跨阻放大器,利用双档位反馈电阻实现对电流的r倍或n*r倍的权重乘法运算;若输入数字激励为低比特位,则为r倍乘法运算,若输入数字激励为高比特位,则为n*r倍(n为整数且n大于1)乘法运算,其中r为单位电阻阻值。

10、可选的,所述后处理电路包括模拟域移位累加电路和模数转换电路;其中,所述模拟域移位累加电路包括m个按比特位配置容值的权重电容,用于通过电荷共享实现电压按比特位累加运算;所述权重电容的容值分别为20c、21c、……、2m-1c,m为大于1的整数。

11、可选的,c为单位电容容值,典型值为50ff。

12、可选的,所述模数转换电路为逐次逼近型模数转换器、单斜率模数转换器或者逐次逼近型与单斜率混合结构模数转换器,以实现模拟电压信号和数字信号的转换。

13、可选的,最佳的n和m满足。

14、可选的,所述字线驱动电路包括字线选择译码器和字线电平转换电路;所述字线选择译码器的输入端与字线地址信号相连,其输出端与所述字线电平转换电路的输入端一一对应相连;所述字线电平转换电路的输出端作为所述字线驱动电路的输出端且与所述晶体管阵列的字线一一对应相连,用于神经网络加速中光电存算单元栅极的激励信号输入,方式是按比特位进行数字输入。

15、可选的,所述超前补偿电容为mom电容,所述双档位运算电阻为多晶硅电阻。

16、本技术的第二个目的在于提供一种存算一体电路,该存算一体电路采用上述基于超前补偿型跨阻放大器的光电存算阵列读出电路实现电流的读出。

17、本技术的第三个目的在于提供一种存算一体装置,含有上述基于超前补偿型跨阻放大器的光电存算阵列读出电路或者上述存算一体电路。

18、本发明有益效果是:

19、本发明提供的基于超前补偿型跨阻放大器的光电存算阵列读出电路,在读出模式中,对于单列光电存算单元在多比特激励下计算得到的多个模拟电流,通过设计高增益高带宽的超前补偿型跨阻放大器,实现对光电存算阵列的负载阻容电路的稳定性补偿,在确保稳定性的前提下兼备电流拷贝和电流电压转换两个功能,节省了读出电路中的高性能放大器的使用,减少了读出电路的功耗开销,且其计算方法仍能有效避免较高比特位电容与较高比特位电流镜的设计;与现有的模拟域累加电路相比,在保持了高精度、小面积的基础上,进一步降低功耗,满足了基于光电存算单元的高精度、高能效比、小面积的神经网络加速需求。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184882.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种数据存储柜的制作方法

下一篇

返回列表