一种RRAM的故障测试方法

- 国知局

- 2024-07-31 19:58:54

本发明属于集成电路领域,具体是涉及一种rram的故障测试方法。

背景技术:

1、阻变随机存储器(rram)是一种新兴的存储器技术,其与主流的存储器技术动态随机存储存储器(dram)和闪存(flash)相竞争。rram与主流存储技术的区别在于,数据是根据电阻而不是电荷来存储的,这意味着rram不会受到与电荷存储相关的缩放限制;此外,rram是一种非易失性存储器(nvm),具有高内存密度、低功耗、与标准互补金属氧化物半导体(cmos)工艺的后端线(beol)兼容等优点,在存储技术、内存计算、逻辑系统等各个领域得到了广泛的应用,因此rram有望在未来取代传统存储器。然而,它的纳米级制造过程引入了不确定性,导致发生故障和随后的读取误差。

2、有研究表明常规存储器的故障同样会出现在rram上,而且rram还存在与常规存储器不同的特殊故障。目前,主流的算法并不能有效检测rram的特殊故障,如专利申请cn112750486a公开了一种阻变存储器的故障测试方法,专利申请cn114171100a公开了一种高故障覆盖率的阻变存储器的测试方法,其均仅使用简单的读写操作来检测sa0,sa1,tf0,tf1,r1d等常规存储器故障,故障覆盖率并不高;专利申请cn116343886a公开了一种基于存储器内建自测试的可配置march 算法,其设计了一种可配置的march算法,尽管该算法可以有效降低测试时间,但是该算法针对的主要是sram与dram,也没有考虑rram的特殊故障;因此rram的特殊故障也难以被检测。

技术实现思路

1、为解决上述技术问题,本发明提供了一种rram的故障测试方法,针对rram的特殊故障设计了改进的测试算法,构建适用于rram的mbist电路,能够有效检测rram特殊故障,同时还可检测一些常规存储器的故障,有效提高rram的故障覆盖率。

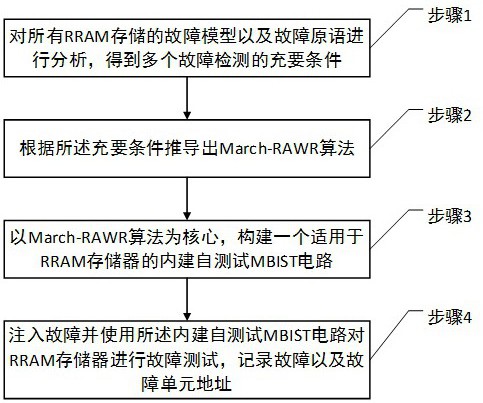

2、本发明所述的一种rram的故障测试方法,包括以下步骤:

3、步骤1、对rram故障模型的故障原语进行分析,针对每个故障模型推导出所需要的测试序列;

4、步骤2、根据需要的测试序列推导出march-rawr测试算法;

5、步骤3、根据march-rawr算法,构建适用于rram的mbist电路;

6、步骤4、对rram注入故障并使用mbist电路对rram进行故障检测,测试完成后输出故障单元的地址信息。

7、进一步的,所述rram故障模型包含rram特殊故障以及常规故障,所述rram特殊故障包括deep故障、usf故障、cfud故障和dcfud故障;所述常规故障包括静态单单元故障、静态双单元故障、动态单单元故障、动态双单元故障。

8、进一步的,rram根据电阻大小不同共有五种状态,即deep1、logic 1、usf、logic0、deep0;对于处于未定义态的rram,设置两个处在usf状态边界的电阻rref1和rref0分别对应rref1和rref0读操作的参考电阻,rref0>rref1,用于检测rram的usf状态;处于logic 0和logic1状态的rram电阻为r0和r1, 将r0和r1操作对应的参考电阻rr大小设置为(r0+r1)/2,可以有效区分0状态和1状态,用于常规故障的检测;

9、对于一个会发生usf故障的rram单元,假设它从0状态转换成1状态时,因为故障落入了usf状态,此时rram单元的电阻值大于rref1;当进行rref1读操作时,可检测出此时的rram单元处于非1状态,与预期的1状态不符,从而检测出rram发生故障。

10、进一步的,所述march-rawr测试算法,具体描述为:{m1↑↓ (w0); m2↑ (rref0 w0r0n r0 w1 r1 w1 rref1); m3↑ (rref1 w1 r1n r1 w0 r0 w0 rref0); m4↓ (rref0 w0 r0 r0w1 r1 w1 r1); m5↓ (rref1 w1 r1 r1 w0 r0 w0 r0); m6↑↓ (r0)};

11、其中,m1-m6为元素,↑代表地址升序,↓代表地址降序,↑↓代表地址可以升序也可以降序,w0代表对选中的存储单元写入0数据,w1代表对选中的存储单元写入1数据;r0代表对选中的存储单元进行读0操作,此时存储单元期望的数据值为0;r1代表对选中的存储单元进行读1操作,此时存储单元期望的数据值为1;r0n代表对选中的存储单元进行n次连续的读0操作;r1n代表对选中的存储单元进行n次连续的读1操作;rref1,rref0代表用于检测rram特殊故障的读操作。

12、进一步的,所述mbist电路包含:

13、控制生成器:控制整个mbist电路各模块按m1-m6的顺序依次执行march-rawr测试算法;

14、地址生成器:产生march-rawr测试算法所需要的地址信号;

15、数据生成器:产生march-rawr测试算法所需要的数据信号;

16、比较器:比较存储器读取rram的实际数据和预期数据之间的差异,检验存储器的读写值是否正确,若正确,输出信号test_fail为低,故障地址记录器不记录信息;若错误,输出信号test_fail为高,故障地址记录器记录存在故障的存储单元地址;

17、故障地址记录器:用于记录存在故障的存储单元地址,并通过地址信号fail_adr输出具体的故障单元地址。

18、进一步的,所述rram包括外围电路、忆阻器阵列、灵敏放大器和参考电阻;

19、所述外围电路接收mbist电路信号或者外部逻辑信号,通过mux选择器来控制,当bist_en信号为0时,外围电路接收外部逻辑信号,当bist_en信号为1时,外围电路接收mbist电路信号。外围电路接收完信号后进行译码并将输出信号输出给忆阻器阵列;

20、所述灵敏放大器两个输入端,一端接忆阻器阵列的输出信号rinx,x代表选中的存储单元所在的列数;另一端接参考电阻的输出信号rref;正常情况下,灵敏放大器仅有一个固定阻值的参考电阻,为了能检测rram特有故障,本发明设置了三个不同阻值的参考电阻,通过一个四选一数据选择器mux与灵敏放大器相连;四选一数据选择器通过控制使能端选择对应大小的参考电阻;参考电阻从大到小分别为rref0,rr和rref1,当读取操作为rref0时,选择rref0电阻,当读取操作为rref1时,选择rref1电阻,当读取操作为r0和r1时,选择rr电阻。

21、进一步的,故障检测过程为:

22、步骤4-1、给rram存储器注入故障:

23、步骤4-2、mbist电路进入测试模式,依次执行march-rawr算法{m1↑↓ (w0); m2↑(rref0 w0 r0n r0 w1 r1 w1 rref1); m3↑ (rref1 w1 r1n r1 w0 r0 w0 rref0); m4↓ (rref0w0 r0 r0 w1 r1 w1 r1); m5↓ (rref1 w1 r1 r1 w0 r0 w0 r0); m6↑↓ (r0)};

24、步骤4-3、在算法进行读操作时,灵敏放大器将对应rram存储单元存储的信息转换成数字信号并输出至比较器,比较器将实际信号与预期信号进行对比。如果实际结果与预期结果存在不同,则说明rram存储器存在故障;步骤4-4、算法执行结束后,若rram存储器存在故障,比较器的test_fail信号被拉高,同时故障地址记录器会记录下故障单元的地址。

25、本发明所述的有益效果为:本发明所述方法通过分析rram的常规故障模型和特有故障模型,推导出一种能有效覆盖大部分故障模型的march-rawr算法,该算法的时间复杂度为32n+2nn(1≤n≤10)(n代表算法中march元素的个数,n代表连续读的次数),可以覆盖所有的静态单单元故障、静态双单元故障,以及大部分动态单单元故障、动态双单元故障以及rram特殊故障,故障覆盖率高达89.92%;同时,本发明所述方法根据march-rawr算法设计的内建自测试电路与常规的内建自测试电路相比,只在灵敏放大器部分增加了一个四选一数据选择器,就可以根据算法元素选取需要的参考电阻,因此该测试电路可以作为常规内建自测试电路的代替,额外增加的面积很小。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184872.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。