一种基于SRAM的内部存算逻辑电路、阵列和SRAM

- 国知局

- 2024-07-31 20:06:48

本技术涉及微处理器设计领域,特别是涉及一种基于sram的内部存算逻辑电路、阵列和sram。

背景技术:

1、在过去的几十年里,存储和计算分离的冯·诺依曼架构一直是各类处理器设计的主流计算架构范式。然而在该架构下,微处理器增长速度的幂指数要远大于存储器从而导致存储器带宽和处理器之间的速度差异越来越大,进而成为该架构下的一个瓶颈“存储墙”。同时,数据从处理器到存储器之间的数据移动还会带来严重的能耗问题,进而造成该架构下的另一个瓶颈“功耗墙”。

2、现如今,静态随机存取存储器(static random-access memory,sram)以读写速度快,工艺成熟稳定,与先进互补金属氧化物半导体(complementary metal oxidesemiconductor,cmos)工艺兼容且能够大规模生产等优势,被工业界和学术界作为片内存内计算的可靠介质广泛研究。sram本身不具备计算能力,但是在外围增加大量的外围电路即可支持sram具有计算能力,同时提高sram的灵活度。将该sram应用于冯·诺依曼架构中可以有效缓解“存储墙”和“功耗墙”的问题。但是在sram外围增加大量的外围电路的过程中,增加了设计成本以及铺设面积,同时通过外围电路提高的sram的灵活度和计算能力有限。

3、鉴于上述技术,寻求一种基于sram的内部存算逻辑电路是本领域技术人员亟待解决的问题。

技术实现思路

1、本技术的目的是提供一种基于sram的内部存算逻辑电路、阵列和sram。可以解决现有技术中通过在sram外围增加大量的外围电路使其具有计算能力带来的增加设计成本以及铺设面积的问题。

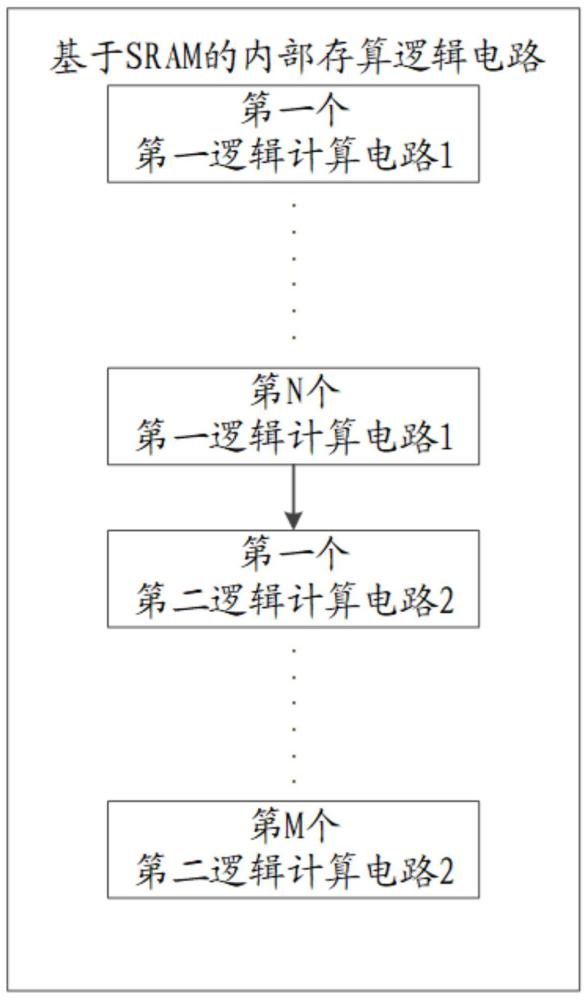

2、为解决上述技术问题,本技术提供一种基于sram的内部存算逻辑电路,包括:n个第一逻辑计算电路和m个第二逻辑计算电路,其中,n和m均为大于零的整数,且n大于m;第一逻辑计算电路包括sram单元电路、用于实现复制运算逻辑和多值运算逻辑的第一晶体管电路和一组计算位线,第二逻辑计算电路包括sram单元电路、第一晶体管电路、用于实现非运算逻辑的第二晶体管电路和一组计算位线;

3、其中,第i组计算位线的第一端与第i-1组计算位线的第二端相连,第i组计算位线的第二端与第i+1组计算位线的第一端相连,i为大于1,小于n+m的整数;

4、第一晶体管电路的第一端和第二端分别与对应的sram单元电路的第一端和第二端相连,第一晶体管电路的第三端和第四端分别与对应的计算位线和对应的sram单元电路的第三端相连,第一晶体管电路的第五端与对应的计算位线相连;

5、第二晶体管电路的第一端和第二端分别与对应的计算位线和对应的sram单元电路的第三端相连,第二晶体管电路的第三端和第四端分别与对应的sram单元电路的第二端和对应的计算位线相连。

6、优选地,第一晶体管电路包括第一晶体管、第二晶体管和第三晶体管;

7、其中,第一晶体管的第一端作为第一晶体管电路的第一端与对应的sram单元电路的第一端相连,第一晶体管的第二端与第一控制端相连,第一晶体管的第三端与第一供电端相连;

8、第二晶体管的第一端与第三晶体管的第一端和第二控制端相连,第二晶体管的第二端作为第一晶体管电路的第二端与对应的sram单元电路的第二端相连,第二晶体管的第三端作为第一晶体管电路的第三端与对应的计算位线相连;

9、第三晶体管的第二端作为第一晶体管电路的第四端与对应的sram单元电路的第三端相连,第三晶体管的第三端作为第一晶体管电路的第五端与对应的计算位线相连。

10、优选地,第二晶体管电路包括第四晶体管和第五晶体管;

11、第四晶体管的第一端与第五晶体管的第一端和第三控制端相连,第四晶体管的第二端作为第二晶体管电路的第一端与对应的计算位线相连,第四晶体管的第二端作为第二晶体管电路的第二端与对应的sram单元电路的第三端相连;

12、第五晶体管的第二端作为第二晶体管电路的第三端与对应的sram单元电路的第二端相连,第五晶体管的第三端作为第二晶体管电路的第四端与对应的计算位线相连。

13、优选地,sram单元电路包括:第六晶体管、第七晶体管、第八体管和第九晶体管;

14、其中,第六晶体管的第一端与第八晶体管的第一端相连,作为sram单元电路的第二端;第七晶体管的第一端和第九晶体管的第一端相连,作为sram单元电路的第三端;

15、第六晶体管的第二端与第七晶体管的第二端和第二供电端相连,第六晶体管的第三端与第八晶体管的第二端相连;

16、第七晶体管的第三端与第九晶体管的第二端相连;

17、第八晶体管的第三端与第九晶体管的第三端相连,作为sram单元电路的第一端。

18、优选地,sram单元电路还包括:第十晶体管和基准连接线;

19、第十晶体管的第一端与基准连接线相连,第十晶体管的第二端与对应的读写位线相连,第十晶体管的第三端与第六晶体管的第一端和第八晶体管的第一端相连。

20、优选地,sram单元电路还包括:第十一晶体管;

21、第十一晶体管的第一端与第十晶体管的第一端和基准连接线相连,第十一晶体管的第二端与对应的读写位线相连,第十一晶体管的第三端与第七晶体管的第一端和第九晶体管的第一端相连。

22、为解决上述技术问题,本技术还提供一种sram内部存算逻辑阵列,包括f个上述的基于sram的内部存算逻辑电路;f为大于零的整数;

23、其中,各基于sram的内部存算逻辑电路中的第一组读写位线的第一端均相连,作为sram内部存算逻辑阵列的第一端;

24、各基于sram的内部存算逻辑电路中的最后一组读写位线的第二端均相连,作为sram内部存算逻辑阵列的第二端;

25、各基于sram的内部存算逻辑电路中的基准连接线与对应的各基于sram的内部存算逻辑电路中的基准连接线相连。

26、为解决上述技术问题,本技术还提供一种sram,包括e个上述的sram内部存算逻辑阵列,e为大于零的整数;

27、其中,各sram内部存算逻辑阵列的第一端相连,作为sram的输入端,各sram内部存算逻辑阵列的第二端相连,作为sram的输出端。

28、本技术所提供的基于sram的内部存算逻辑电路,包括:n个第一逻辑计算电路和m个第二逻辑计算电路,其中,n和m均为大于零的整数,且n大于m;第一逻辑计算电路包括sram单元电路、用于实现复制运算逻辑和多值运算逻辑的第一晶体管电路和一组计算位线,第二逻辑计算电路包括sram单元电路、第一晶体管电路、用于实现非运算逻辑的第二晶体管电路和一组计算位线;其中,第i组计算位线的第一端与第i-1组计算位线的第二端相连,第i组计算位线的第二端与第i+1组计算位线的第一端相连,i为大于1,小于n+m的整数;第一晶体管电路的第一端和第二端分别与对应的sram单元电路的第一端和第二端相连,第一晶体管电路的第三端和第四端分别与对应的所述计算位线和对应的sram单元电路的第三端相连,第一晶体管电路的第五端与对应的计算位线相连;第二晶体管电路的第一端和第二端分别与对应的计算位线和对应的sram单元电路的第三端相连,第二晶体管电路的第三端和第四端分别与对应的sram单元电路的第二端和对应的计算位线相连。可见,本技术中,修改了sram内部的单元电路,增加了使其具有实现复制运算逻辑、多值运算逻辑和非运算逻辑的第一晶体管电路和第二晶体管电路,使其sram内部单元电路具有计算能力,不需要额外连接外接电路。同时,本技术中采用第一逻辑计算电路和第二逻辑计算电路结合的方法构建sram的内部存算逻辑电路,进一步降低了sram设计的成本以及面积铺设的问题。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185273.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。